《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK

大家在写程序的时候,可能会听闻,什么独热码,什么格雷码,什么二进制码等等,本节意在解释这几种编码之间的区别和优势以及用verilog怎么去实现,下面先介绍这几种编码的区别。

1 基础理论部分

1.1 独热码

独热码,在英文文献中称做 one-hot code, 直观来说就是有多少个状态就有多少比特,而且只有一个比特为1,其他全为0的一种码制。

如,有十六个状态的独热码状态编码应该是:0000000000000001,0000000000000010,0000000000000100,0000000000001000,0000000000010000,0000000000100000 ,……,10000000000000000。但是通常我们为了方便书写,将二进制简化为十六进制表示(从右往左每四位二进制位用一位十六进制数表示),那么,以上十六状态的独热码可以表示成0x0001, 0x0002, 0x0004, 0x0008, 0x0010, 0x0020, ……, 0x8000。

1.2 格雷码

在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。

1.3 二进制码

二进制代码:由两个基本字符'0'、'1'组成的代码。其中,码元:"一位"二进制代码。码字:N个码元可以组成的不同组合,任意一个组合称一个码字。

1.4 二进制编和格雷码利弊

二进制编码、格雷码编码使用最少的触发器,消耗较多的组合逻辑,而独热码编码反之。独热码编码的最大优势在于状态比较时仅仅需要比较一个位,从而一定程度上简化了译码逻辑。虽然在需要表示同样的状态数时,独热编码占用较多的位,也就是消耗较多的触发器,但这些额外触发器占用的面积可与译码电路省下来的面积相抵消。

由于CPLD更多地提供组合逻辑资源,而FPGA更多地提供触发器资源,所以CPLD多使用gray-code,而FPGA多使用one-hot编码。另一方面,对于小型设计使用gray-code和binary编码更有效,而大型状态机使用one-hot更高效。

关于独热码,我们在使用状态机的时候,会详细解释。为了更进一步说明二进制码和格雷码之间的关系,可以查看下图12.1。

方法一:

图12.1 二进制码与独热码

上述的方法可以称为递归法,从0~7的高位都是0,后8~15的高位都是1,那么由二进制怎么去实现格雷码,如下图12.2所示。

方法二:适合于编程实现

图12.2 计算格式

也即对原位进行移位,然后和原位进行求抑或操作。

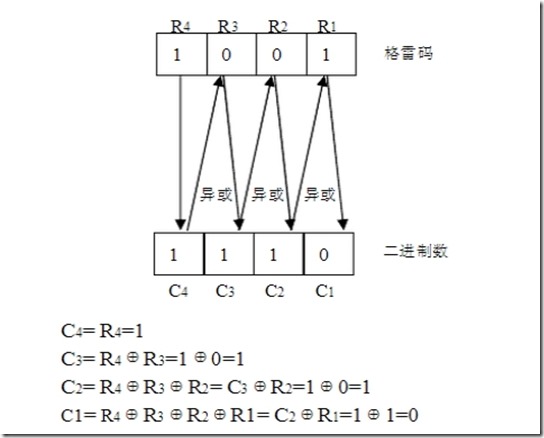

那么格雷码怎么去实现二进制呢?且看下图12.3解释:

图12.3

由上图可以分析得出,最高位是保持不变的,然后以后每一位都要和前几位进行求异或操作。下面我们就用verilog来实现。

2 Verilog代码实现部分

2.1 二进制转格雷码

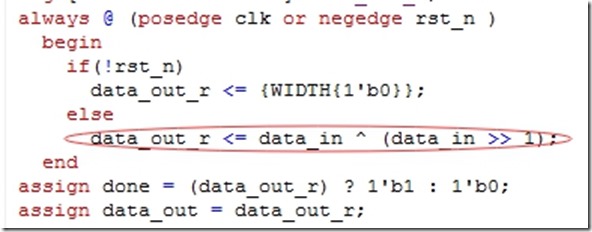

讲解最重要的代码部分,如图12.4

图12.4 代码实现部分

最重要的代码一行搞定。请大家看懂。

2.2 格雷码转二进制

让大家感受一下FPGA的并行的魅力,重要代码如图12.5所示,利用FPGA的并行加速,可以实现其他CPU不能比拟的速度。

图12.5 转换实现部分

3 Modelsim仿真部分

部分重要代码如图12.6所示

图12.6 仿真程序

将输入数据封装成一个任务,然后在initial中直接调用任务即可,但要注意,data_init为输入数据的初始化,一定要放在task_reset复位信号的前面,这一点不容忽视。

图12.7为binary2gray仿真的波形。

图12.7 仿真波形

关于板级仿真,大家可以去利用四位LED或者数码管去实现,这里不再赘述。

图12.8为testbench代码部分,gray2binary

图12.8 代码实现部分

图12.9为gray2binary仿真的波形

图12.9 仿真波形

《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK的更多相关文章

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

1基础理论部分 1.1分频 分频,是的,这个概念也很重要.分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频.实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

- 《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷

1基础理论部分 VGA(video graphics array)即视频图形阵列,是IBM在1987年随PS/2一起推出的使用模拟信号的一种视频传输标准.VGA相比与现在的视频传输接口来说已经过时,不 ...

- 《FPGA全程进阶---实战演练》第四章之Quartus II使用技巧

技巧1:“新”技能 hierarchies警告寻找 在编译之后,警告中“hierarchies”这个单词大家估计都很熟悉了,一看到这个警告,基本上就是例化时出现的问题.一般例化时,要是哪个连线没引出, ...

- 《FPGA全程进阶---实战演练》第二十一章 电源常用类型:LDO和 DCDC

高速电路中的电源设计 高速电路中的电源设计大概分为两种,一种是集总式架构,一种是分布式架构.集总式架构就是由一个电源输入,然后生成多种所需要的电压.如图1所示.这种架构会增加多个DC/DC模块,这样成 ...

- 《FPGA全程进阶---实战演练》第七章 让按键恢复平静

1基础理论部分 A:“怎么按键按下去之后,结果不正常?”,B:“按键你消抖了吗?”A:“消什么抖,还要消抖?”, B:“先检测按键变化,然后消抖过滤波动信号,最后输出稳定信号”,A:“我好像漏掉了什 ...

- 《FPGA全程进阶---实战演练》第二十一章之 几种常用电平分析及特性

TTL,CMOS以及LVTTL,LVCMOS TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本.TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大, ...

- 《FPGA全程进阶---实战演练》第三章之PCB叠层

1.双面板 在双层板设计layout时,最好不要不成梳状结构,因为这样构成的电路,回路面积较大,但是只要对较重要的信号加以地保护,布线完成之后将空的地方敷上地铜皮,并在多个过孔将两个地连接起来,可以弥 ...

随机推荐

- js函数调用二种常用方法的例子

js中函数调用的两种常用方法. 一个js函数 function test(aa){ window.alert("你输入的是"+aa); } 方法一:直接调用 test(" ...

- [svc]为何linux ext4文件系统目录默认大小是4k?

linux ext4普通盘为什么目录大小是4k? Why does every directory have a size 4096 bytes (4 K)? To understand this, ...

- 菜鸟学Java(八)——dom4j详解之读取XML文件

dom4j是一个Java的XML API,类似于jdom,用来读写XML文件的.dom4j是一个非常非常优秀的Java XML API,具有性能优异.功能强大和极端易用使用的特点,同时它也是一个开放源 ...

- Java 虚拟机:互斥同步、锁优化及synchronized和volatile

互斥同步 互斥同步(Mutual Exclusion & Synchronization)是常见的一种并发正确性保证手段.同步是指子啊多个线程并发访问共享数据时,保证共享数据在同一时刻只能被一 ...

- IBM研究院找到度量安全性方法:容器与虚拟机,谁更安全?

https://zhuanlan.zhihu.com/p/40446759 虚拟机比容器更安全吗?你可能会有自己的答案,但IBM研究院发现容器的安全性与虚拟机一样,甚至更加安全. 一般来说,从接口宽度 ...

- [Windows Azure] Virtual Machine and Cloud Service Sizes for Windows Azure

Virtual machine size CPU cores Memory OS disk space–cloud services OS disk space–virtual machines Ma ...

- 【ActiveMQ】Spring Jms集成ActiveMQ学习记录

Spring Jms集成ActiveMQ学习记录. 引入依赖包 无论生产者还是消费者均引入这些包: <properties> <spring.version>3.0.5.REL ...

- Delphi下IOCP开源框架:DIOCP 成功应用案例分享

首先说明,该项目不是本人的项目,本文转自盒子. 该项目使用的DIOCP版本为1.0,目前diocp为3.5 以下是盒子的原文 ------------------------------------- ...

- python celery 多work多队列

1.Celery模块调用 既然celery是一个分布式的任务调度模块,那么celery是如何和分布式挂钩呢,celery可以支持多台不通的计算机执行不同的任务或者相同的任务. 如果要说celery的分 ...

- jQuery之自定义pagination控件

slpagination 效果: slpagination.js (function($) { $.fn.slpagination = function(options, params) { if ( ...