FPGA小白学习之路(4)PLL中的locked信号解析(转)

ALTPLL中的areset,locked的使用

转自:http://www.360doc.com/content/13/0509/20/9072830_284220258.shtml

今天对PLL中areset和locked详细查了下资料,发现网上这方面的资料很少,所以自己认真读了下Documentation---ug_altpll.pdf,现在我将我学到的内容总结如下:

areset简而言之就是高电平有效,对pll进行复位。

下面我们主要来认识一下locked信号:

Locked这个输出到底是干嘛用的呢,pdf中这样写道:

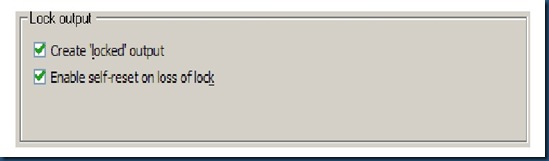

The ALTPLL megafunction allows you to monitor the PLL locking process using a lock signal named locked and also allows you to set the PLL to self-reset on loss of lock.

原来这Locked信号是用来观察pll输出时钟是否和输入时钟锁定。当锁定时,这个Locked信号就变为高电平。

但pdf中又这么写道:

The locked signal might toggle as the PLL begins tracking the reference clock. To avoid such a false lock indication, use a gated lock signal.

当这个pll刚开始跟踪输入时钟时这个Locked信号又可能会发生跳转,为了避免这种错误的指示,我们就使用gated lock信号。这个gated lock信号其实和locked信号是同一个,locked信号多了个计数功能后就叫做gated lock了。

You must specify the number of PLL input clock cycles to hold the locked signal low after the PLL is initialized

就是在pll被初始化之后,让gated lock依旧保持低电平多少个周期,以此来解决下面图片中的问题:

这图片中locked在pll开始跟踪输入时钟的时候一直在抖动,而gated lock因为设置了上面周期后,开始阶段始终为low,直到到达counter值后变为高电平,这就避免了locked的抖动。所以gated lock信号更加稳定。

这个时钟周期怎么算呢,如下:

To calculate the number of clock cycles needed, you must know the maximum lock time of the PLL, and the period of the PLL input clock. The lock time of the PLL is listed in the “PLL Timing Specifications” section of the DC & SwitchingCharacteristics chapter of the device handbook. The period of the PLL input clock is user-specified. For example, if the maximum lock time of a PLL is 1ms,and its input clock frequency is 100 MHz which corresponds to a 10 ns clock period, you calculate the value of the gated lock counter, by dividing 1 ms by 10 ns. The result is 100,000 clock cycles. 这个我就不解释了,大家自己看吧,很容易理解的。

不同器件类型对gated lock和self-reset的支持情况不一样

FPGA小白学习之路(4)PLL中的locked信号解析(转)的更多相关文章

- FPGA小白学习之路(1) System Verilog的概念以及与verilog的对比(转)

转自CSDN:http://blog.csdn.net/gtatcs/article/details/8970489 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证 ...

- FPGA小白学习之路(2)error:buffers of the same direction cannot be placed in series

锁相环PLL默认输入前端有个IBUFG单元,在输出端有个BUFG单元,而两个BUFG(IBUFG)不能相连,所以会报这样的错: ERROR:NgdBuild:770 - IBUFG 'u_pll0/c ...

- FPGA小白学习之路(5)clk为什么要用posedge,而不用negedge(转)

clk为什么要用posedge,而不用negedge 转自:http://www.cnblogs.com/dangxia/archive/2012/03/07/2383744.html Verilog ...

- FPGA小白学习之路(6)串口波特率问题的处理

串口波特率问题的处理 此博文一共包含三个方面的内容:(1)异步串口通信的数据格式:(2)为何串口通信中接收端采样时钟频率是传输的波特率的16倍:(3)串口波特率等概念. 1.异步串口通信的数据格式 串 ...

- USB小白学习之路(6) IIC EEPROM读取解析

IIC EEPROM读取解析 1. 编译错误处理(这里可以忽略) 在解压包解压了程序后,直接编译,出现如下错误. *** WARNING L14: INCOMPATIBLE MEMORY MODEL ...

- USB小白学习之路(1) Cypress固件架构解析

Cypress固件架构彻底解析及USB枚举 1. RAM的区别 56pin或者100pin的cy7c68013A,只有内部RAM,不支持外部RAM 128pin的cy7c68013A在pin脚EA=0 ...

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- Qt 学习之路 2(4):信号槽

Home / Qt 学习之路 2 / Qt 学习之路 2(4):信号槽 Qt 学习之路 2(4):信号槽 豆子 2012年8月23日 Qt 学习之路 2 110条评论 信号槽是 Qt 框架引以 ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

随机推荐

- 第04项目:淘淘商城(SpringMVC+Spring+Mybatis)【第九天】(商品详情页面实现)

https://pan.baidu.com/s/1bptYGAb#list/path=%2F&parentPath=%2Fsharelink389619878-229862621083040 ...

- 视觉SLAM算法框架解析(1) PTAM

版权声明:本文为博主原创文章,未经博主允许不得转载. 本系列文章旨在总结主流视觉SLAM算法的框架,对比各个算法在子模块的差异,最终提炼出融合各个算法优点的架构. PTAM[1]是视觉SLAM领域里程 ...

- shell_跳板机推送公钥

#!/bin/bash#push publickey to aap-servers#将局域网内可以ping通的主机ip保存到一个文件> ip_up.txtfor i in {2..10}do { ...

- 深入理解Java接口

一.接口的特点 接口中可以有变量和方法,接口中的变量会隐式的指定为public static final变量(并且只能是public static final变量),而方法会被隐式的指定为public ...

- iOS 类似外卖 两个tableView联动

在伯乐在线上看到一个挺好玩的文章,自己也参考文章实现了一下. 效果实现如图所示: 具体实现的内容可以参考原文,参考文章:<iOS 类似美团外卖 app 两个 tableView 联动效果实现&g ...

- 客户端和后台交互日期注意点 sqlite日期字段使用Date类型的情况下

不要直接传递时间类型 一般把时间格式化字符串后传递 不要传递Date().getTime() 毫秒数 非要使用的话需要在后台处理 传递的毫秒数 - TimeZone.getDefault().get ...

- 量化预测质量之分类报告 sklearn.metrics.classification_report

classification_report的调用为:classification_report(y_true, y_pred, labels=None, target_names=None, samp ...

- ccpc20190823

04 http://acm.hdu.edu.cn/showproblem.php?pid=6705 分析:先把每条边以 形式放进堆,堆按路径权值从小到大排序,然后每次取出堆顶,用v的出边扩展 新的路径 ...

- python后端面试第一部分:python基础--长期维护

1. 为什么学习Python? 2. 通过什么途径学习的Python? 3. Python和Java.PHP.C.C#.C++等其他语言的对比? 4. 简述解释型和编译型编程语言? https:/ ...

- 用Spring Tool Suite简化你的开发

如果你是一个喜欢用spring的人,你可能会在欣赏spring的强大功能外,对其各样的配置比较郁闷,尤其是相差较大的版本在配置文件方面会存在差异,当然你可以去花不少的时间去网上查找相关的资料,当你准备 ...