SystemVerilog 编写FSM

SystemVerilog 编写FSM

好书:

https://github.com/yllinux/blogPic/blob/master/doc/CummingsSNUG2003SJ_SystemVerilogFSM.pdf

https://github.com/yllinux/blogPic/blob/master/doc/CummingsSNUG2019SV_FSM1.pdf

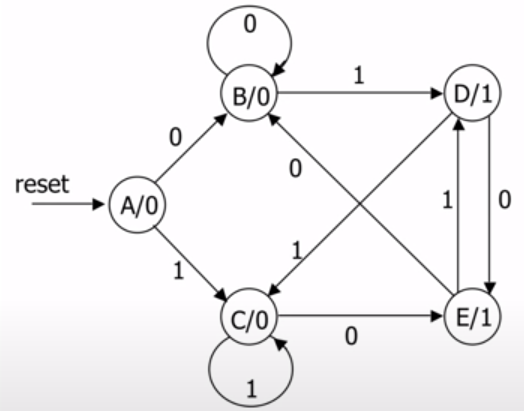

题目

SystemVerilog实现

module ExampleFSM (

input logic clk ,

input logic reset ,

input logic X ,

output logic Y

);

typedef enum logic [2:0] {A, B, C, D, E} state ; // 定义枚举类型

state currentState, nextState ; // 声明自定义类型变量

always_ff @(posedge clk , posedge reset) // 状态转移,同步时序,推荐3行式

if (reset) currentState <= A ;

else currentState <= nextState ;

always_comb begin // 状态转移条件判断,组合逻辑

nextState = 3'bxxx ; //@ loopback,需要写上

case (currentState)

A : if (X) nextState = C ;

else nextState = B ;

B : if (X) nextState = D ;

else nextState = B ; //@LB

C : if (X) nextState = C ;

else nextState = E ;

D : if (X) nextState = C ;

else nextState = E ;

E : if (X) nextState = D ;

else nextState = B ;

default : nextState = A ; // 需要写上

endcase

end

// assign Y = (currentState == D | currentState == E) ; // 组合输出

// always_ff @(posedge clk , posedge reset)

// if (reset)

// Y <= 1'b0 ;

// else begin

// Y <= (nextState == D | nextState == E) ;

// end

always_ff @(posedge clk , posedge reset)

if (reset)

Y <= 1'b0 ;

else begin

Y <= 1'b0 ;

case (nextState)

D : Y <= 1'b1 ;

E : Y <= 1'b1 ;

// don't need default

endcase

end

endmodule

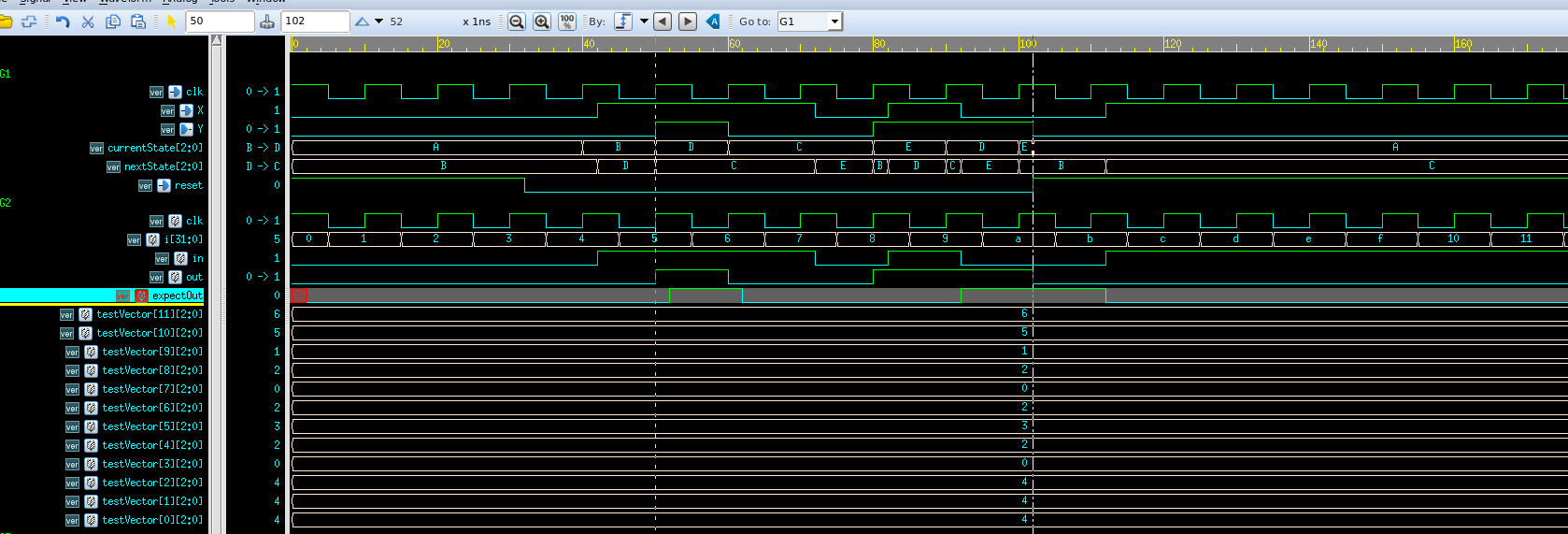

仿真

`timescale 1ns/1ns

module ExampleFSM_TB ();

logic clk=1 ;

logic reset ;

logic in ;

logic out ;

logic expectOut ;

logic [31:0] i ;

ExampleFSM dut (

.clk ( clk ),

.reset ( reset ),

.X ( in ),

.Y ( out )

);

logic [2:0] testVector [1000:0] ;

initial begin

$readmemb ("TestBenchVector.txt", testVector, 0, 19) ;

i = 0;

reset = 1; in = 0;

#200ns; $finish;

end

always @(posedge clk) begin

{reset, in, expectOut} <= #2 testVector[i] ;

$display(reset, in, expectOut, $time);

end

always @(negedge clk) begin

if (expectOut !== out) begin

$display("wrong output for inputs %b, %b != %b, address %d", {reset, in}, expectOut, out, i, $time);

end

i = i + 1 ;

end

always begin

clk <= 1; #5 ;

clk <= 0; #5 ;

end

//-----------------------------------------

// for VCS generate fsdb file

//-----------------------------------------

initial begin

$fsdbDumpfile("./digital.fsdb");

$fsdbDumpvars(0,ExampleFSM_TB,"+all");

$fsdbDumpflush();

end

endmodule

激励向量文件:TestBenchVector.txt

10_0

10_0

10_0

00_0

01_0

01_1

01_0

00_0

01_0 // 01_1

00_1

10_1

11_0

11_0

11_0

11_0

11_0

11_0

11_0

11_0

11_0

SystemVerilog 编写FSM的更多相关文章

- 关于RiscV的一些资料整理

1. 基于RISC-V架构的开源处理器及SoC研究综述 https://mp.weixin.qq.com/s/qSD-q8y0_MY8R0MBA85ZZg 原文链接: https://blog.csd ...

- 《SystemVerilog验证-测试平台编写指南》学习 - 第3章 过程语句和子程序

<SystemVerilog验证-测试平台编写指南>学习 - 第3章 过程语句和子程序 3.1 过程语句 3.2 任务.函数以及void函数 3.3 任务和函数概述 3.4 子程序参数 3 ...

- 《SystemVerilog验证-测试平台编写指南》学习 - 第2章 数据类型

<SystemVerilog验证-测试平台编写指南>学习 - 第2章 数据类型 2.1 内建数据类型 2.2 定宽数组 2.2.1 声明 2.2.2 常量数组 2.2.3 基本的数组操作 ...

- 《SystemVerilog验证-测试平台编写指南》学习 - 第1章 验证导论

<SystemVerilog验证-测试平台编写指南>学习 - 第1章 验证导论 测试平台(testbench)的功能 方法学基础 1. 受约束的随机激励 2. 功能覆盖率 3. 分层的测试 ...

- 使用有限状态机(FSM)编写的敌人AI

using UnityEngine; using System.Collections; public class AttackState : FSMState { public AttackStat ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm summary

主要是1.不要用1段式写FSM 2.不要用状态编码写one-hot FSM ,要用索引编码写one-hot FSM.

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 FSM Coding Goals

1.the fsm coding style should be easily modifiable to change state encoding and FSM styles. FSM 的的 状 ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(三段式)

Three always block style with registered outputs(Good style)

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(二段式)

1.Two always block style with combinational outputs(Good Style) 对应的代码如下: 2段式总结: (1)the combinational ...

随机推荐

- [单调栈]Imbalanced Array

I m b a l a n c e d A r r a y Imbalanced Array ImbalancedArray 题目描述 You are given an array a a a con ...

- js 一数组分割成若干个数组,并装换成字符串赋个li标签

success: function (datas) { //请求成功后处理函数. var htmltext = ''; var data = datas.result; console.log(dat ...

- Python函数参数和注解是什么

四种参数 Python函数func定义如下: def func(first, *args, second="Hello World", **kwargs): print(first ...

- 2018年block3学习计划

还是要给自己制定一个block的计划,希望自己的技术能有更进一步的提升 1. 算法/数学 随着学习的进一步深入,愈发认识到了算法的重要性,这个block给自己定下的计划就是 1)把introducti ...

- IDEA xml 注解快捷键

注释:CTRL + SHIFT + / 撤销注释:CTRL + SHIFT + \

- Python学习笔记-PuLP库(3)线性规划实例

本节以一个实际数学建模案例,讲解 PuLP 求解线性规划问题的建模与编程. 1.问题描述 某厂生产甲乙两种饮料,每百箱甲饮料需用原料6千克.工人10名,获利10万元:每百箱乙饮料需用原料5千克.工人2 ...

- 锁定项目的 node 版本

一些老项目对 node 版本是有要求的,往往使用默认的新版本包安装不上,scripts 也跑不起来. 之前就遇到过运行一个小程序项目时,根据文档来,第一步安装就出错.本着办法总比问题多的理念,来一个解 ...

- 基于MATLAB的手写公式识别(7)

今天晚上通过对原有T4模型的修改实现: 1.可以识别真彩图形.(这基本是一样大的,通过这个了解图像分割的原理) 2.在识别心脑管血药类的基础上实现数字的识别.(了解图像识别原理,熟练掌握图像分割技术) ...

- 记weblogic上传shell路径

0x01 前言 自从上次在渗透过程中发现了波weblogic CVE-2020-2551漏洞后面又对其进行了复现,后边看到exp里有个上传webshell的功能,但是由于不清楚weblogic这个路径 ...

- 基于Docker配置本地Gitlab

技术背景 Github和Gitee(码云)是最常见的基于git的代码托管平台,现在基于svn的代码管理仓库已经相对比较少见了,大部分还都是企业内部的代码仓.但是基于开源的Gitlab,我们在企业内网也 ...