dac verilog ad5601

首先从官网下载数据手册。DAC有串行有并行,ad5601是串行,(需要好多时钟沿的移位内部转换为并行在输出)。

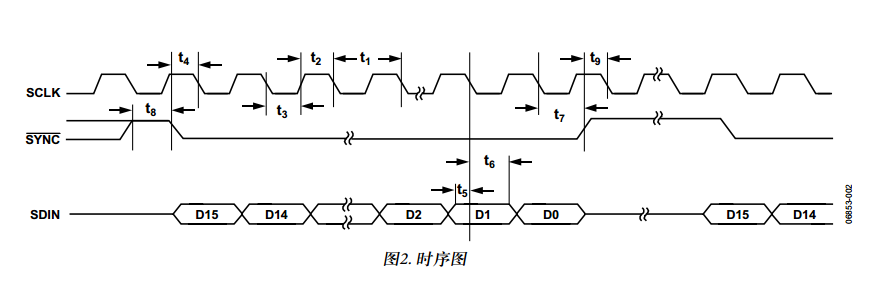

按照手册的时序编写程序,

关注下芯片的波特率范围

看看手册的数据传输那些事有效的数据位

module dac

(

input clk,

input rst_n_in,

output reg sclk,

output reg sync,

output reg din

);

//产生状态

reg[5:0] cnt=0;

always@(posedge clk or negedge rst_n_in)

begin

if(!rst_n_in)

cnt<=0;

else

begin

if(cnt>=34)cnt<=0;

else cnt<=cnt+1;

end

end

reg[15:0] data_reg=16'h1740;

always@(posedge clk or negedge rst_n_in)

begin

if(!rst_n_in)begin sclk=0;sync=1; end

else begin

case(cnt)

0: begin

data_reg=16'h1740;//显示的数据,16位中前两位无效位,最后6位无效位,中间8位为数据位

end

1:begin sclk=1;din=data_reg[15];sync=0;end

2:begin sclk=0;end //

3:begin sclk=1;din=data_reg[14];end

4:begin sclk=0;end //

5:begin sclk=1;din=data_reg[13];end

6:begin sclk=0;end //

7:begin sclk=1;din=data_reg[12];end

8:begin sclk=0;end //

9:begin sclk=1;din=data_reg[11];end

10:begin sclk=0;end //

11:begin sclk=1;din=data_reg[10];end

12:begin sclk=0;end //

13:begin sclk=1;din=data_reg[9];end

14:begin sclk=0;end //

15:begin sclk=1;din=data_reg[8];end

16:begin sclk<=0;end //

17:begin sclk=1;din=data_reg[7];sync=0;end

18:begin sclk=0;end //

19:begin sclk=1;din=data_reg[6];end

20:begin sclk=0;end //

21:begin sclk=1;din=data_reg[5];end

22:begin sclk=0;end //

23:begin sclk=1;din=data_reg[4];end

24:begin sclk=0;end //

25:begin sclk=1;din=data_reg[3];end

26:begin sclk=0;end //

27:begin sclk=1;din=data_reg[2];end

28:begin sclk=0;end //

29:begin sclk=1;din=data_reg[1];end

30:begin sclk=0;end //

31:begin sclk=1;din=data_reg[0];sync=0;end

32:begin sclk=0;end //

33:begin sclk=1; sync=1;end //

endcase

end

end

endmodule

dac verilog ad5601的更多相关文章

- 基于小脚丫DDS 调频 调幅 调相 切换波形 AD5601输出模拟波形

先讲讲里面的矩阵键盘,矩阵键盘列有下拉电阻,默认全为0000,默认行输入为1111,当有按键按下的时候,列输入会被拉高,这时控制行的输出做行扫描,电子琴用key_flag_r0电平作为使能,这里用ke ...

- STM32之DAC君

如花说得好:呃呃呃.是俗话说得好:有了ADC,怎可少了DAC..我觉得奇怪.今天我开头就直奔主题了.我想了想,总结了一句话:孙悟空纵然有七十二变.无论是变成猫也好,变成狗也罢.始终还是会变回他本身.所 ...

- DAC Usage4:从 Backup Package(.bacpac)还原DB

使用DAC,能够将database的schema 和 data 从一个server 或 cloud 上复制到另外一个server上,存储schema 和 data的文件是 .bacpac 文件. 方法 ...

- DAC Usage3:Monitor Data-tier Applications

If you deploy a DAC to a managed instance of the Database Engine, information about the deployed DAC ...

- DAC Usage2:通过DAC实现DB Schema的Migration和Upgrade

一,Introduce Extract DAC 是从现存的DB中创建DAC,抽取DB Object的definition 和 与之相关的实例级别的元素,比如Login,以及Login 和User之间的 ...

- 基于STM32Cube的DAC数模转化

1. STM32Cube配置 1.1 DAC配置 1.2 TIM6 配置 1.3 利用Cube产生工程程序,MDK打开软件 在主循环上添加语句: HAL_TIM_Base_S ...

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog HDL模型的不同抽象级别

所谓不同的抽象类别,实际上是指同一个物理电路,可以在不同层次上用Verilog语言来描述.如果只从行为功能的角度来描述某一电路模块,就称作行为模块.如果从电路结构的角度来描述该电路模块,就称作结构模块 ...

- Verilog学习笔记基本语法篇(十二)········ 编译预处理

h Verilog HDL语言和C语言一样也提供编译预处理的功能.在Verilog中为了和一般的语句相区别,这些预处理语句以符号"`"开头,注意,这个字符位于主键盘的左上角,其对应 ...

随机推荐

- 释放License命令

lmutil_x86.exe lmremove -c 1055@Vappcloud-WinS acfd Administrator VappCloud_Win7a.vancloud-corp.com ...

- 基于FPGA具有容错能理的异步串口程序设计

首先,问题源于一个项目.本来是一个很简单的多个串口收发FIFO存取数据的小程序,通过电脑验证也可用,而下位机板子之间通信就出现了丢数问题. 经过分析原因如下: 我的串口收模块是基于特权同学的开发板程序 ...

- VS(Visual Studio)中快速找出含中文的字符串

环境:visual studio 2017 1.ctrl + shift + f 打卡全局查找 2.输入(".*[\u4E00-\u9FA5]+)|([\u4E00-\u9FA5]+.*&q ...

- Clean Code之JavaScript代码示例

译者按: 简洁的代码可以避免写出过多的BUG. 原文: JavaScript Clean Code - Best Practices 译者: Fundebug 本文采用意译,版权归原作者所有 引文 作 ...

- Fiddler-抓Android和IOS包

知识:Fiddler能捕获IOS设备发出的请求,比如IPhone, IPad, MacBook. 等等苹果的设备. 同理,也可以截获Andriod,Windows Phone的等设备发出的HTTP/ ...

- OJDBC版本区别:ojdbc14.jar,ojdbc5.jar和ojdbc6.jar的区别

classes12.jar - for Java 1.2 and 1.3ojdbc14.jar - for Java 1.4 and 1.5ojdbc5.jar - for Java 1.5ojdbc ...

- [BJWC2008]雷涛的小猫 dp

题目背景 原最大整数参见P1012 题目描述 雷涛同学非常的有爱心,在他的宿舍里,养着一只因为受伤被救助的小猫(当然,这样的行为是违反学生宿舍管理条例的).在他的照顾下,小猫很快恢复了健康,并且愈发的 ...

- [HNOI2011]数学作业 矩阵快速幂 BZOJ 2326

题目描述 小 C 数学成绩优异,于是老师给小 C 留了一道非常难的数学作业题: 给定正整数 NNN 和 MMM ,要求计算Concatenate(1..N) Concatenate (1 .. N) ...

- CoinEye PRIVACY POLICY

PRIVACY POLICY First, welcome to use the app Thank you for using our products and services ("Se ...

- EIGRP-3-EIGRP的多参数度量

带宽度量参数本身无法区分10Gbit/s及更高速率的接口.对1Gbit/s接口,默认延迟度量参数已设置为最低值1(10微妙).而且EIGRP承载的是经过换算的参数,每台路由器需要将其换算回再计算新开销 ...