嵌入式ROM核的调用

本次设计的工具和源码在:http://download.csdn.net/detail/noticeable/9914766

课程目的:调用quartus II提供的rom(read only memory)进行系统项目设计

实验现象:将一组固定的波形数据以MIF的格式存储于fpga中使用IP核构建的片上ROM中,开发板上电后,系统从ROM 中读取数据,并将数据通过I/O口输出,使用signal TAP II取I/O口输出的数据,即可得到三角波形;并通过quartus II提供的in system memory content editor 工具在线更改ROM 中的数据,然后再次通过signal TAP II将更改后的波形读取出来。

知识点:1、mif文件的生成方法2、ROM IP核的使用。3、In-system memory content editor 内存查看工具的使用。4、signalTap II 调试工具的简单使用

开发流程:

首先,自己创建对应波形的mif文件,以便后面调用rom IP核的时候使用

可以自己创建一个文本,然后在文件中输入自己想自己想要显示的波形的数据再保存,但是这样设计使得设计过于繁琐,这里推荐使用软件mif_maker2010直接生成.mif文件(软件在源码压缩包中)

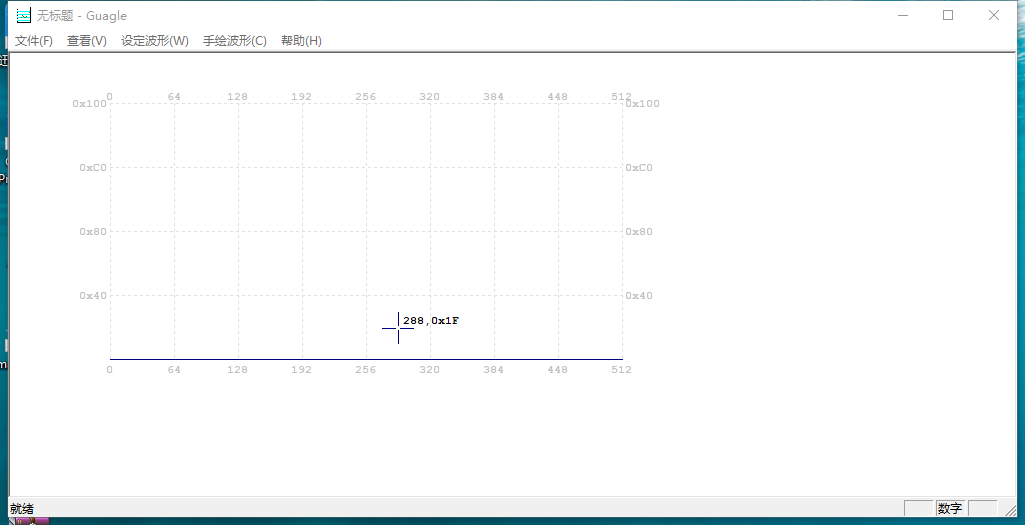

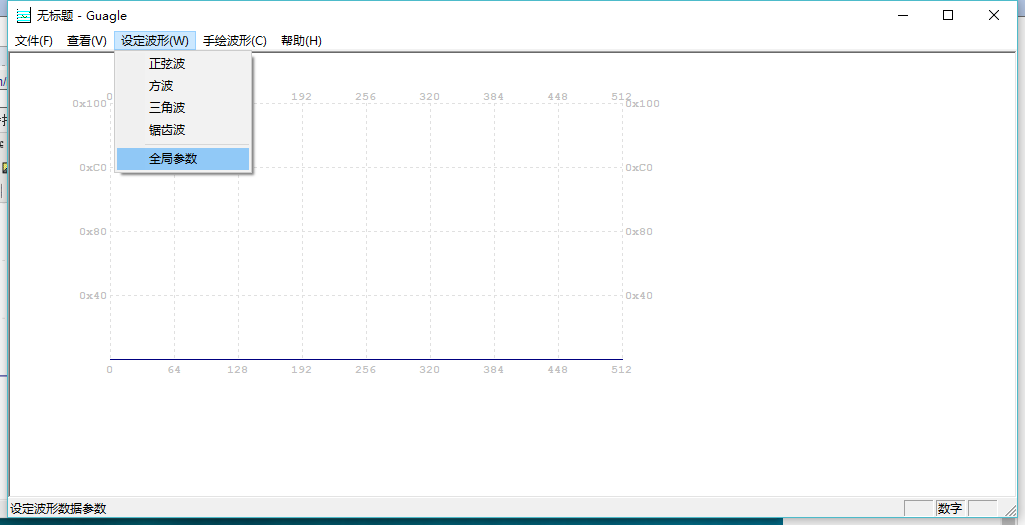

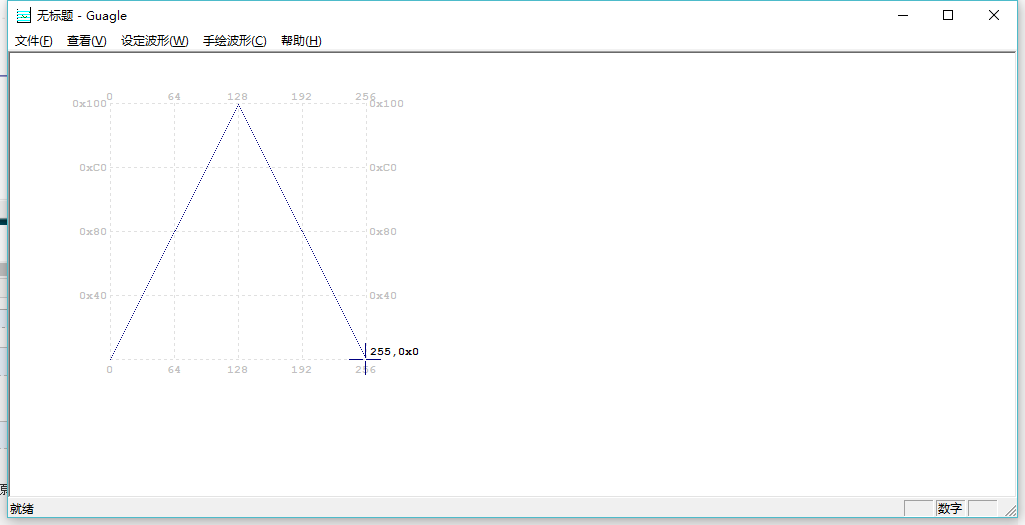

打开软件

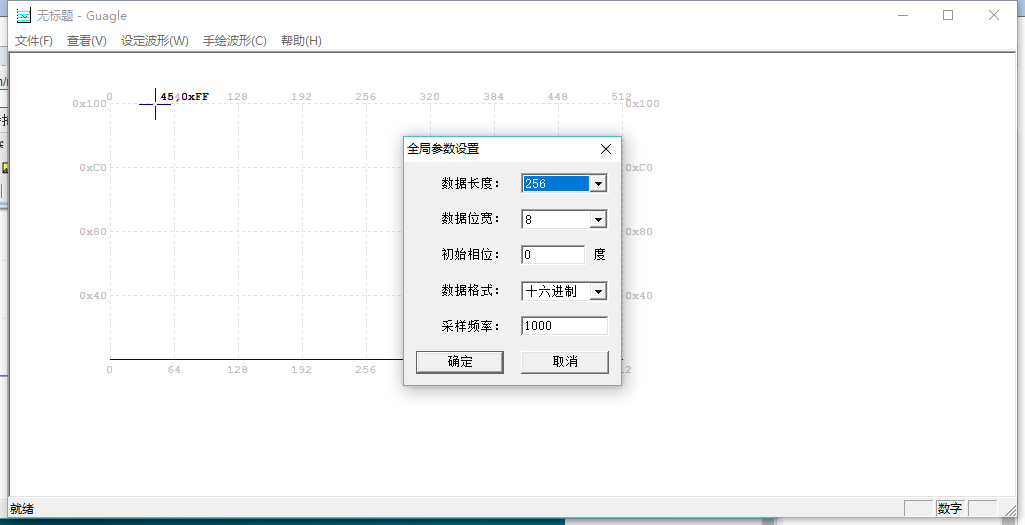

设置全局参数

本次设计为256个数据长度8位位宽

选择期望生成的波形,保存即可得到相应波形对应参数的mif文件。

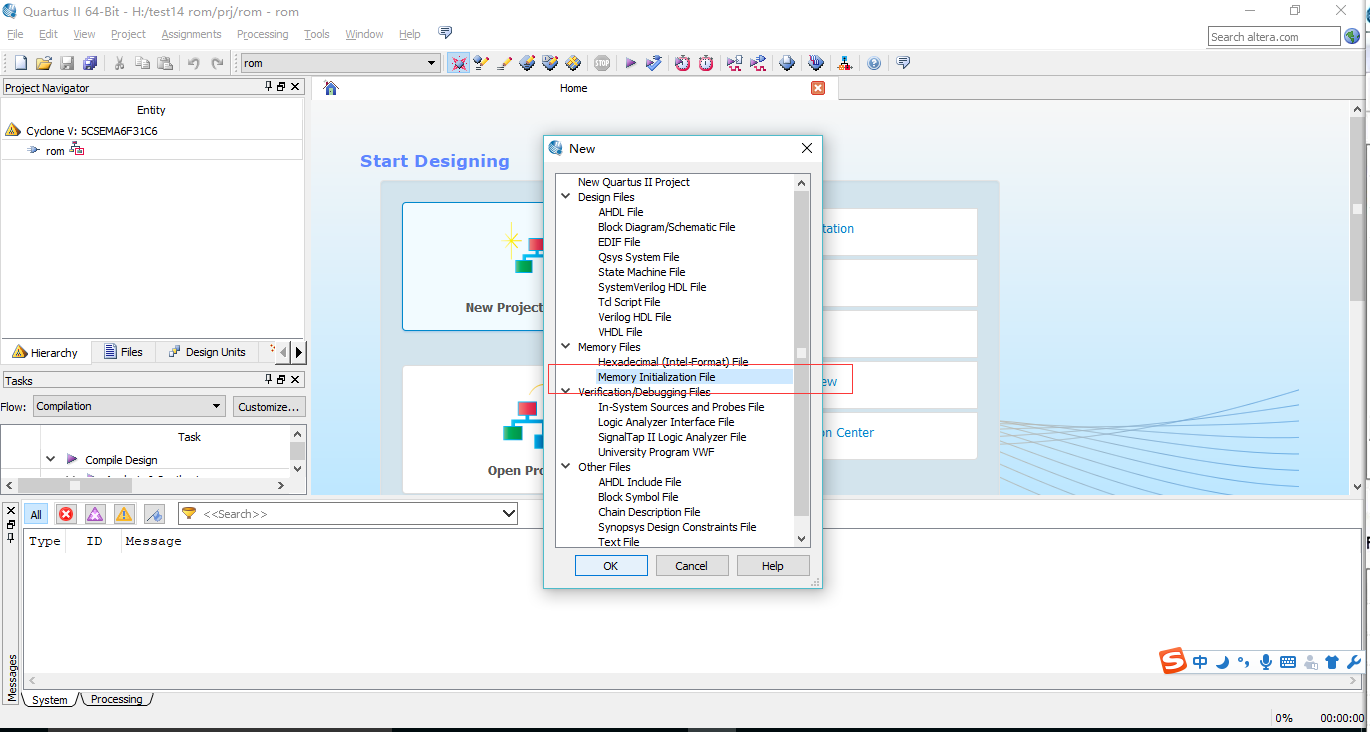

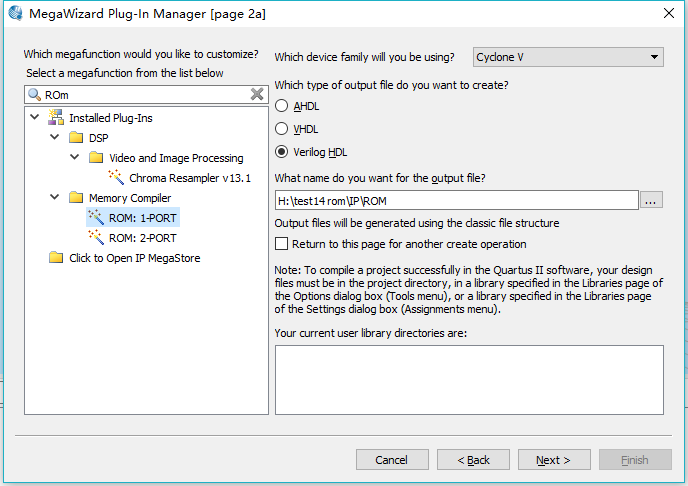

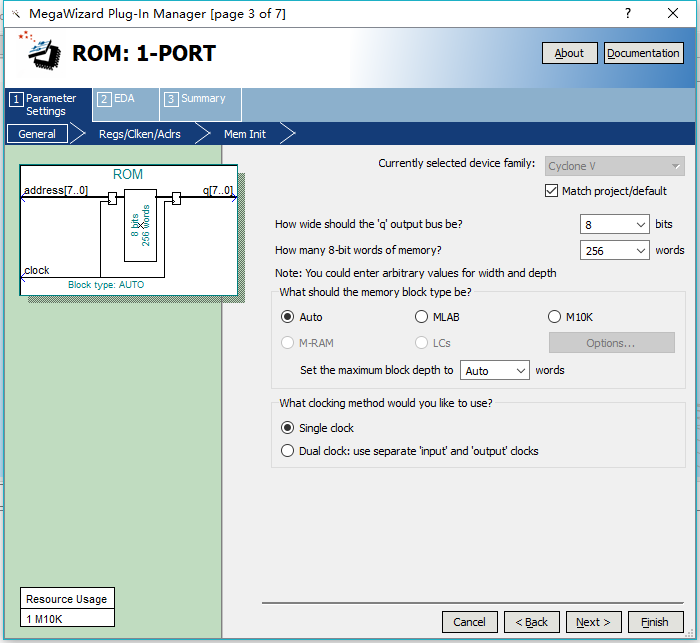

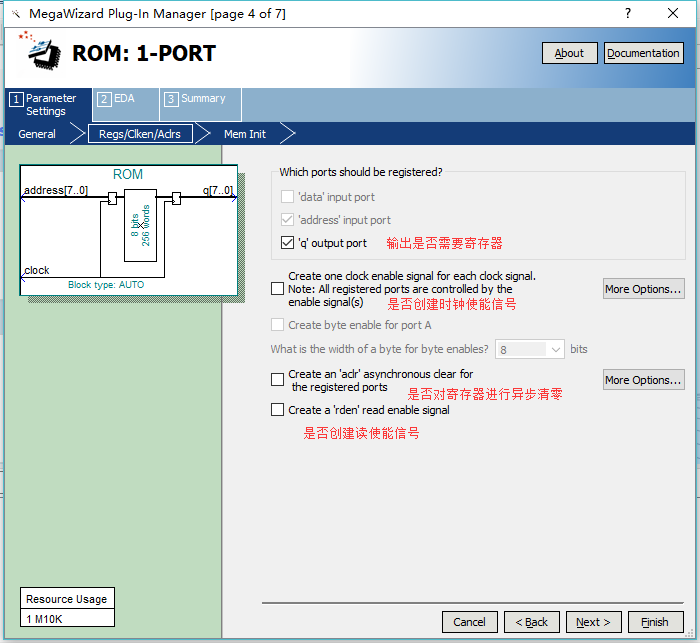

新建工程,调用rom ip核

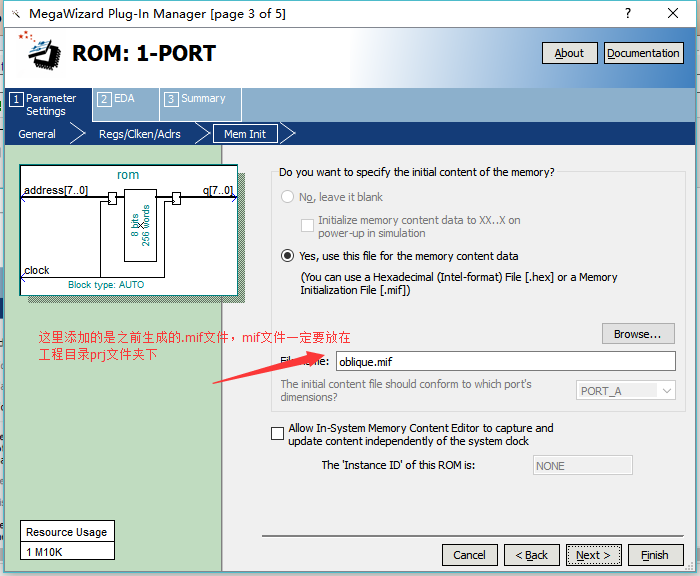

之后直接next到finish即完成生成rom文件了。

之后直接next到finish即完成生成rom文件了。

将IP核设置为顶层文件

然后编写IP核的testbench文件

`timescale 1ns/1ns

`define clock_period

module rom_tb;

reg [:]addr;

reg clk;

wire [7:0]q;

rom rom (

.address(addr),

.clock(clk),

.q(q));

initial clk=;

always#(`clock_period/)

clk=~clk; integer i;

initial

begin

addr=;

for(i=;i<=;i=i+)begin

#`clock_period;

addr=addr+;

end

#(`clock_period*);

$stop;

end endmodule

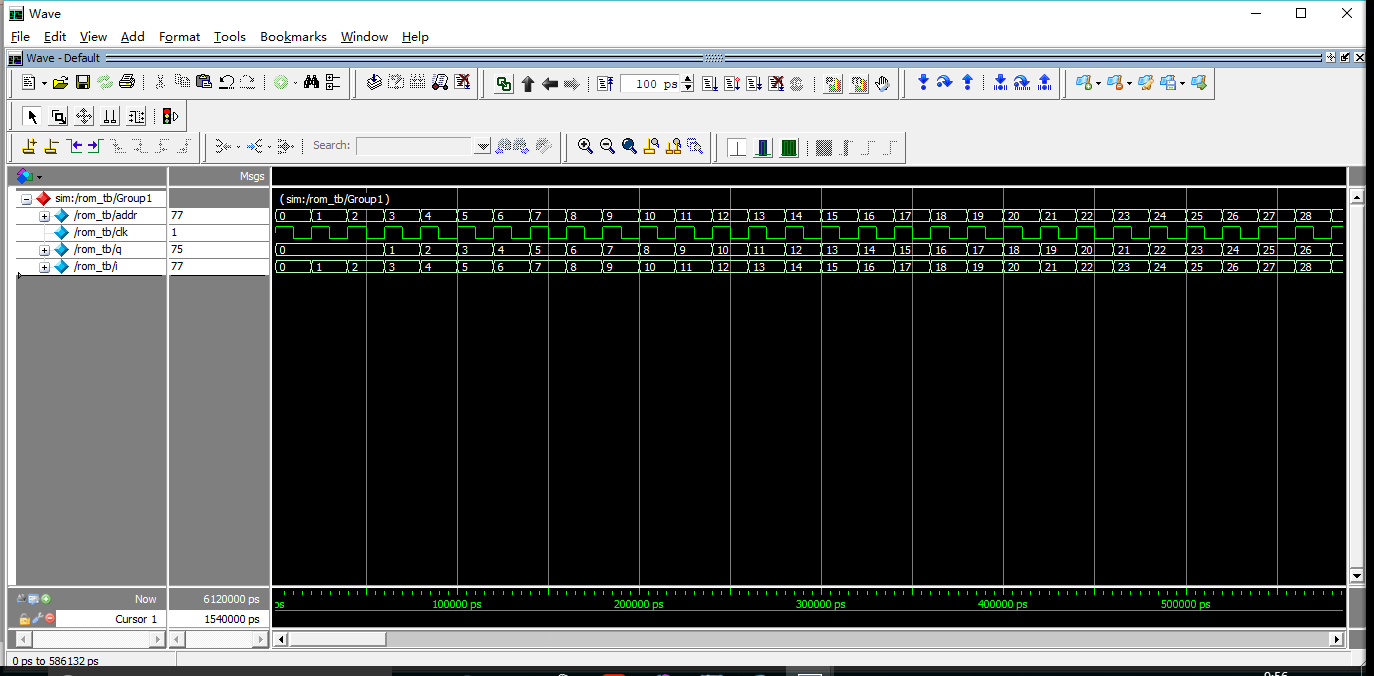

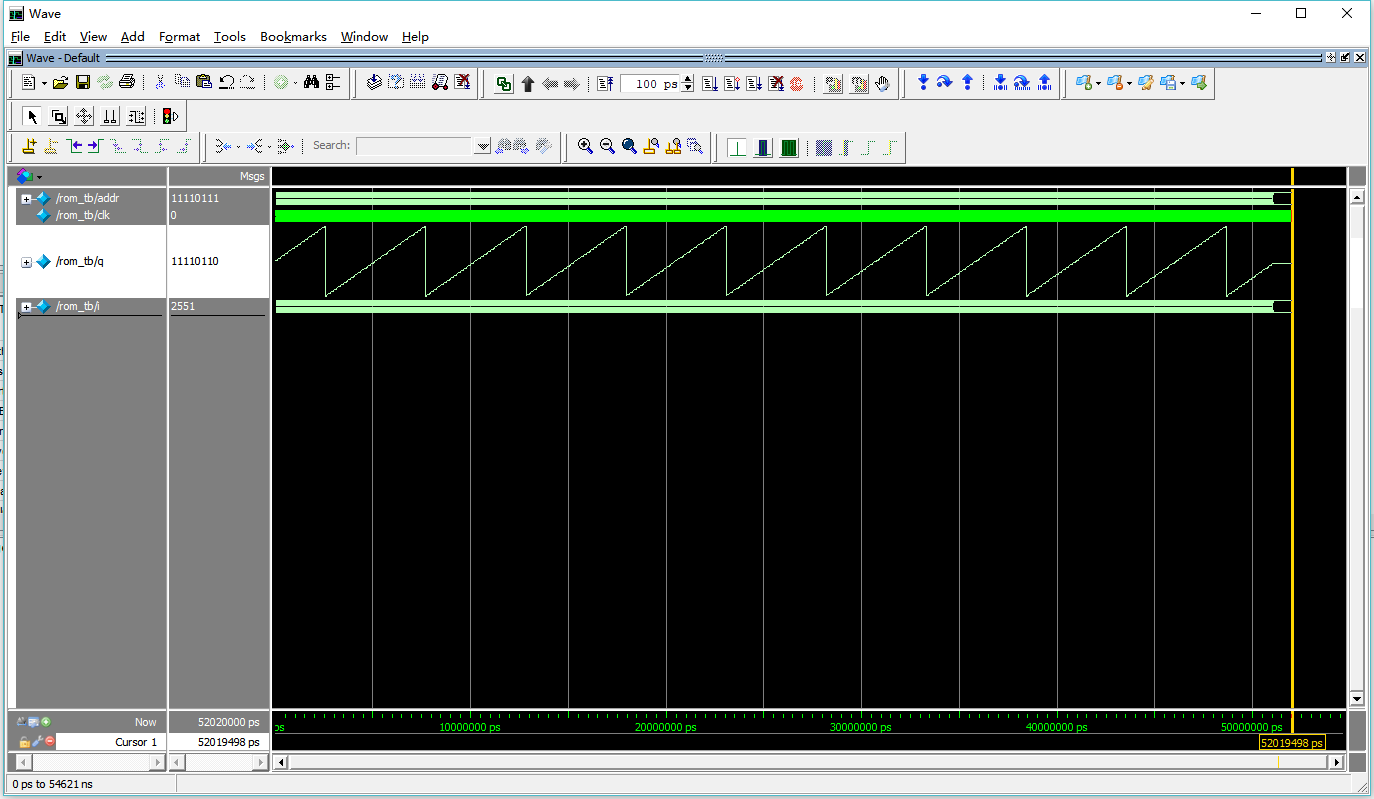

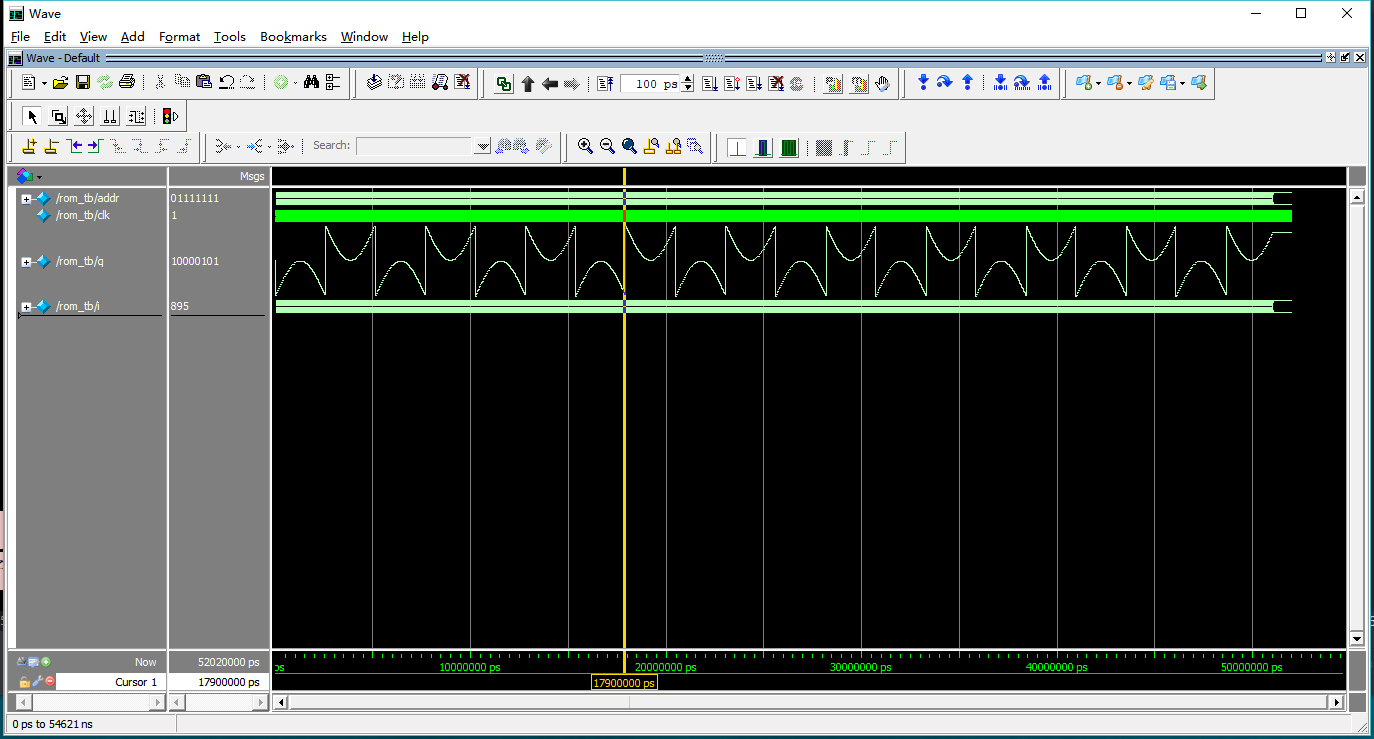

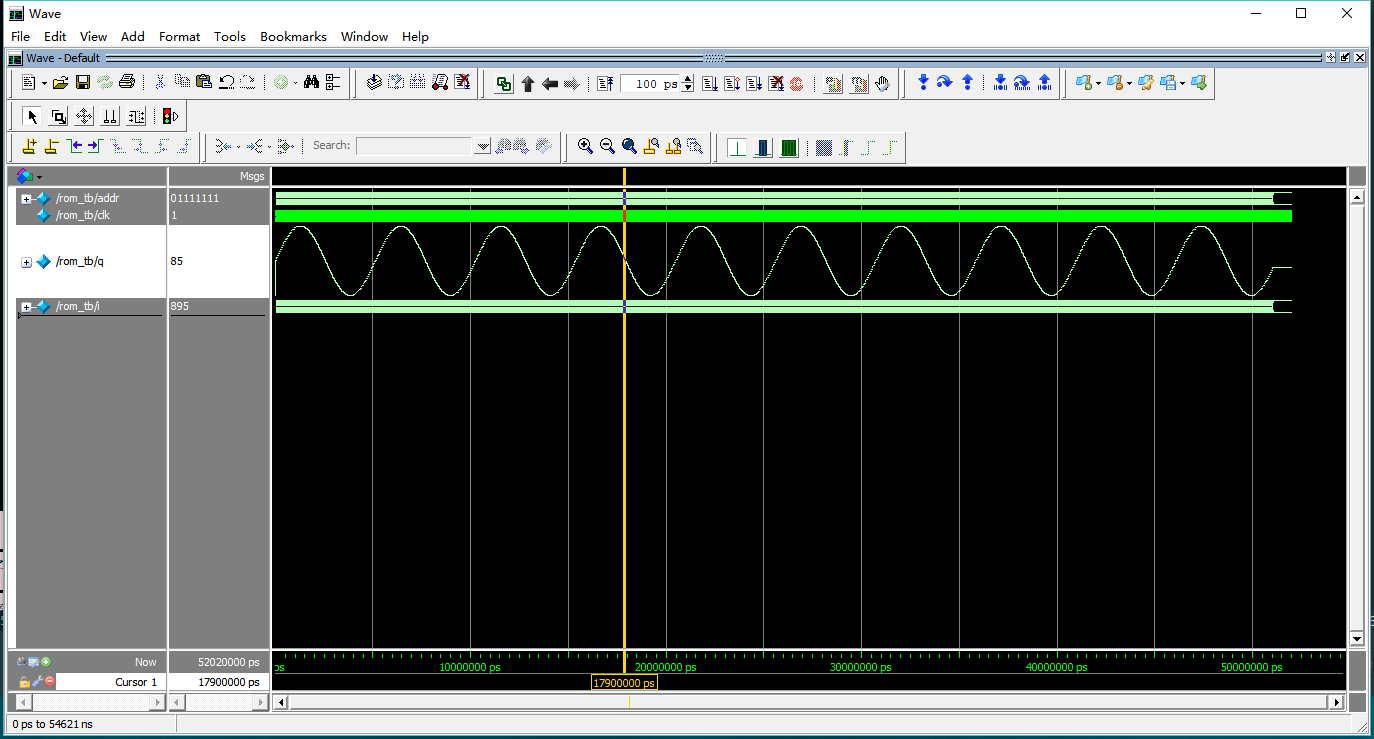

设定仿真路径进行仿真,可以看到q成功的将mif文件提取出来了,并通过仿真加强对romIP核的理解

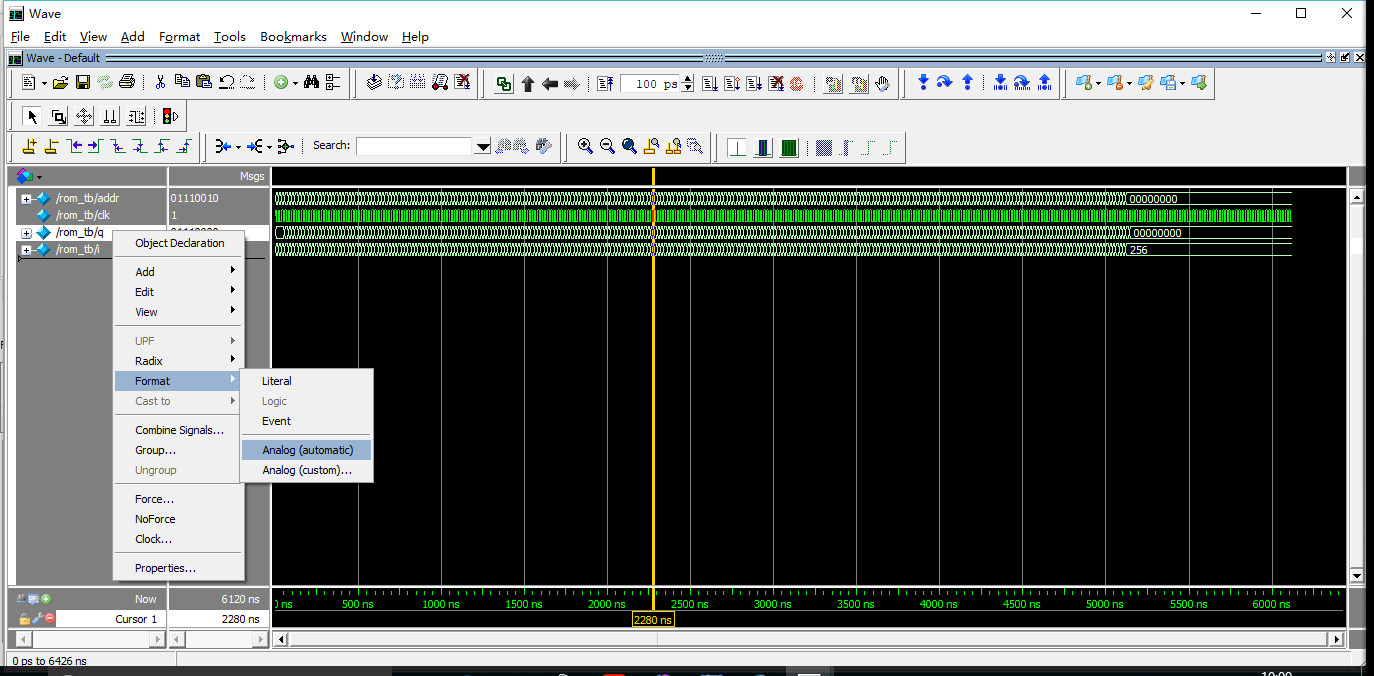

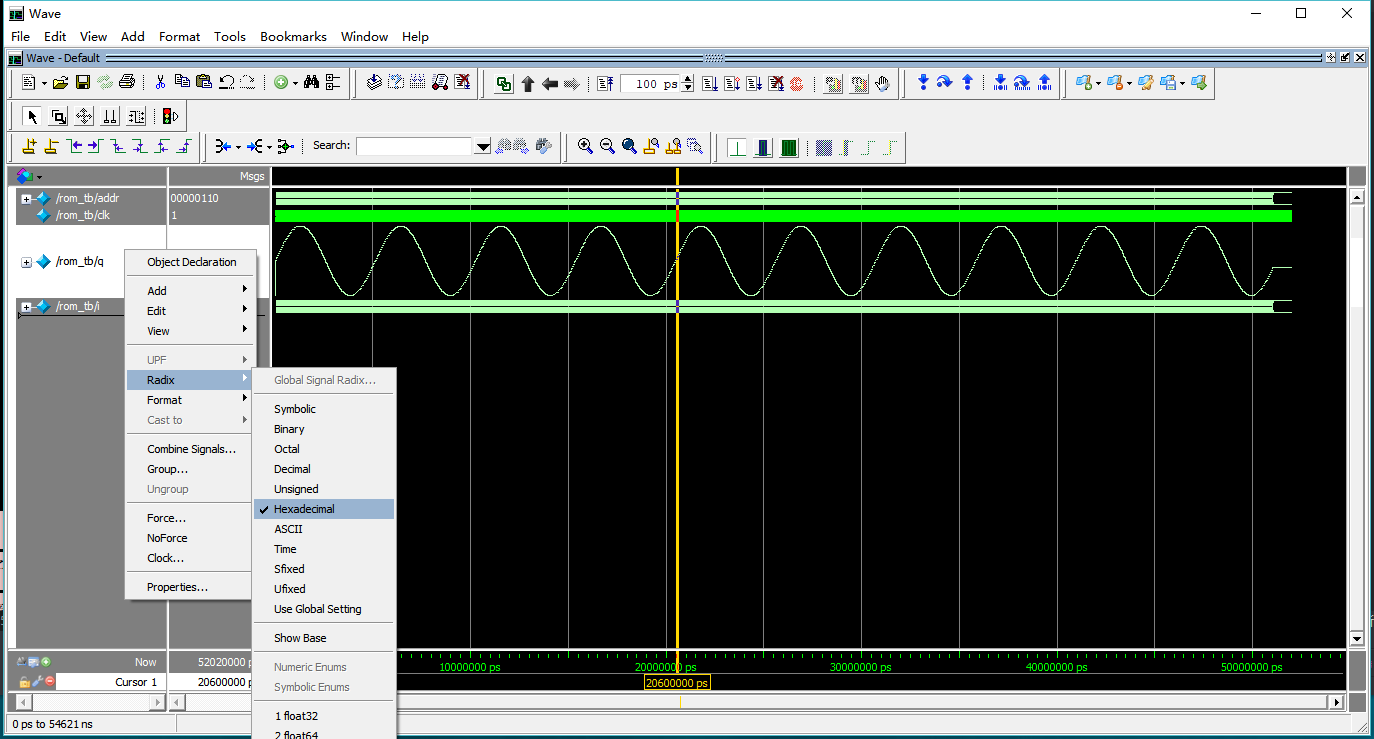

选中q,右键修改显示格式,即可看到仿真出来的模拟的锯齿波形。

将mif未见改为正弦波的mif文件观察

此时发现波形有断层

这是因为选择的显示格式为无符号的,将格式改为有符号的即可

在这里,波形发生器的仿真设计已经完成了(对于控制频率,其实就是一个控制地址变化的方式)。

新建一个rom_top文件,将其设置为顶层文件,其目的是设计地址发生模块:

module rom_top(clk,

rst_n,

q

); input clk;

input rst_n;

output [:]q;

reg [:]addr;

rom rom_1 (

.address(addr),

.clock(clk),

.q(q)); always@(posedge clk or negedge rst_n)

if(!rst_n)

addr<=;

else

addr<=addr+; endmodule

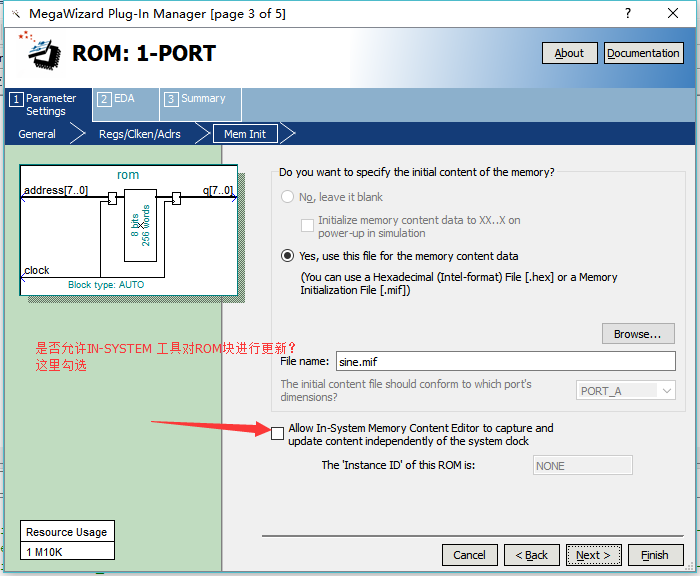

下面为了使in system memory content editor 工具在线修改ROM中的数据,需要对IP核进行设置

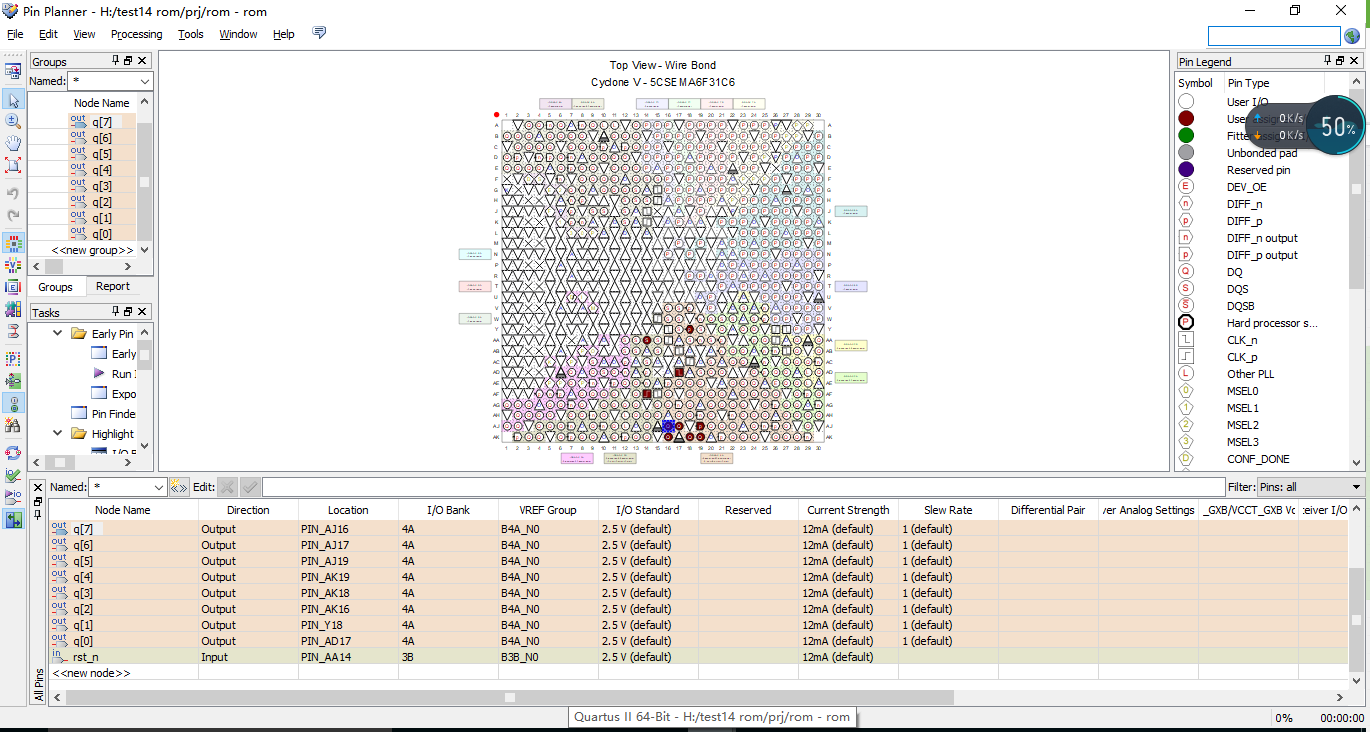

对引脚进行分配,其中q[0]~q[7]对应开发板上GOIP09~GPIO2

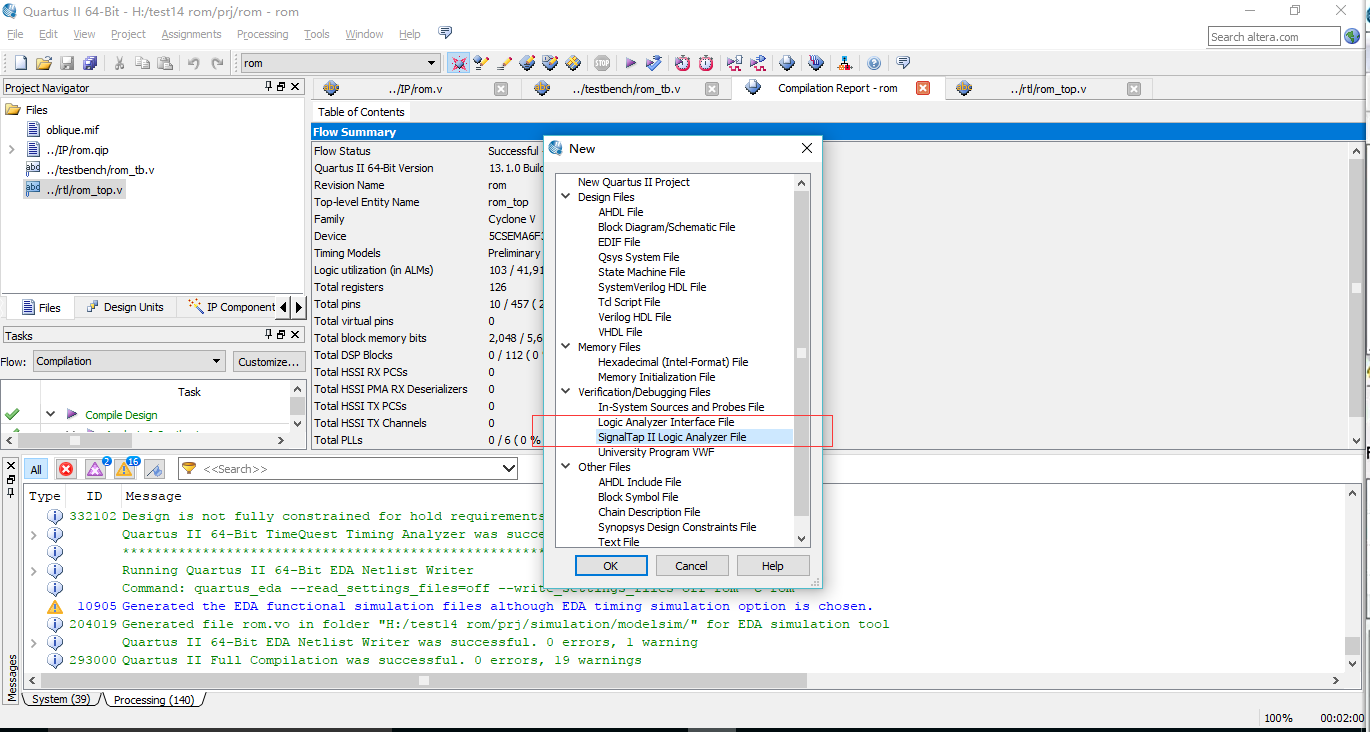

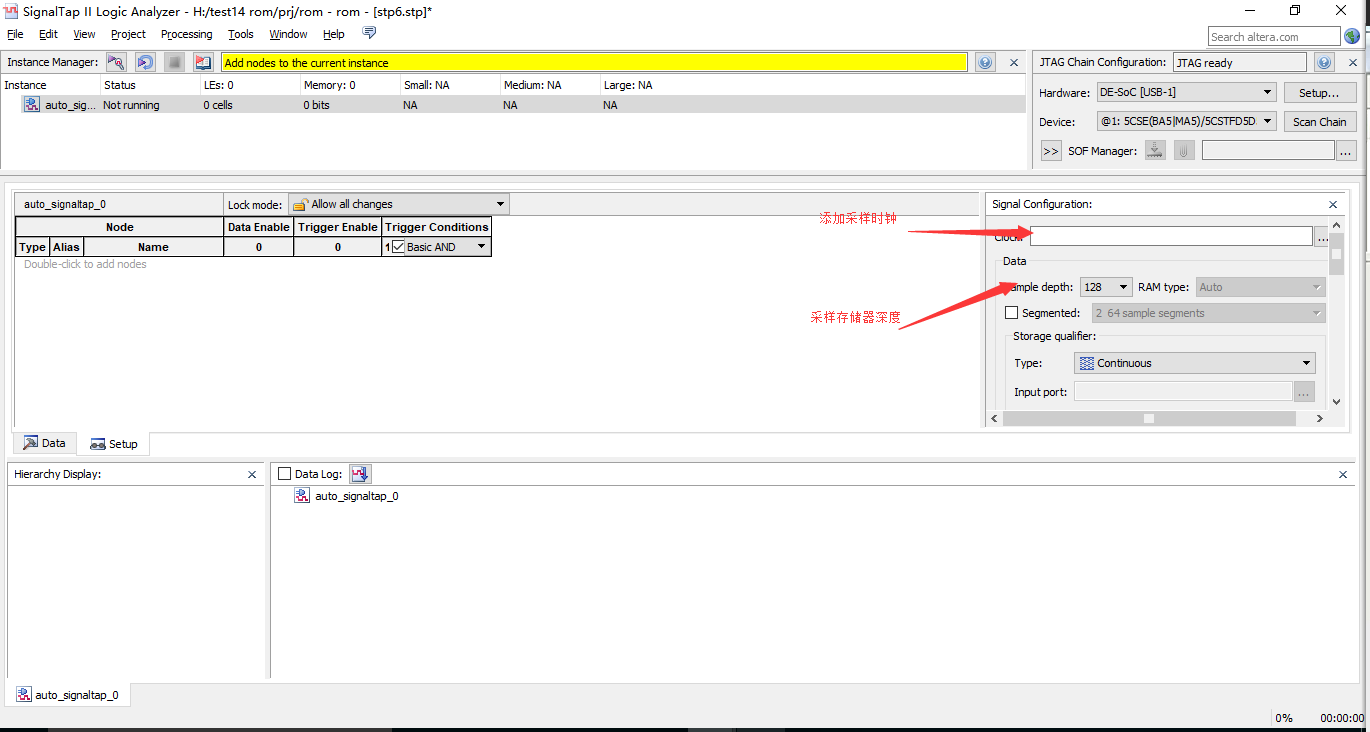

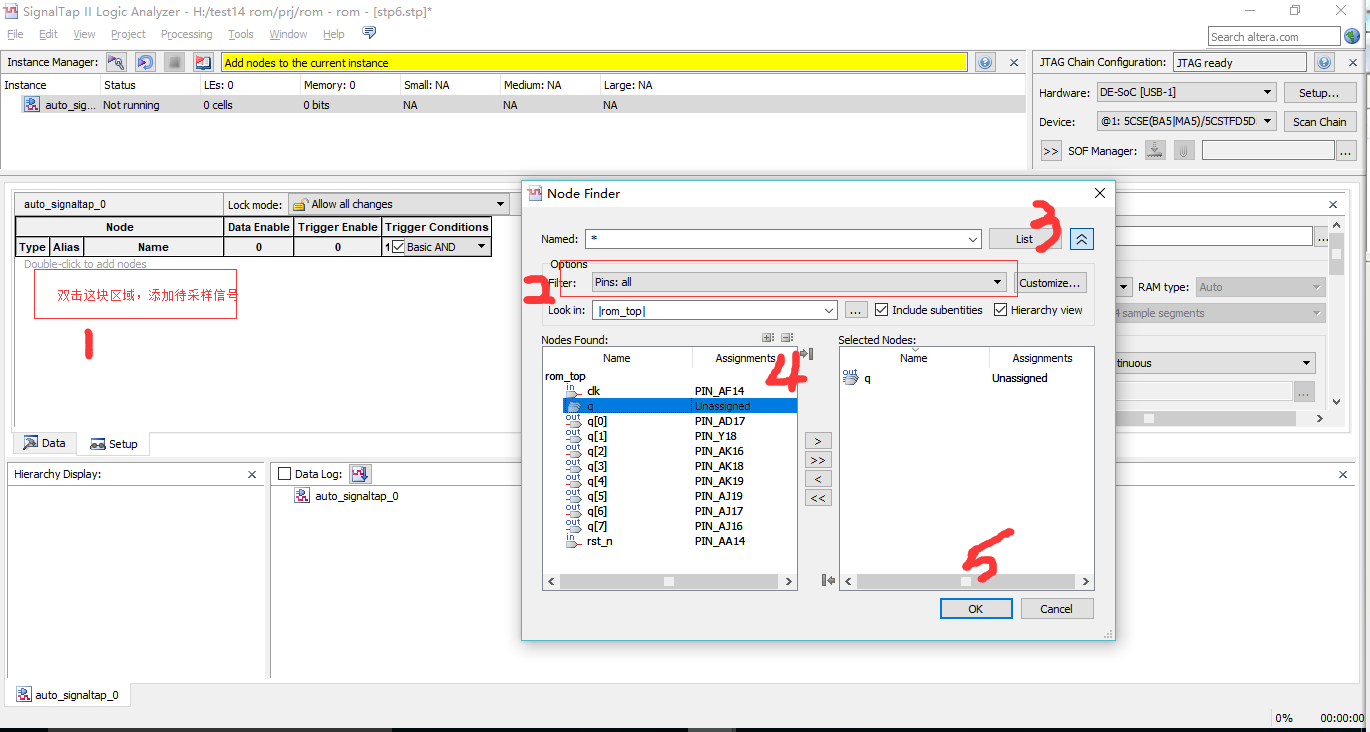

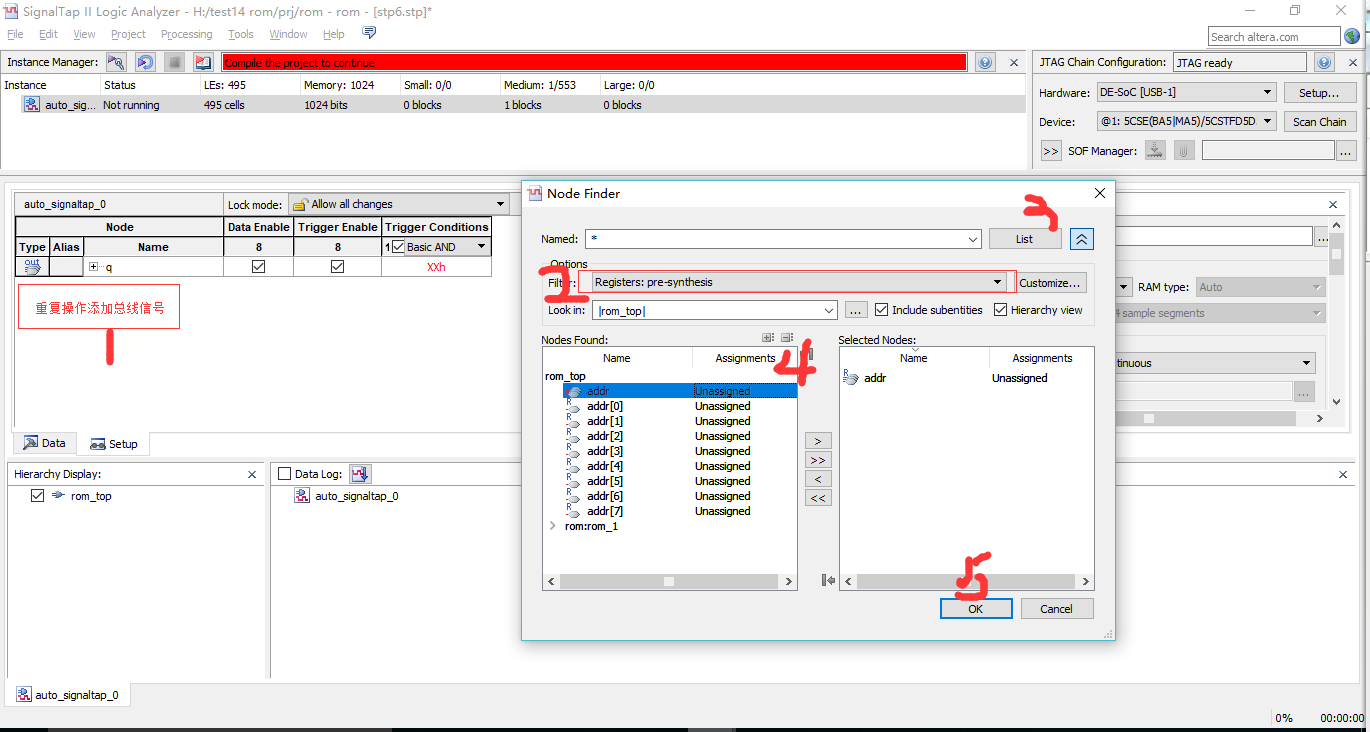

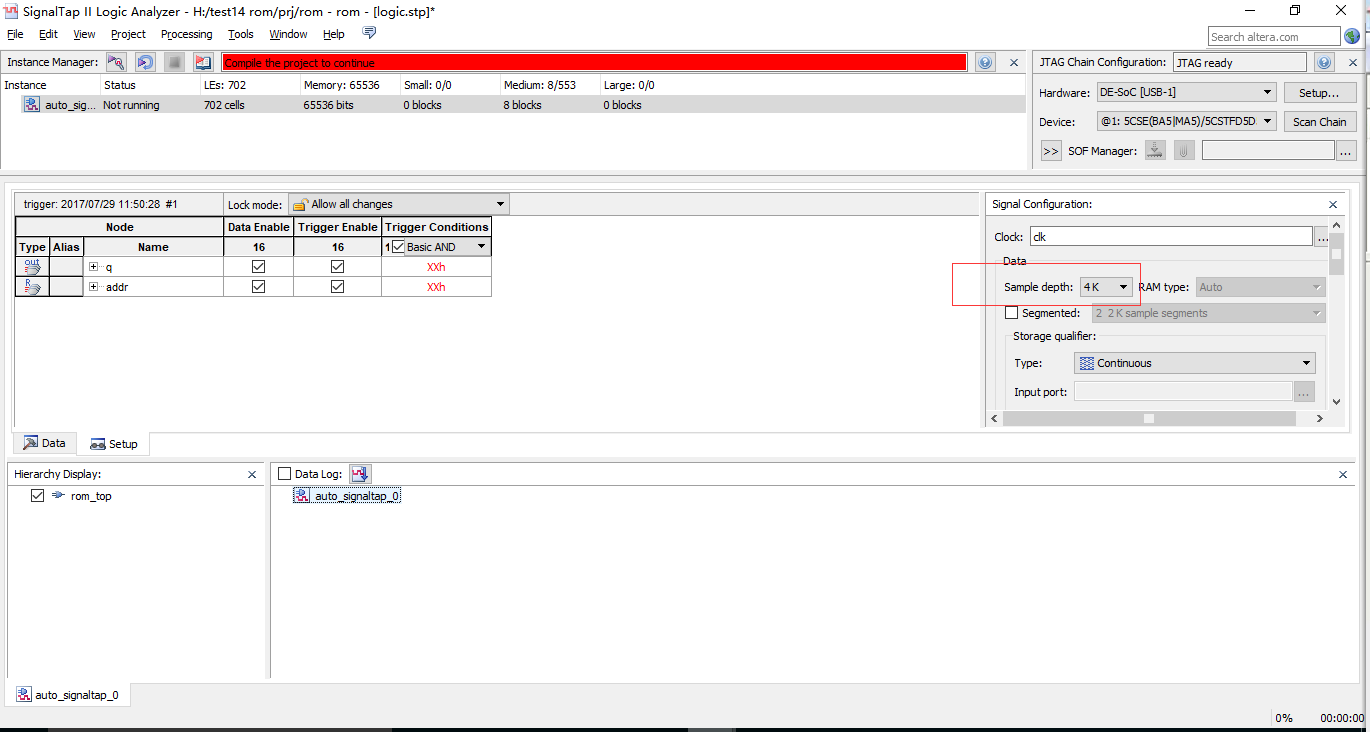

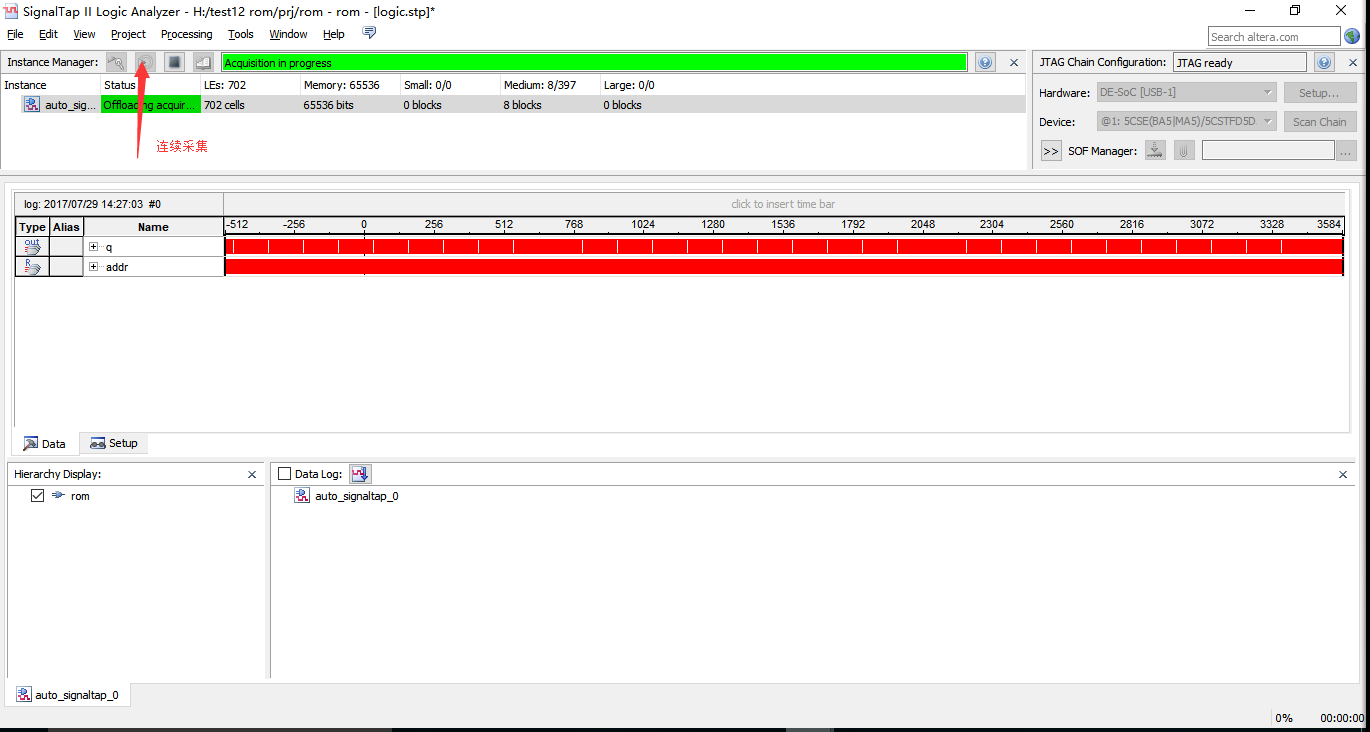

全编译后,通过FPGA内部搭建一个片上的逻辑分析仪,抓取rom里的文件:

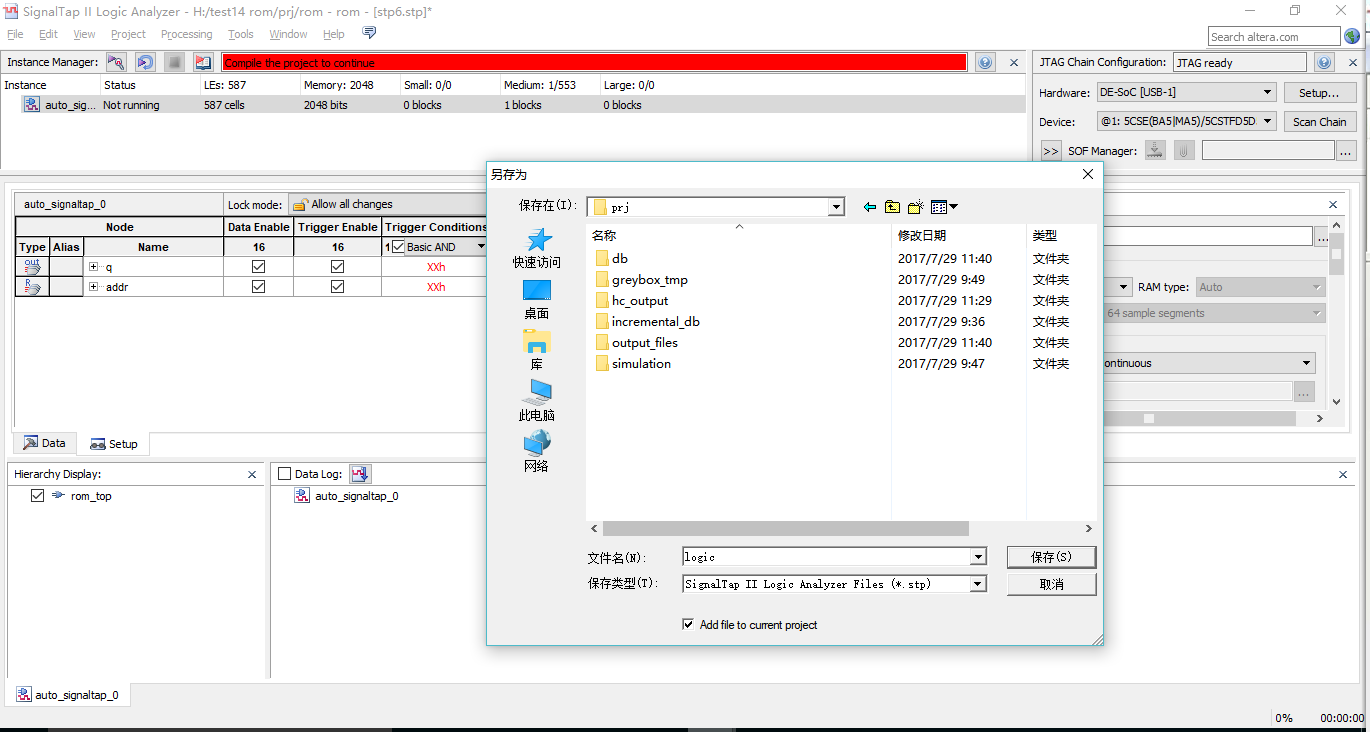

新建一个signal tap II logic analyzer file文件

保存在工程目录下

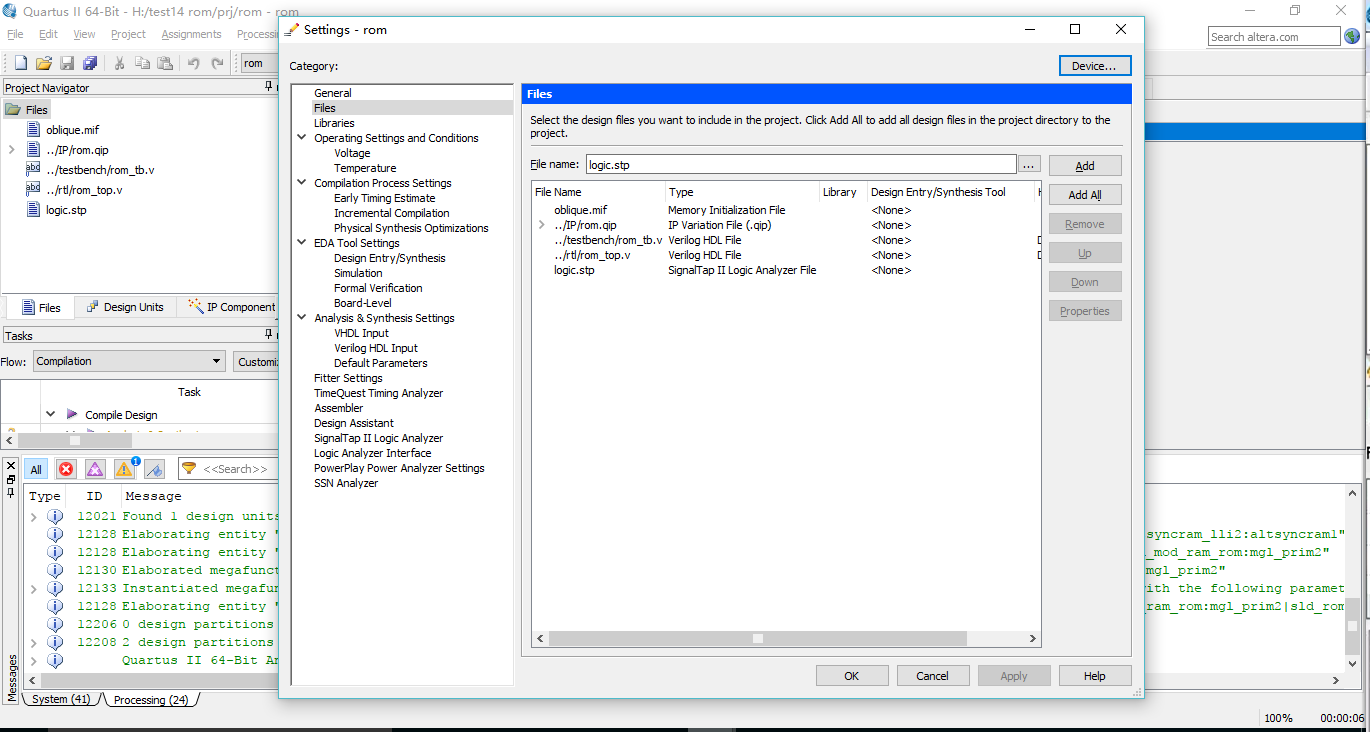

将逻辑分析仪工具添加到工程文件夹中,对工程进行全编译

将工程生成的.sof文件下载到FPGA开发板中,进行板级验证,烧写完成后打开logic.stp文件

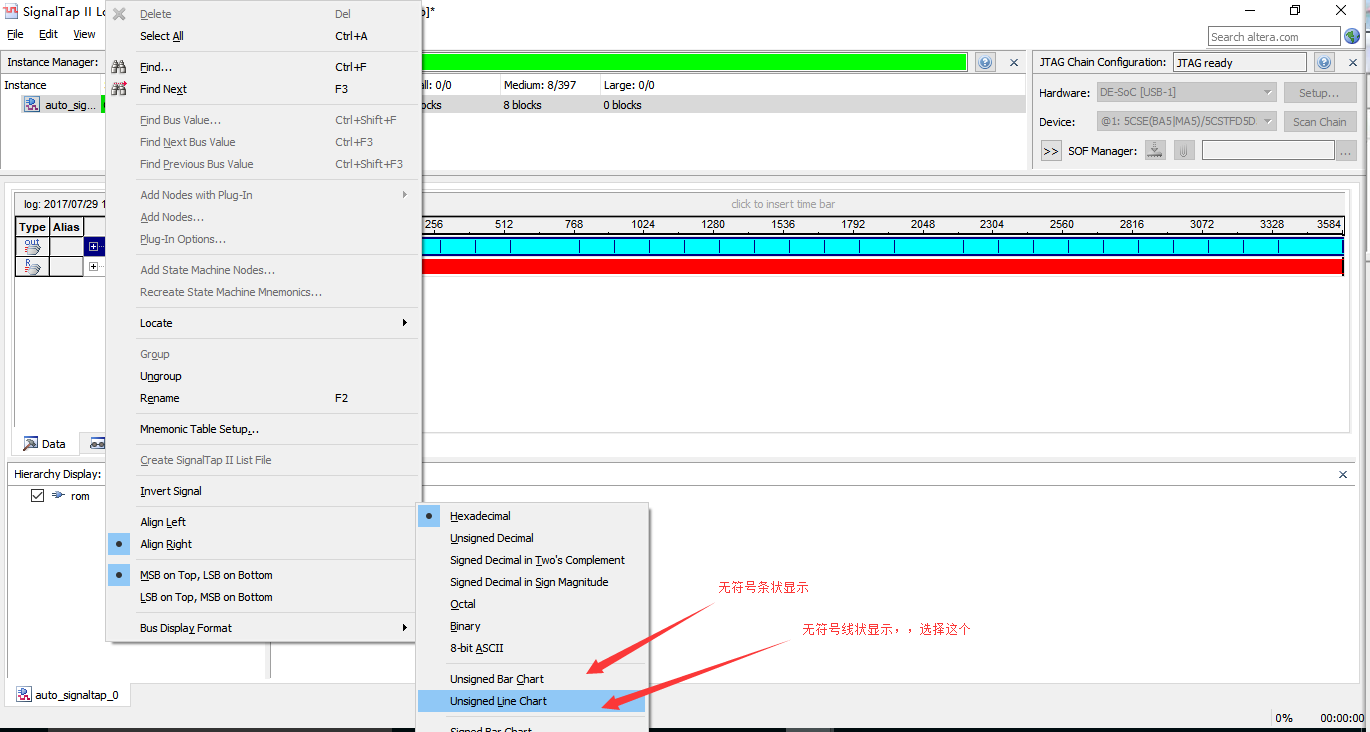

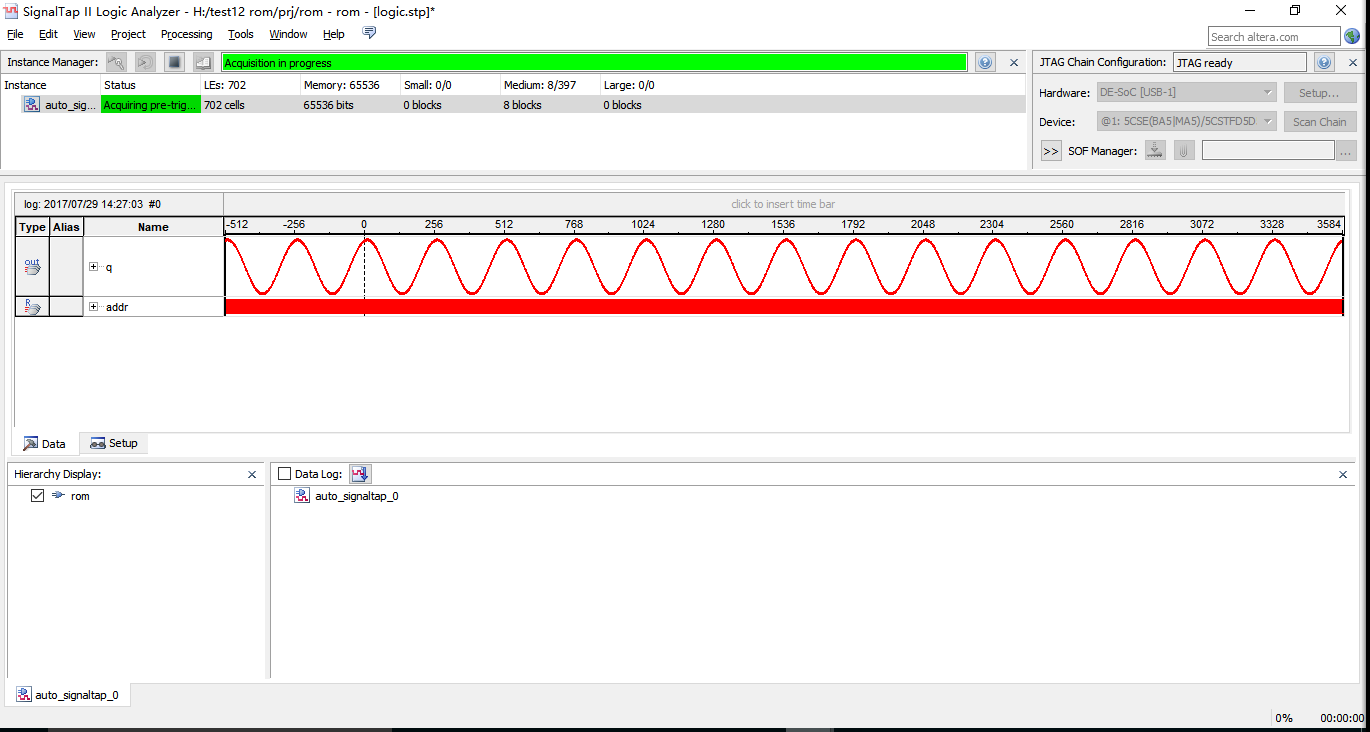

即可看到成功显示的正弦波波形了

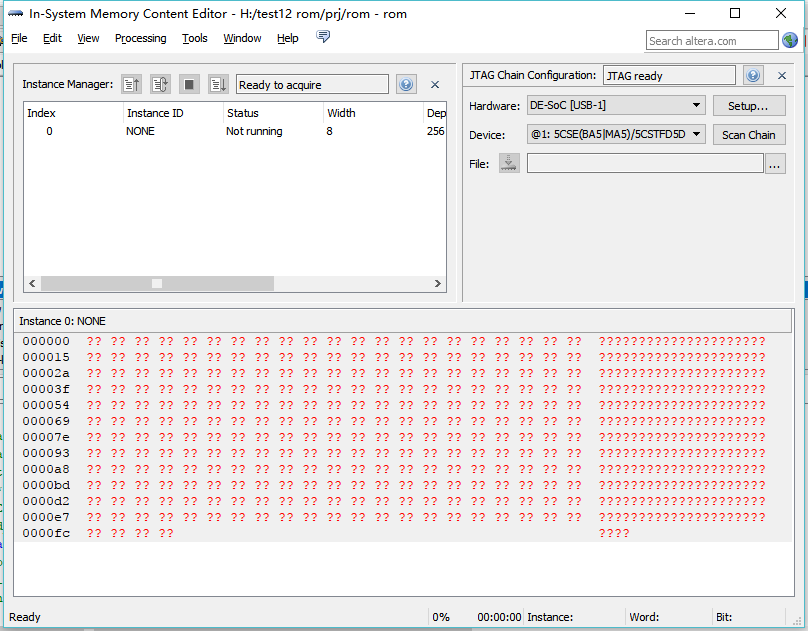

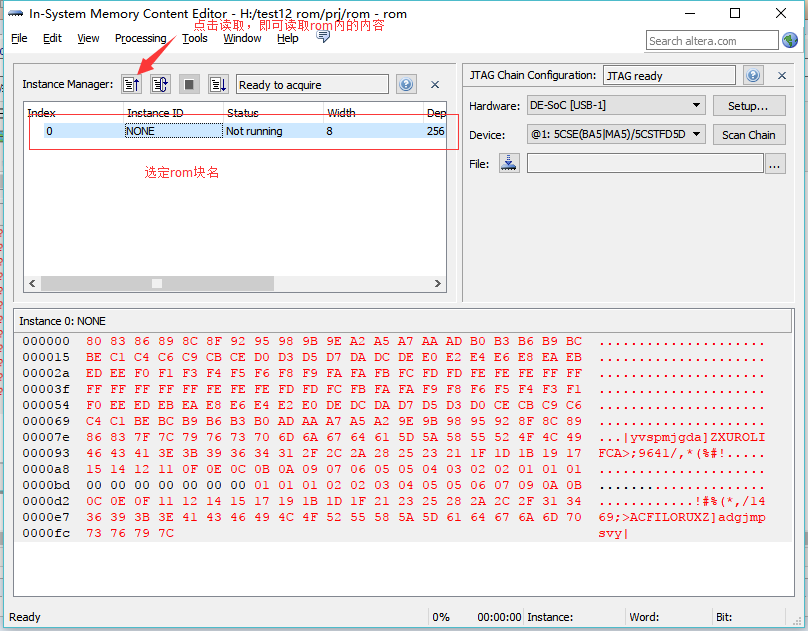

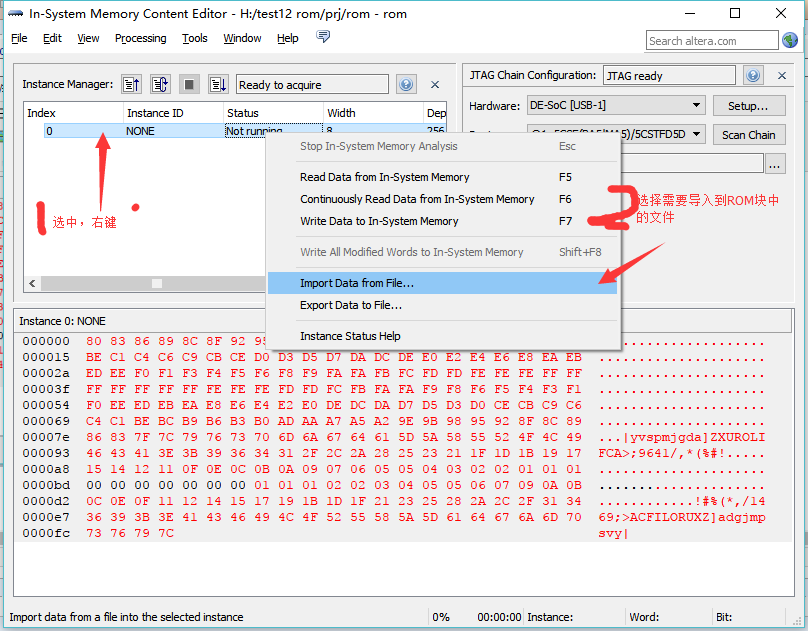

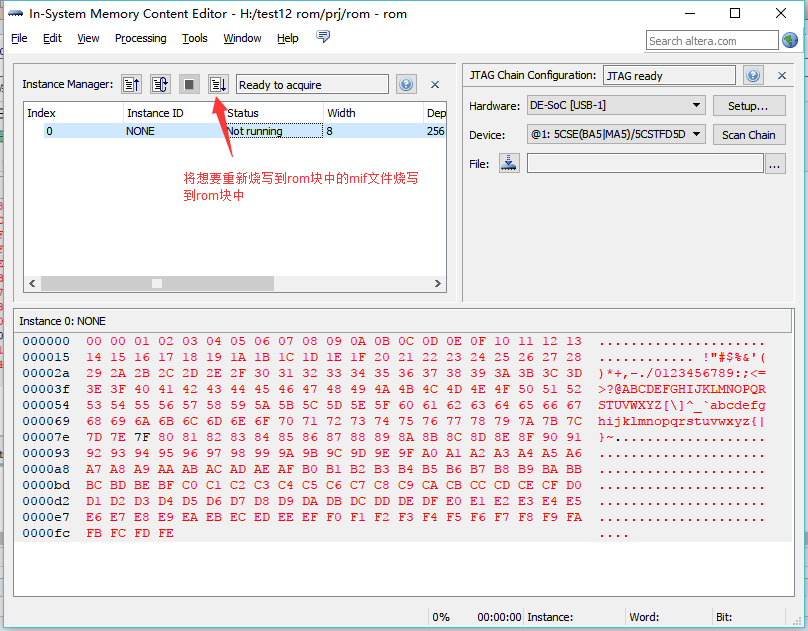

下面通过in system memory content editor 工具对rom 内容进行更改

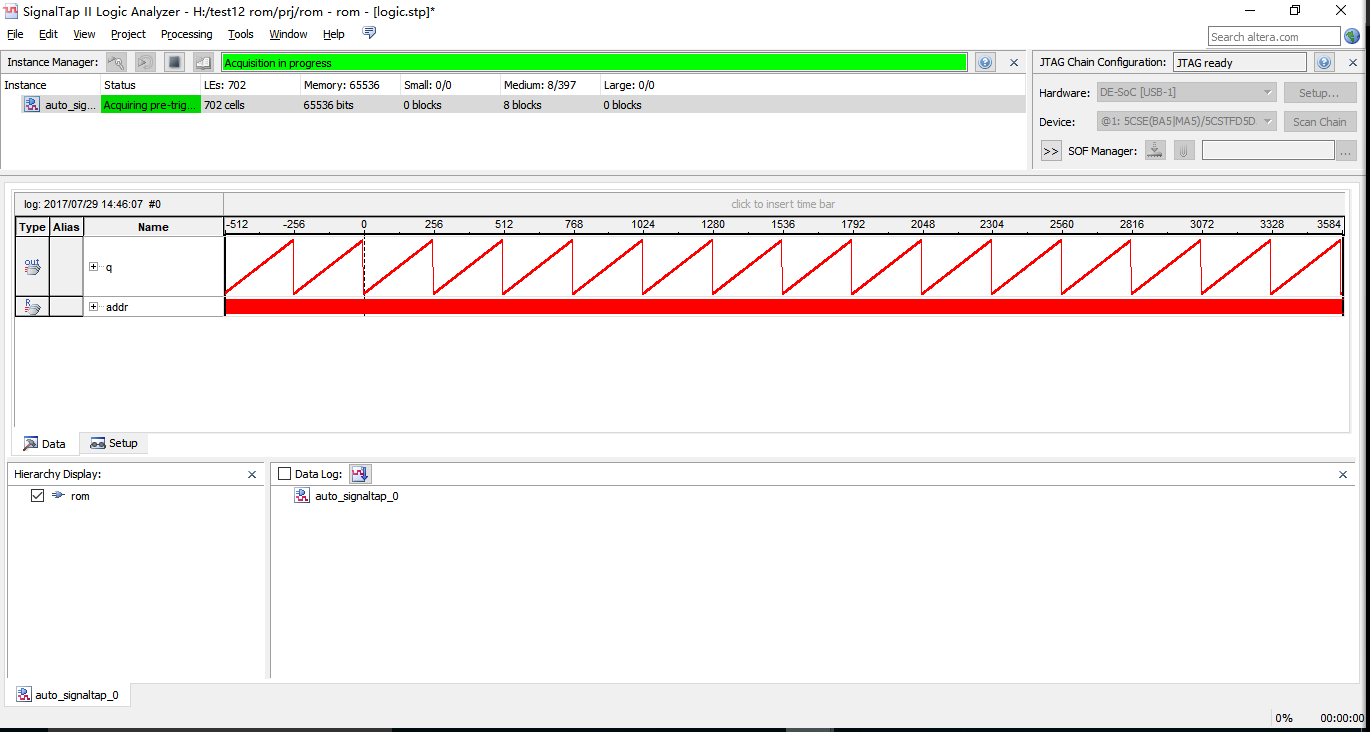

可以看到signalTap II logic analyzer中显示的波形变为了锯齿波了。

至此,整个设计就完成了

嵌入式ROM核的调用的更多相关文章

- 嵌入式FIFO核的调用

本次设计源码下载地址:http://download.csdn.net/detail/noticeable/9915523 课程目标:学习调用quartus II 软件的FIFO(先进先出)IP核,并 ...

- modelSIM仿真ROM核报错

用Quartus Prime 15.1调用modelSIM进行RTL仿真,modelSIM的transcript框框总是有Failed to Open Readmem File提示. 错误原因:IP核 ...

- 移动工程后,打开ROM核无配置信息

问题: 从他人处下载的ISE工程,打开dw51的ROM IP核,无配置信息,为block memory generator的初始配置,并显示无法找到coe文件 原因:ROM配置过程中的部分内容丢失导致 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- FPGA开发随笔汇总

点击标题即可进入相关随笔. DE-SOC开发板VrilogHDL开发相关部分: (本过程需要Verilog HDL 的基本语言基础) 1.FPGA的发展史及FPGA 的基础架构 2.首先看一下友晶DE ...

- 【lattice软核】ROM的使用

=======================>>>>> 一.ROM核调用:==================>>>>> ======== ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- System Generator 生成IP核在Vivado中进行调用

System Generator 生成IP核在Vivado中进行调用 1.首先在Simulink中搭建硬件模型 2.查看仿真结果 3.资源分析与时序分析 4.启动vivado,关联生成的IP核 5.调 ...

- 【小梅哥SOPC学习笔记】Altera SOPC嵌入式系统设计教程

Altera SOPC嵌入式系统设计教程 第1章 概述 SOPC(System On Programmable Chip,可编程的片上系统)是Altera公司提出来的一种灵活.高效的SOC解决方案.它 ...

随机推荐

- RabbitMQ--windows10环境下的RabbitMQ安装步骤(转)

https://blog.csdn.net/weixin_39735923/article/details/79288578

- 46.Scrapy框架结构

Scrapy的介绍:Scrapy是基于Twisted的异步处理框架,是纯python语言实现的爬虫框架,特点是架构清晰,模块间耦合度低.扩展性强较为灵活. 框架结构如图所示: Engine:引擎,处理 ...

- scp: command not found

scp 不能用? [root@doc]# scp jdk-8u144-linux-x64.tar.gz root@10.10.10.17:/root/ root@10.10.10.17's passw ...

- [PAClient Error] Error: E4356 File does not exist armv7

[PAClient Error] Error: E4356 File does not exist: /Users/tt/PAServer/scratch-dir/Administrator-snIO ...

- Spring中AOP主要用来做什么。Spring注入bean的方式。什么是IOC,什么是依赖注入

Spring中主要用到的设计模式有工厂模式和代理模式. IOC:Inversion of Control控制反转,也叫依赖注入,通过 sessionfactory 去注入实例:IOC就是一个生产和管理 ...

- json.dump和json.dumps区别,json.load和json.loads的区别

dumps是将python类型(list,dict等)转化成str格式,loads是将str转化成python类型(list,dict等). dump和load也是类似的功能,只是与文件操作结合起来了 ...

- pyspider示例代码:解析JSON数据

pyspider示例代码官方网站是http://demo.pyspider.org/.上面的示例代码太多,无从下手.因此本人找出一下比较经典的示例进行简单讲解,希望对新手有一些帮助. 示例说明: py ...

- 获取当前页面url

function getCurrUrl() { var url = ""; if (parent !== window) { try { url = window.top.loca ...

- ES6中的let命令

ES6新增了let命令,用于声明变量.其用法类似var,区别是使用let命令声明的变量只在当前代码块有效. for循环的计数器就很适合使用let命令. var arr= [1,2,3,4,5]; fo ...

- C++11 constexpr常量表达式

常量表达式函数 要求: 函数体内只有单一的return返回语句 例如: constexpr int data() { const int i=1; //含有除了return以外的语句 return i ...