s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)

不同位宽设备的连接

我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的。

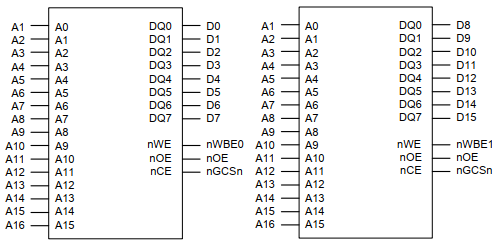

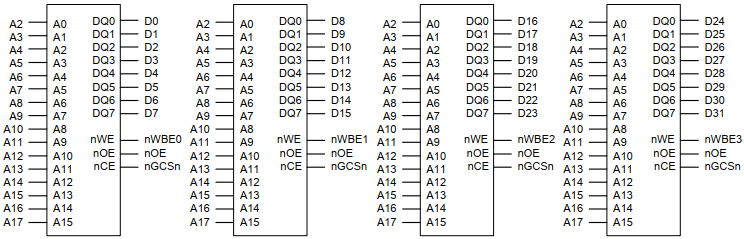

8bit rom与CPU地址线的连接

8bit*2 rom与CPU地址线的连接

8bit*4 rom与CPU地址线的连接

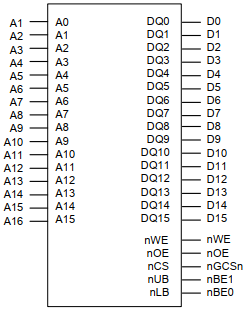

16bit rom与CPU地址线的连接

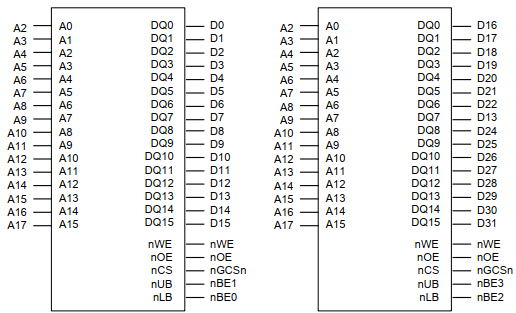

16bit*2 rom与CPU地址线的连接

从上面的图中,我们知道可以对2片位宽为8bit的外设扩展级联成1个16bit的外设,同理可用4片位宽为8bit的外设进行级联成1个32bit的外设...

从上面的图中,我们还看见一个规律:

当外设总线位宽为8bit时, 外设A0接CPU的地址总线ADDR[0],

A[1]->ADDR[1] ...A[15]->ADDR[15]

当外设总线位宽为16bit时,外设A0接CPU的地址总线ADDR[1],

A[1]->ADDR[2] ...A[15]->ADDR[16]

当外设总线位宽为32bit时,外设A0接CPU的地址总线ADDR[2],

A[1]->ADDR[3] ...A[15]->ADDR[17]

那么为什么要这样设计呢?

我们先看一个例子:

假设CPU执行:

MOV R0, #3

LDRB R1, [R0] @ 从内存地址为3的地方,读出一个字节

如图有8bitROM、16bitROM、32bitROM

(1)对于8bitROM ,8bit是一次读写的最小单位,即0地址是第一个8bit,1地址是第二个8bit;

CPU发出地址3,即A0和A1都为1,8bitROM的A0和A1收到的也都是1,

于是找到了ROM上地址为3的8bit数据,包含了我们需要的数据。

(2)对于16bitROM ,16bit是一次读写的最小单位,即0地址是第一个16bit,里面有两个8bit数据;

CPU发出地址3,即A0和A1都为1,16bitROM的A0和A1分别收到的是1和0,

于是找到了ROM上地址为1的16bit数据,包含了我们需要的数据,最后内存控制器再帮我们挑选出所需的8bit数据。

(3)对于32bitROM ,32bit是一次读写的最小单位,即0地址是第一个32bit,里面有四个8bit数据;

CPU发出的地址3,即A0和A1都为0,32bitROM的A0和A1收到的都是0,

于是找到了ROM上地址为0的32bit数据,包含了我们需要的数据,最后内存控制器再帮我们挑选出所需的8bit数据。

用表格更好理解:

| ROM/bit | CPU发出地址 | ROM收到地址 | ROM返回数据 | 内存控制器挑选出数据给CPU |

|---|---|---|---|---|

| 8bit(ROM) | 0b000011 | 0b000011 | 编号3的存储单元中的8数据 | 编号3的存储单元中的8数据 |

| 16bit(ROM) | 0b000011 | 0b000001 | 编号1的存储单元中的16数据 | 根据”A0=1”,挑出低8bit数据 |

| 32bit(ROM) | 0b000011 | 0b000000 | 编号0的存储单元中的32数据 | 根据”A1A0=11”,挑出最低8bit数据 |

结论:

和cpu地址总线相连的外设地址线确定了要访问外设的地址,即哪个存储单元;

然后内存控制器拿到外设存储单元中的数据后,再根据那几个错开的引脚[A1-A0]的值(CPU地址总线没接的那几个引脚的值),来挑出相应的数据给CPU。

再举一个栗子: 假如读取一个32位的数据时

MOV R0, #4

LDR R1, [R0] @去地址4,读取4字节数据

我们知道CPU发出的是32bit地址,那么

对于16bit Rom,内存控制器会给它发2次,rom也会相应的接收2次;

对于8bit Rom,内存控制器给它发4次, rom接收4次,

那么CPU怎么知道它外接的rom位宽是16bit,8bit还是多少...?

当然内存控制器知道了,配置总线位宽寄存器。 如何配置总线位宽寄存器

执行过程如下:

| ROM/bit | CPU发出地址 | ROM收到地址(内存控制器转发给rom) | ROM返回数据 | 内存控制器组装数据给CPU |

|---|---|---|---|---|

| 8bit(ROM) | 0b000100 | 0b000100 | 地址4的一个1byte数据 | 组装地址7、6、5、4数据成4字节数据 |

| 0b000101 | 地址5的一个1byte数据 | |||

| 0b000110 | 地址6的一个1byte数据 | |||

| 0b000111 | 地址7的一个1byte数据 | |||

| 16bit(ROM) | 0b000100 | 0b00010 | 地址2的一个2byte数据 | 组装地址3、2的数据成4字节数据 |

| 0b00011 | 地址3的一个2byte数据 | |||

| 32bit(ROM) | 0b000100 | 0b00001 | 地址1的一个4byte数据 | 直接返回4字节数据 |

怎样确定芯片的访问地址?

1. 根据片选信号确定基地址

2. 根据芯片所接地址线确定范围

| 外设类型 | 接内存控制器的哪个片选 | 基地址 | 占用CPU的地址总线 | 地址范围(offset + size) |

|---|---|---|---|---|

| nor | nGCS0 | 0x0000,0000 | ADDR0-ADDR20 | 0x0000,0000 ~ 0x001f,ffff(2M) |

| dm9000网卡 | nGCS4 | 0x2000,0000 | ADDR0和ADDR2 | 0x2000,0000 ~ 0x2000,0005(5byte) |

| sdram | nGCS6 | 0x3000,0000 | ADDR0-ADDR25 | SDRAM的地址范围 |

这里再次提醒一下,有人发现nor没有和CPU的ADDR0相连接,sdram没有和CPU的ADDR0、ADDR1相连接。不要觉得ADDR0、ADDR1没用到,由于nor数据位宽是16bit,ADDR0是给内存控制器拆分数据用的,同样sdram数据位宽32bit,ADDR0、ADDR1也是给内存控制器拆分数据用的。这个上面已分析过,这也是什么要错位连接的原因。

s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)的更多相关文章

- s3c2440裸机-内存控制器(三、norflash初始化-时序设置)

1.norflash与2440的硬件连接 2.初始化nor,配置nor时序 1.如图是S3C2440的内存控制器的可编程访问周期读写时序,里面的时间参数要根据外部设备的性能进行配置,这里先列出时间参数 ...

- s3c2440裸机-内存控制器(四、SDRAM原理-cpu是如何访问sdram的)

1.SDRAM原理 black (1)SDRAM内部存储结构: (2)再看看与2440连接的SDRAM原理图: sdram引脚说明: A0-A12:地址总线 D0-D15:数据总线(位宽16,2片级联 ...

- s3c2440裸机-内存控制器(五、SDRAM编程实现)

配置内存控制器-SDRAM编程配置 2440内存控制器共有13个寄存器. BANK0--BANK5只需要设置BWSCON和BANKCONx(x为0-5)两个寄存器: BANK6.BANK7外接SDRA ...

- s3c2440裸机-内存控制器(一、内存控制器的原理)

1.内存接口概念 S3C2440是个片上系统,有GPIO控制器(接有GPIO管脚(GPA-GPH)),有串口控制器 (接有TXD RXD引脚),有memory controller内存控制器,有Nan ...

- s3c2440裸机-时钟编程(二、配置时钟寄存器)

s3c2440裸机编程-时钟编程(二.配置时钟寄存器) 1.2440时钟时序 下图是2440时钟配置时序: 1.上电后,nRESET复位信号拉低,此时cpu还无法取指令工作. 2.nRESET复位信号 ...

- s3c2440裸机-UART编程(二、UART编程实现)

UART编程 1.初始化 我们的2440支持3个UART串口,以uart0为例讲解. 那么我们需要实现以下这几个函数完成串口的最基本功能: (1)uart0_init()用于初始化串口 (2)putc ...

- 内存寻址能力与CPU的位宽有关系吗?

答案是:没有关系.CPU的寻址能力与它的地址总线位宽有关,而我们通常说的CPU位宽指的是数据总线位宽,它和地址总线位宽半毛钱关系也没有,自然也与寻址能力无关. 简单的说,CPU位宽指的是一个时钟周期内 ...

- S3C2440—7.存储控制器访问外设

文章目录 一.内存接口的概念 二.存储控制器(内存控制器) 2.1 什么是存储控制器? 2.2 S3C2440存储控制器介绍 2.3 存储控制器如何处理不同位宽的外设 2.4 怎么确定芯片的访问地址? ...

- 十二、S3C2440 裸机 — SDRAM

12.1 SDRAM 介绍 12.1.1 SDRAM 定义 SDRAM(Synchronous Dynamic Random Access Memory):同步动态随机存储器-内存条 同步是指内存工作 ...

随机推荐

- Flutter - flutter desktop embedding / flutter 桌面支持

2019年5月9日,随着谷歌在IO19宣布Flutter支持Web平台,就标志着Flutter已经全面支持所有平台(移动.网页.桌面.嵌入式). 现编一个跨平台小段子: 微软Xarmarin:喵喵喵? ...

- Nlog配置

初次使用nlog,里里外外找了好久,终于搞会了. 使用nlog建日志输出到txt文件.数据库.邮件 nlog配置,如图 码云dome

- js 实现ReplaceAll 的方法

JS 字符串有replace() 方法.但这个方法只会对匹配到的第一个字串替换. 如下例: <HTML> <HEAD> <TITLE> New Document ...

- C# Monitor and transfer or copy the changed or created file to a new location

using System; using System.Collections.Generic; using System.IO; using System.Linq; using System.Tex ...

- Redis 到底是怎么实现“附近的人”这个功能的呢?

作者简介 万汨,饿了么资深开发工程师.iOS,Go,Java均有涉猎.目前主攻大数据开发.喜欢骑行.爬山. 前言:针对“附近的人”这一位置服务领域的应用场景,常见的可使用PG.MySQL和MongoD ...

- python捕捉详细异常堆栈的方法

python中有 try——except 的方法捕获异常,可以获取到异常的种类以及自定义异常, 但是有时候对于debug测试来说,信息不全,比如说 触发异常的具体位置在哪: import traceb ...

- Shell批量SSH免交互登录认证

脚本实现功能:批量或单个SSH免交互登录认证 脚本应用场景:当部署集群时,大多数实现要配置好管理节点与从节点的SSH免交互登录,针对这样的情况,写了下面脚本,简化工作. 脚本支持系统:Ubuntu和C ...

- Codeforces 7E - Defining Macros 题解

目录 Codeforces 7E - Defining Macros 题解 前言 做法 程序 结尾 Codeforces 7E - Defining Macros 题解 前言 开始使用博客园了,很想写 ...

- Community structure enhanced cascade prediction 笔记

目录 一.摘要 二.杂记 三.模型思想 四.实验 五.其他 六.参考文献 一.摘要 深度学习不用去手工提取特征,但是现有深度模型没有在传播预测任务中使用社区结构.所以提出一个CS-RNN框架,把社区在 ...

- tf.InteractiveSession()与tf.Session()的区别

Tensorflow依赖于一个高效的C++后端来进行计算.与后端的这个连接叫做session.一般而言,使用TensorFlow程序的流程是先创建一个图,然后在session中启动它. 这里,我们使用 ...