E203 itcm

E203 itcm是64Kb,所以地址总线为16位,2^16=64Kb, 数据线宽度为64 bits(8 bytes),所以address width是16-3=13bit,ram depth 是2^16/8=2^13。

itcm的基地址默认是0x8000_0000。

在目录e200_opensource/riscv-tools/riscv-tests/isa/generated,这儿有很多生成好的test文件。比如test rv32ui-p-andi

文件rv32ui-p-andi是riscv的可执行elf文件, rv32ui-p-andi.dump是对应的汇编文件,rv32ui-p-andi.verilog是对于的机器码文件,可以在verilog中用下面的代码把要执行的机器码装入itcm中。

//default itcm size is 64Kb, so E203_ITCM_RAM_DP=13

reg [7:0] itcm_mem [0:(`E203_ITCM_RAM_DP*8)-1];

initial begin

$readmemh({testcase, ".verilog"}, itcm_mem); for (i=0;i<(`E203_ITCM_RAM_DP);i=i+1) begin

`ITCM.mem_r[i][00+7:00] = itcm_mem[i*8+0];

`ITCM.mem_r[i][08+7:08] = itcm_mem[i*8+1];

`ITCM.mem_r[i][16+7:16] = itcm_mem[i*8+2];

`ITCM.mem_r[i][24+7:24] = itcm_mem[i*8+3];

`ITCM.mem_r[i][32+7:32] = itcm_mem[i*8+4];

`ITCM.mem_r[i][40+7:40] = itcm_mem[i*8+5];

`ITCM.mem_r[i][48+7:48] = itcm_mem[i*8+6];

`ITCM.mem_r[i][56+7:56] = itcm_mem[i*8+7];

end

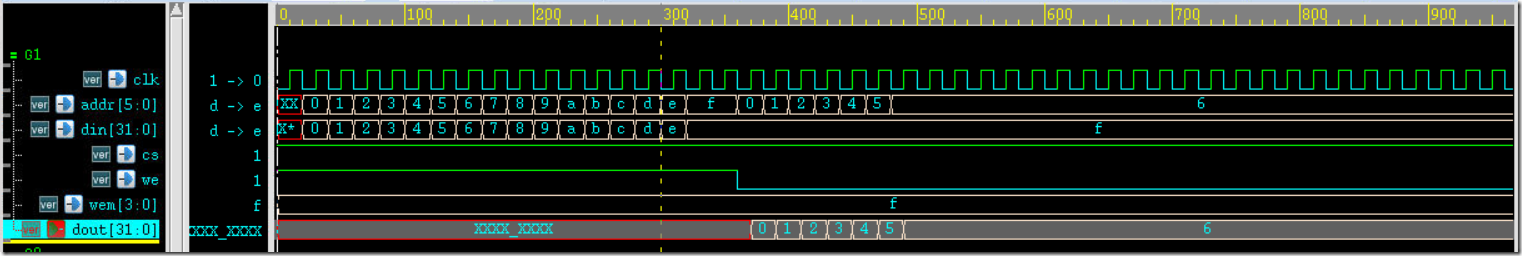

itcm实际上就是一块sram,对itcm的读写如下,读写数据宽度都是按32bit进行的,对于写可以通过write mask只写某个byte。

module sirv_sim_ram

#(parameter DP = 512,

parameter FORCE_X2ZERO = 0,

parameter DW = 32,

parameter MW = 4,

parameter AW = 32

)

(

input clk,

input [DW-1 :0] din,//input data

input [AW-1 :0] addr,//input address

input cs, //chip select

input we, //write enable

input [MW-1:0] wem,//write enable mask

output [DW-1:0] dout //write data out

); reg [DW-1:0] mem_r [0:DP-1];

reg [AW-1:0] addr_r;

wire [MW-1:0] wen;

wire ren; assign ren = cs & (~we);

//it is 4 bits, and every bit mask a byte write

assign wen = ({MW{cs & we}} & wem); genvar i; always @(posedge clk)

begin

if (ren) begin

addr_r <= addr;

end

end generate

for (i = 0; i < MW; i = i+1) begin :mem

if((8*i+8) > DW ) begin: last

always @(posedge clk) begin

if (wen[i]) begin

mem_r[addr][DW-1:8*i] <= din[DW-1:8*i];

end

end

end

else begin: non_last

always @(posedge clk) begin

if (wen[i]) begin

mem_r[addr][8*i+7:8*i] <= din[8*i+7:8*i];

end

end

end

end

endgenerate wire [DW-1:0] dout_pre;

assign dout_pre = mem_r[addr_r]; generate

if(FORCE_X2ZERO == 1) begin: force_x_to_zero

for (i = 0; i < DW; i = i+1) begin:force_x_gen

`ifndef SYNTHESIS//{

assign dout[i] = (dout_pre[i] === 1'bx) ? 1'b0 : dout_pre[i];

`else//}{

assign dout[i] = dout_pre[i];

`endif//}

end

end

else begin:no_force_x_to_zero

assign dout = dout_pre;

end

endgenerate endmodule

testbench文件

module sirv_sim_ram_tb;

reg clk=0;

reg cs=1;

reg we=1;

reg[3:0] wem=4'b1111;

reg[31:0] addr;

reg[31:0] din; wire[31:0] dout;

integer i,j; sirv_sim_ram #(

.FORCE_X2ZERO (1),

.DP (64),

.AW (6),

.MW (4),

.DW (32)

)u_sirv_sim_ram (

.clk (clk),

.din (din),

.addr (addr),

.cs (cs),

.we (we),

.wem (wem),

.dout (dout)

);

always #10 clk = ~clk; initial

begin

for(i=0; i<16; i=i+1)

#20 addr=i;

#20

#20 we = 0;

addr = 0;

#20 addr = 1;

#20 addr = 2;

#20 addr = 3;

#20 addr = 4;

#20 addr = 5;

#20 addr = 6; end initial

begin

for(j=0; j<16; j=j+1)

#20 din=j;

end

initial

begin

//$dumpfile("dump.vcd");

//$dumpvars;

$fsdbDumpfile("dump.fsdb");

$fsdbDumpvars("+all");

end initial

begin

$monitor($time,,,"%d,%d,%d,%d,%d,%d)",cs,din,addr,we,wem,dout);

#1000 $finish;

end

endmodule

E203 itcm的更多相关文章

- E203 CSR rtl实现分析

CSR状态控制寄存器,每个hart都有自己的CSR.对于每个hart,可以配置的状态寄存器是4k.CSR寄存器的功能见:https://www.cnblogs.com/mikewolf2002/p/1 ...

- 蜂鸟E203 IFU模块

E203的IFU(instruction fetch unit)模块主要功能和接口如下: IFU的PC生成单元产生下一条指令的PC. 该PC传输到地址判断和ICB生成单元,就是根据PC值产生相应读指请 ...

- 蜂鸟E203系列——Linux下运行hello world例程

欲观原文,请君移步 创建程序 在 -/hbird-e-sdk-master/software 路径下创建一个"helloworld"中文件夹 在 -/hbird-e-sdk-mas ...

- 蜂鸟E203系列——Linux调试(GDB+Openocd)

欲观原文,请君移步 本文基于文章<蜂鸟E203系列--利用 Hbrid-E-SDK 环境开发程序> GDB 简介 GDB(GNU Project Debugger),是 GNU 工具链中的 ...

- Save ITCM

Debug String if below 64 BYTE it will in DRAM or it will in ITCM So to save ITCM , move it to ALLStr ...

- 童话故事 --- CPU的贴身侍卫ITCM和ICache

"叮铃铃- 叮铃铃-" "谁呀?"黛丝博士打开了家门,"哇,高飞,你怎么来了?" 高飞狗:"好久不见,想来看看你,还买了你最喜欢吃 ...

- 【STM32H7教程】第28章 STM32H7时间关键代码在ITCM执行的超简单方法

完整教程下载地址:http://www.armbbs.cn/forum.php?mod=viewthread&tid=86980 第28章 STM32H7时间关键代码在ITCM执行 ...

- 在vcs中编译及运行测试E203例子

E203的Makefile默认是调用 iverilog编译rtl,我们可以做如下修改,使其支持vcs编译. 1. 首先修改e200_opensource/tb/tb_top.v, 增加dump波形的两 ...

- E203 CSR寄存器

RiscV架构则定义了一些控制和状态寄存器(CSR),用于配置或记录一些运行的状态.CSR寄存器是处理器内核内部的寄存器,使用专有的12位地址编码空间,对一个hart,可以配置4k的CSR寄存器. 蜂 ...

随机推荐

- 什么是DaemonSet

DaemonSet只管理Pod对象,通过nodeAffinity和Toleration两个调度器,保证每个节点上只有一个Pod 集群动态加入了新Node,DaemonSet中的Pod也会添加在新加入N ...

- golang 处理 json 结构体

首先 我们来看一下这个json 字串 { "resp": { ", "respMsg": "成功", "app" ...

- Web前端基础(14):jQuery基础(一)

1. jQuery概述 1.1 为什么要使用jQuery 在用js写代码时,会遇到一些问题: window.onload 事件有事件覆盖的问题,因此只能写一个事件. 代码容错性差. 浏览器兼容性问题. ...

- IDEA激活码

MNQ043JMTU-eyJsaWNlbnNlSWQiOiJNTlEwNDNKTVRVIiwibGljZW5zZWVOYW1lIjoiR1VPIEJJTiIsImFzc2lnbmVlTmFtZSI6I ...

- jQuery从零开始(三)-----ajax

jq当中的ajax技术 $.ajax $.get() $.post() $.load() $.ajax({ url:'请求文件的地址', type:'请求文件使用的方法', data:'向请求的api ...

- Xamarin Bindableproperty 可绑定属性

重要的事情说三遍: 本文基本是取自微软官方 Bindable Properties, 官方也提供了机翻的中文版本,笔者只是尝试用自己的理解描述一遍,便于记忆.如有不对之处,欢迎拍砖. 本文基本是取自微 ...

- form-data、x-www-form-urlencoded、raw、binary的区别(非原创)

文章大纲 一.form-data介绍二.x-www-form-urlencoded介绍三.raw介绍四.binary介绍五.参考文章 一.form-data介绍 http请求中的multipart/f ...

- FLUME NG的基本架构

Flume简介 Flume 是一个cloudera提供的 高可用高可靠,分布式的海量日志收集聚合传输系统.原名是 Flume OG (original generation),但随着 FLume 功能 ...

- IDEA使用svn拉取多模块项目

如果没有安装过svn客户端,安装的时候需要选择安装第二个工具,如下图所示 安装小乌龟, 自行搜索, 注意点是需要选择安装第二个工具 因为默认是不安装的, 而这个组件是集成到IDEA ”必须的” . 如 ...

- SSH的本地、远程、动态端口转发实验笔记

SSH端口转发 SSH 会自动加密和解密所有 SSH 客户端与服务端之间的网络数据.但是,SSH 还能够将其他 TCP 端口的网络数据通过 SSH 链接来转发,并且自动提供了相应的加密及解密服务.这一 ...