FPGA-HPS

最近在做DE1的图像方面实验,用到了HPS,所以简要谈一谈什么是HPS.

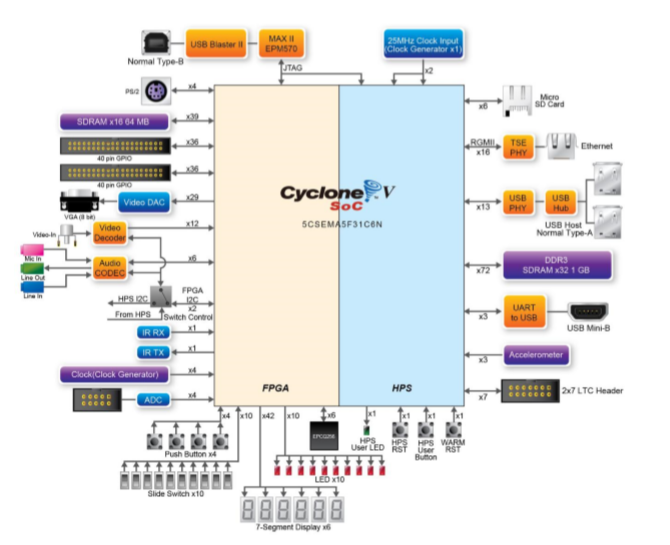

由图可知,DE1的板子就是有fpga+hps组成的;

参考自:http://bbs.eeworld.com.cn/thread-454766-1-1.html

1、HPS:Hard processor system 字面意思就是硬件处理器系统,应该指的是和arm核相连的硬件接口。

2、包括以下内容:

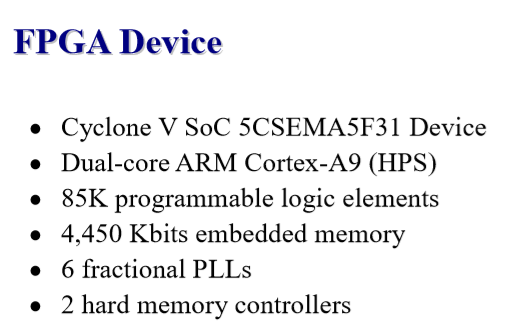

1)Single or dual-core ARM Cortex-A9 MPCore processor-up to 800 MHz maximum frequency with support for symmetric and asymmetric multiprocessing

支持一个或2个ARM Cortex-A9,频率最大能达到800MHz,两个处理器还可以设置成不同的处理速率,这点不知道有什么好处。

2)Interface peripherals —10/100/1000 Ethernet media access control (EMAC), USB 2.0

On-The-GO (OTG) controller, quad serial peripheral interface (QSPI) flash controller,

NAND flash controller, Secure Digital/MultiMediaCard (SD/MMC) controller, UART,

controller area network (CAN), serial peripheral interface (SPI), I2C interface, and

up to 85 HPS GPIO interfaces

接口外设,这个比较好理解,都是常见的arm接口,网口、USB,SPI等等

3)System peripherals —general-purpose timers, watchdog timers, direct memory access

(DMA) controller, FPGA configuration manager, and clock and reset managers

系统外设,这个也比较好理解,就是系统能不运行,而不和外界打交道的,比如定时器,看门狗,DMA控制器等

4) On-chip RAM and boot ROM

片上的RAM和POM,这个还不知道是什么玩意

5)HPS –FPGA bridges —include the FPGA-to-HPS, HPS-to-FPGA, and lightweight

HPS-to-FPGA bridges that allow the FPGA fabric to issue transactions to slaves in

the HPS, and vice versa

这个是比较关键的地方,HPS-FPGA之间的沟通机制

6)FPGA-to-HPS SDRAM controller subsystem —provides a configurable interface to

the multiport front end (MPFE) of the HPS SDRAM controller

接到HPS的SDRAM控制器,应该是和ARM的存储资源有联系

7)ARM CoreSight™ JTAG debug access port, trace port, and on-chip trace storage

这应该说的是调试接口和调试机制

以前的简要介绍

https://www.cnblogs.com/fcfc940503/p/10438350.html

FPGA-HPS的更多相关文章

- 可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构

本周我想进一步探究可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构.我发现了三种主要方式,它们是如何映射并处理通信的,哪些组件需要管控时序并且有访问权限. AXI Bridge 为了能够实现 ...

- 通过HPS控制FPGA端的GPIO

该笔记主要记录HPS端如何通过AXI Bridge控制FPGA端口的GPIO,主要是如何操作FPGA侧的Led 1.AXI Bridge AXIB主要包括H2FB.F2HB.LWH2F ...

- 通过HPS控制FPGA的GPIO

1.学习目的 本例程主要是让 SoC FPGA 初学者了解 HPS/ARM 如何跟 FPGA 交互.“My First HPS-FPGA”工程演示了实现方法的细节.这个工程包括 Quartus II ...

- 关于HPS和FPGA之间的桥接学习笔记一

为了实现FPGA和HPS之间的存储器共享和数据传输,Altera SoC FPGA提供了两种方式用于FPGA和HPS通信.分别是FPGA to SDRAM和AXI bridge. FPGA to SD ...

- HPS端如何通过AXI Bridge控制FPGA端口的GPIO

该笔记主要记录HPS端如何通过AXI Bridge控制FPGA端口的GPIO,主要是如何操作FPGA侧的Led 1.AXI Bridge AXIB主要包括H2FB.F2HB.LWH2F ...

- altera soc体验之旅 FPGA与ARM的窃窃私语

喜大普奔,公司要评估用SOC做产品,我就自然而然的被安排了学习和评估的工作,于是,每天的工作就是开始研究soc了.其实,只要能静下心来学习,一切都还是能够弄出来的. 以前像个无头苍蝇一样到处乱撞, ...

- FPGA在其他领域的应用(一)

测试和测量应用: 测试需要是所有细分市场的要求.无论是终端市场,所有产品在运到最终客户之前都必须进行测试.这动态地驱动测试和测量领域的普遍性质,其中包括下面的种类和分段: 通信测试: 无线测试仪 (W ...

- FPGA开发随笔汇总

点击标题即可进入相关随笔. DE-SOC开发板VrilogHDL开发相关部分: (本过程需要Verilog HDL 的基本语言基础) 1.FPGA的发展史及FPGA 的基础架构 2.首先看一下友晶DE ...

- Altera FPGA SoC搭建步骤

Altera SoC 官方搭建指南: https://rocketboards.org/foswiki/Documentation/EmbeddedLinuxBeginnerSGuide 官方文档中除 ...

随机推荐

- C++-POJ3070-Fibonacci-[矩阵乘法][快速幂]

#include <cstdio> ][];}; ,MOD=1e4; Matrix A,B,O,I; Matrix Mul(Matrix A,Matrix B){ Matrix C=O; ...

- 小sun的假期【牛客】

链接:https://ac.nowcoder.com/acm/contest/1085/A来源:牛客网 应肖老师要求前来更新水一水 题目描述 小 sun 非常喜欢放假,尤其是那种连在一起的长假,在放假 ...

- UVa - 12050 Palindrome Numbers (二分)

Solve the equation: p ∗ e −x + q ∗ sin(x) + r ∗ cos(x) + s ∗ tan(x) + t ∗ x 2 + u = 0 where 0 ≤ x ≤ ...

- .net Core 安装在linux上

1.安装 .net Core 参考官方网站 https://dotnet.microsoft.com/learn/dotnet/hello-world-tutorial/install 2.发布应用程 ...

- 162.扩展User模型-使用Proxy模型

扩展用户模型: Django内置的User模型虽然已经足够强大了,但是有时候还是不能满足我们的需求,比如在验证用户登录的时候,它用的是用户名作为验证,而我们有时候需要通过手机号码或者是邮箱进行验证,还 ...

- SpringBoot学习- 3、整合MyBatis

SpringBoot学习足迹 1.下载安装一个Mysql数据库及管理工具,同类工具很多,随便找一个都可以,我在windows下做测试项目习惯使用的是haosql 它内部集成了MySql-Front管理 ...

- 支持CSS3的高级CSS

一.匹配部分字符串 在CSS2中,可以使用[ href='info.htm' ] 这样的属性选择器来匹配href属性中的字符,但是无法只匹配部分字符串.而CSS3给出了三个新的运算符:^ , $ 和 ...

- python接口自动化测试之http协议(一)

1.http(超文本传输)协议:是一个基于请求与响应模式的.无状态的(不会记住每个请求的状态).应用层协议 2.url详解 https://www.baidu.com/s?ie=utf-8&f ...

- 怎样判断一个exe可执行程序是32位的还是64位的(转)

转载自:https://blog.csdn.net/qq_23308823/article/details/54898119 怎样判断一个exe可执行程序是32位的还是64位的

- python操作mongo实例

# coding:utf-8 """ mongo操作工具 """ from pymongo import MongoClient MONGO ...