每天进步一点点------verilog语言实现的分频

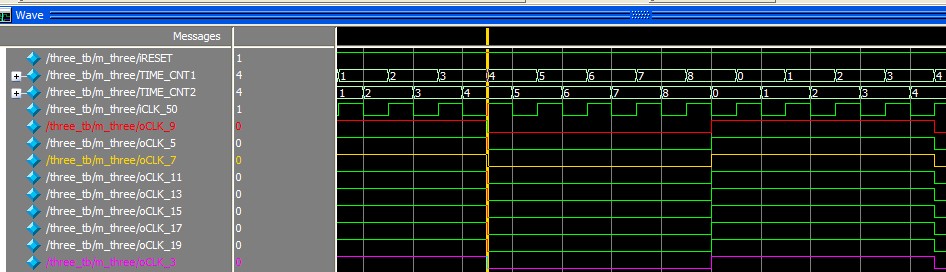

一 、占空比50%的任意奇数分频

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。这种方法可以实现任意的奇数分频。归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。再者同时进行下降沿触发的模N计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

/*********************************************************************************

* Company :

* Engineer : 空气微凉

*

* Create Date : 00:00:00 22/03/2013

* Design Name :

* Module Name :

* Project Name :

* Target Devices :

* Tool versions :

* Description :

* http://www.cnblogs.com/kongqiweiliang/

* Dependencies :

*

* Revision :

* Revision : 0.01 - File Created

* Additional Comments :

********************************************************************************/

`timescale 1ns/1ps

`define UD #

/*******************************************************************************/

module three

(

//system interface

input iCLK_50 ,//50MHz

input iRESET ,//system interface

//Interface package

output oCLK_3 ,//

output oCLK_5 ,//

output oCLK_7 ,//

output oCLK_9 ,//

output oCLK_11 ,//

output oCLK_13 ,//

output oCLK_15 ,//

output oCLK_17 ,//

output oCLK_19 //

//hardware interface

);

//-------------------------------------------------------------------------------

parameter N = ; reg [:] TIME_CNT1,TIME_CNT1_N;

reg [:] TIME_CNT2,TIME_CNT2_N; always@(posedge iCLK_50 or negedge iRESET)begin

if(!iRESET)

TIME_CNT1 <= 'h0;

else

TIME_CNT1 <= TIME_CNT1_N;

end

always@(*)begin

if(TIME_CNT1 == N - )

TIME_CNT1_N = 'h0;

else

TIME_CNT1_N = TIME_CNT1 + 'h1;

end always@(negedge iCLK_50 or negedge iRESET)begin

if(!iRESET)

TIME_CNT2 <= 'h0;

else

TIME_CNT2 <= TIME_CNT2_N;

end

always@(*)begin

if(TIME_CNT2 == N - )

TIME_CNT2_N = 'h0;

else

TIME_CNT2_N = TIME_CNT2 + 'h1;

end assign oCLK_3 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_5 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_7 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_9 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_11 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_13 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_15 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_17 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

assign oCLK_19 = (TIME_CNT1 < ((N - )/)) | (TIME_CNT2 < ((N - )/));

//-------------------------------------------------------------------------------

endmodule

/*********************************************************************************

* Company :

* Engineer : 空气微凉

*

* Create Date : 00:00:00 22/03/2013

* Design Name :

* Module Name :

* Project Name :

* Target Devices :

* Tool versions :

* Description :

* http://www.cnblogs.com/kongqiweiliang/

* Dependencies :

*

* Revision :

* Revision : 0.01 - File Created

* Additional Comments :

********************************************************************************/

`timescale 1ns/100ps

`define UD #

/*******************************************************************************/

module three_tb();

//-------------------------------------------------------------------------------

//system interface

reg iSYSCLK ;

reg iRESET ;

//Interface package

wire oCLK_3 ;

wire oCLK_5 ;

wire oCLK_7 ;

wire oCLK_9 ;

wire oCLK_11 ;

wire oCLK_13 ;

wire oCLK_15 ;

wire oCLK_17 ;

wire oCLK_19 ;

//hardware interface

//-------------------------------------------------------------------------------

//测试实例设计

//-------------------------------------------------------------------------------

initial begin

iRESET = ;

iSYSCLK = ;

#

iRESET = ;

iSYSCLK = ;

end always # iSYSCLK = ~iSYSCLK ; //-------------------------------------------------------------------------------

//例化被测试工程

//-------------------------------------------------------------------------------

three m_three

(

//system interface

.iCLK_50 (iSYSCLK ),//50MHz

.iRESET (iRESET ),//system interface

//Interface package

.oCLK_3 (oCLK_3 ),//

.oCLK_5 (oCLK_5 ),//

.oCLK_7 (oCLK_7 ),//

.oCLK_9 (oCLK_9 ),//

.oCLK_11 (oCLK_11 ),//

.oCLK_13 (oCLK_13 ),//

.oCLK_15 (oCLK_15 ),//

.oCLK_17 (oCLK_17 ),//

.oCLK_19 (oCLK_19 ) //

//hardware interface

);

//*******************************************************************************

endmodule

二 、任意占空比的任意分频

FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。很容易想到用计数的方式来分频:50000000/880 = 56818。显然这个数字不是2的整幂次方,那么我们可以设定一个参数,让它到56818的时候重新计数就可以实现了。程序如下:

module div(clk, clk_div); input clk; output clk_div; reg [:] counter; always @(posedge clk) if(counter==) counter <= ; else counter <= counter+; assign clk_div = counter[]; endmodule

下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter为0到32767的时候为低,在32768到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么我们需要再设定一个参数,使它为56817的一半,使达到它的时候波形翻转,就可以实现结果了。程序如下:

module div(clk, clk_div);

input clk;

output clk_div;

reg [:] counter;

always @(posedge clk)

if(counter==) counter <= ;

else counter <= counter+;

reg clk_div;

always @(posedge clk)

if(counter==) clk_div <= ~clk_div;

endmodule

继续让我们来看如何实现任意占空比,比如还是由50 M分频产生880Hz,而分频得到的信号的占空比为30%。 56818×30%=17045

module div(clk,reset,clk_div,counter); input clk,reset; output clk_div; output [:] counter; reg [:] counter; reg clk_div; always @(posedge clk) if(!reset) counter <= ; else if(counter==) counter <= ; else counter <= counter+; always @(posedge clk) if(!reset) clk_div <= ; else if(counter<) clk_div <= ; else clk_div <= ; endmodule

每天进步一点点------verilog语言实现的分频的更多相关文章

- 【iCore、iCore2 双核心板】EPCS 实验(SPI Flash)(基于Verilog语言)

_____________________________________ 深入交流QQ群: A: 204255896(1000人超级群,可加入) B: 165201798(500人超级群,满员) C ...

- 基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用

在电力电子变流器设备中,常常需要计算发电量,由于电力电子变流器设备一般是高频变流设备,所以发电量的计算几乎时实时功率的积分,此时就会用到一个积分模块.发电量计算的公式如下:Q=∫P. FPGA由于其并 ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- Verilog语言:还真的是人格分裂的语言

人气腹语术师天愿在现场披露了被人偶搭档夺取灵魂的腹语术师将妻子杀害的表演节目.天愿真的陷入了多重人格,命令自己杀害妻子和子的人偶的人格出现了.为了不(让自己)杀害和弟子登川有外遇的妻子,天愿提出委托想 ...

- Verilog 语言 001 --- 入门级 --- 编写一个半加器电路模块

Verilog 语言编写一个 半加器 电路模块 半加器 的电路结构: S = A 异或 B C = A 与 B 1. 程序代码 module h_adder (A, B, SO, CO); input ...

- FPGA基础(verilog语言)——语法篇

verilog语言简介 verilog语言是一种语法类似于c的语言,但是与c语言也有不同之处,比如: 1.verilog语言是并行的,每个always块都是同时执行,而c语言是顺序执行的 2.veri ...

- 从RTL视图到Verilog语言-转可乐豆原创

从RTL视图到Verilog语言 曾经听过某位大牛都说:“当你的学习FPGA到一个境界的时候,你看到的硬件描述语言,将不再是单纯的语言,而是由一个个逻辑门组成的电路图,一旦达到这个境界,方能把代码写到 ...

- 每天进步一点点------Verilog 测试平台(Testbench) (一)

每天进步一点点------Verilog 测试平台(Testbench) (一)

- Verilog语言中的系统任务和系统函数

Verilog语言中预先定义了一些任务和函数,用于完成一些特殊的功能,它们被称为系统任务和系统函数,这些函数大多数都是只能在Testbench仿真中使用的,使我们更方便的进行验证. `timescal ...

随机推荐

- PAT (Basic Level) Practice (中文)1031 查验身份证 (15 分)

一个合法的身份证号码由17位地区.日期编号和顺序编号加1位校验码组成.校验码的计算规则如下: 首先对前17位数字加权求和,权重分配为:{7,9,10,5,8,4,2,1,6,3,7,9,10,5,8, ...

- 前端页面中:jsp和HTML的区别之处

JSP和HTML的区别 HTML页面是静态页面,也就是事先由用户写好放在服务器上,固定内容,不会变,由web服务器向客户端发送,平时上网看的网页都是大部分都是基于html语言的. JSP页面是有JSP ...

- C#的结构和数组

下面我们继续学习C#的语法.结构struct,C#中的结构和我们PLC中建立的UDT(结构体)是一样的.里面存储了相关的不同类型的数据. 有一句话我觉得十分重要:方法是依存于结构和对象存在的.这以后我 ...

- HTML5 表单学习

创建表单的方法: 用form标签 form标签常用元素:input:单行表单.select:下拉式表单.textarea:多行文本域 input元素的type属性:text:文本属性.checkbox ...

- 小程序y轴拖动

需求场景 小程序在y轴方向 拖动 一小段距离 解决方案 1.监听 元素 2.绑定 点击 和 移动 事件 3.数据处理 代码 <view animation="{{item.animat ...

- 《深入理解java虚拟机》读书笔记八——第九章

第九章 类加载及执行子系统的案例与实战 Q:如果有10个WEB应用程序都是用Spring来进行组织管理的话,可以把Spring放到Common或Shared目录下(Tomcat5.0)让这些程序共享. ...

- php私有组件以及创建自己的composer私有组件(packagist+git+composer)

1.私有组件 大多数时候我们使用的都是公开可用的开源组件,但有时候如果公司使用内部开发的PHP组件,而基于许可证和安全方面的问题不能将其开源,就需要使用私有组件.对Composer而言,这是小菜一碟. ...

- 记录 Docker 的学习过程 (网络篇)

打开2个会话,分别运行以下命令 # docker run -it -P --name nginx2 nginx #-P 端口随机映射 再打开一个会话查看 运行中的容器 # docker ps -aCO ...

- BK: Data mining: concepts and techniques (1)

Chapter 1 data mining is knowledge discovery from data; The knowledge discovery process is an iterat ...

- RabbitMQ+PHP教程

RabbitMQ+PHP 教程一(Hello World) RabbitMQ+PHP 教程二(Work Queues) RabbitMQ+PHP 教程三(Publish/Subscribe) Rabb ...