DUAL PORT RAM应用实例

作者:桂。

时间:2018-05-14 12:11:00

链接:http://www.cnblogs.com/xingshansi/p/9035522.html

前言

主要是Xilinx 常用模块汇总(verilog)【03】中双端口RAM的细节补充,限于篇幅,单独列出。

一、双端口RAM简述

具体细节参考ug473_7Series_Memory_Resources.pdf.

这里直接调用IP核。

二、IP核参数简述

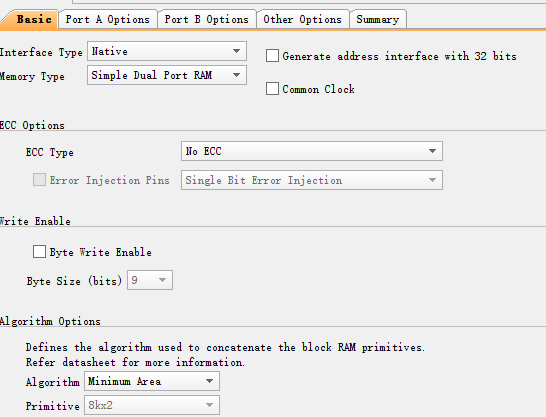

A-Page1

- Common Clock:同源时钟

- Generate adderss..:默认32bit地址,否则根据深度自动调节

- ECC:纠错

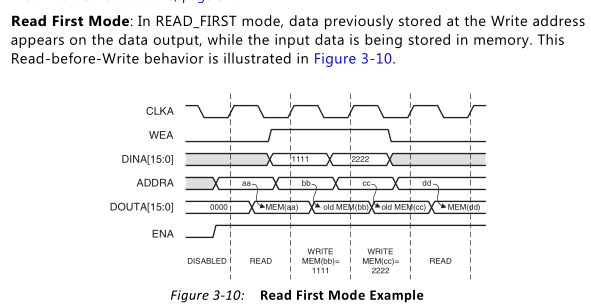

- Read First Operating Mode is supported when the Common Clock option is selected.

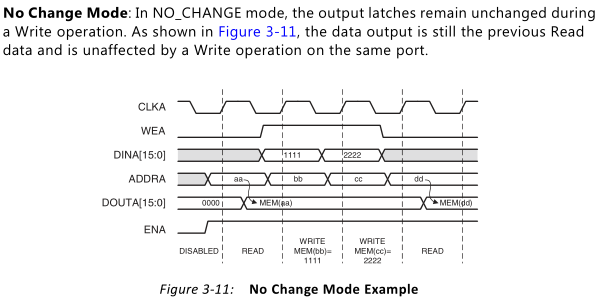

- no change mode

这里使用,通常选择no change mode。

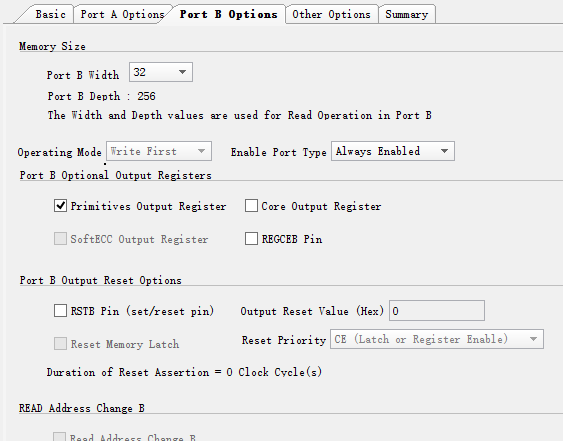

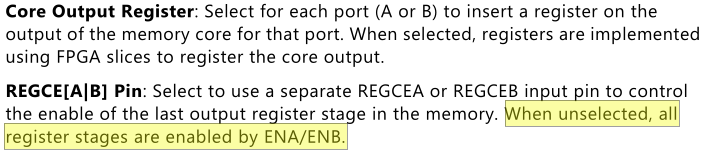

C-Page3

在输出添加一个锁存器,即多延1拍,保证时序良好。

D-Page4

三、仿真验证

任务要求【简化】:

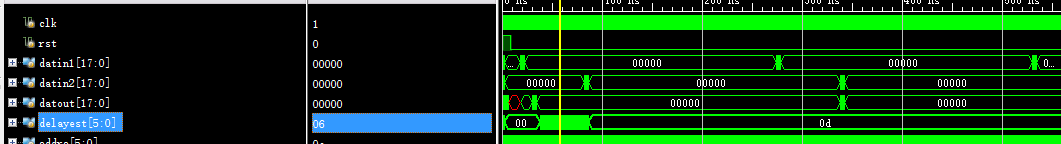

两路周期为64clocks【对应最大延迟数】的数据链,相差delay clocks,现在需要用DUAL PORT RAM进行对齐处理。

思路分析:

1)选1路为参考,一路进入DUAL PORT RAM修正;

2)修正思路:对于脉冲信号,信号高为有效->判断延拍数—>根据延拍数进行地址偏移->输出对齐的数据。

Testbench:

`timescale 1ns / 1ps

/*

Function: DPRAM for data aligned

Author: Gui.

Data: 2018年5月14日12:49:07

*/

module dpram_tb;

//parameter

//parameter datwidth = 18;

parameter delay = ;

parameter start = ;

//port

logic clk,rst;

logic [:] datin1;

logic [:] datin2;

logic [:] datout;

logic [:] addra, addrb, counter, delayest;

logic [:] flag;//FSM

//initial

initial begin

clk = ;

rst = ;

#

rst = ;

#

$stop;

end always # clk = ~clk; always @(posedge clk)

begin

if(rst) begin

datin1 <= ;

datin2 <= ;

counter <= ;

end

else begin

counter <= counter+;

if(counter == start)

begin

datin1 <= {'b1,17'b0};

end

else begin

datin1 <= ;

end

if (counter == (start + delay ))

begin

datin2 <= {'b1,17'b0};

end

else begin

datin2 <= ;

end

end

end //flag control

always @(posedge clk)

begin

if(rst)

begin

delayest <= ;

addra <= ; //for primitive output register

addrb <= ;

flag <= ;

end

else begin

if (flag == 'b00)

begin

if(datout[])

begin

delayest <= ;

flag <= 'b01;

end

end

if (flag == 'b01)

begin

delayest <= delayest + ;

end

if ((flag == 'b01) & datin2[17])

begin

flag <= 'b10;

end

if (flag == 'b10)

begin

addra <= addra + delayest + ;

flag <= 'b11;//next flag state

end

else begin

addra <= addra + ;

end

addrb <= addrb + ;

end

end

//IP

blk_mem_gen_0 uut(

.clka(clk),

.wea('b1),

.addra(addra),

.dina(datin1),

.clkb(clk),

.addrb(addrb),

.doutb(datout)

); endmodule

datout是datin1的修正,可见datin1修正后的结果—>datout 已经与datin2对齐。

DUAL PORT RAM应用实例的更多相关文章

- Xilinx ISE 14.1中模拟True Dual Port RAM例子

<一>创建工程 创建工程在此略过. <二>基本代码 1.创建一个Verilog modual代码如下: module main( input clk, input rsta, ...

- AHB总线RAM Verilog实例

//*************************************************************************** // Copyright(c)2017, L ...

- Xilinx 常用模块汇总(verilog)【03】

作者:桂. 时间:2018-05-10 2018-05-10 21:03:44 链接:http://www.cnblogs.com/xingshansi/p/9021919.html 前言 主要记 ...

- 单双口RAM

// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// singl ...

- RAM建模和初始化

冯诺依曼提出的存储计算,计算存储,因此,几乎所有的CPU和ASIC都会使用存储器,它们的类型很多,包括异步RAM.同步RAM.ZBT RAM.DDR DRAM.ROM等.由于大部分的异步RAM和SRA ...

- [RAM] FPGA的学习笔记——RAM

1.RAM——随机存取存储器, 分为SRAM和DRAM. SRAM:存和取得速度快,操作简单.然而,成本高,很难做到很大.FPGA的片内存储器,就是一种SRAM,用来存放程序,以及程序执行过程中,产生 ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- IP核——RAM

一.Quartus 1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager 2.弹出创建页面,选择Creat a new custom megafunc ...

- Vivado的helloword计划(一个):硬件project部分

硬件平台:ZedBoard 软件平台:vivado2013.3 本演示样例通过综合.实现,生成比特流,发送到SDK实现. 启动vivado而且创建一个项目 依据提示操作一步步创建新项目的时候记得选择R ...

随机推荐

- Codeforces 442C Artem and Array (看题解)

Artem and Array 经过分析我们能发现, 如果对于一个a[ i ] <= a[ i + 1 ] && a[ i ] <= a[ i - 1 ]可以直接删掉. 最 ...

- gitbook editor教程

用户首先需要安装 nodejs,以便能够使用 npm 来安装 gitbook.所以我们先安装node.js,安装过程很简单,都是不断按下「Next」按钮就可以了 写node -h可以看看是否安装成功 ...

- See you~ HDU1892

一开始还离散化弄了好久 离散化细节弄得好差 这题用二维树状数组做很快 因为树状数组下标不为0 所以所有下标要加一处理 还有就是算矩阵的时候要处理两个坐标的大小关系 个人感觉树状数组用for语句写 ...

- 8. 博客系统| 富文本编辑框和基于bs4模块防御xss攻击

views.py @login_required def cn_backend(request): article_list = models.Article.objects.filter(user= ...

- 各种浏览器下的页面元素xpath获取方法

参考链接: http://blog.sina.com.cn/s/blog_654c6ec70100v1i2.html

- 解决linux下“XX不在 sudoers 文件中。此事将被报告"的问题

在使用sudo命令时,经常性会提示出“不在 sudoers 文件中.此事将被报告”的错误信息. 这是因为当前登录的账号不在sudo权限里面. sudo命令可以让你以root身份执行命令,来完成一些我们 ...

- Java设计模式从精通到入门一 责任链模式

一直都想对设计模式有一个深刻的认识,这样对于阅读源码的时候就不会那么吃力了.于是有了想要记录下设计模式的笔记.打算从自己不怎么熟悉的设计模式开始写,里面穿插着一点自己的想法,希望自己写完后,会又一 ...

- JVM调优总结 -Xms -Xmx -Xmn -Xss(转)

堆大小设置JVM 中最大堆大小有三方面限制:相关操作系统的数据模型(32-bt还是64-bit)限制:系统的可用虚拟内存限制:系统的可用物理内存限制.32位系统下,一般限制在1.5G~2G:64为操作 ...

- java中线程安全的map是ConcurrentHashMap

原理:http://www.cnblogs.com/ITtangtang/p/3948786.html 与hashtable的区别: http://blog.csdn.net/songfeihu08 ...

- dataGridView使用指南系列一、回车换行或换列完美解决方案

在使用datagridview控件时,默认按回车是跳转到下一行的当前列的,要想让按回车跳转到同一行的下一列该怎么做呢? 百度搜索了一下,大都是使用该控件的key_down事件和CellEndEdit进 ...