Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真

Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真

Author:zhangxianhe

新建工程

打开Vivado软件,直接在欢迎界面点击Create New Project,或在开始菜单中选择File - New Project即可新建工程。

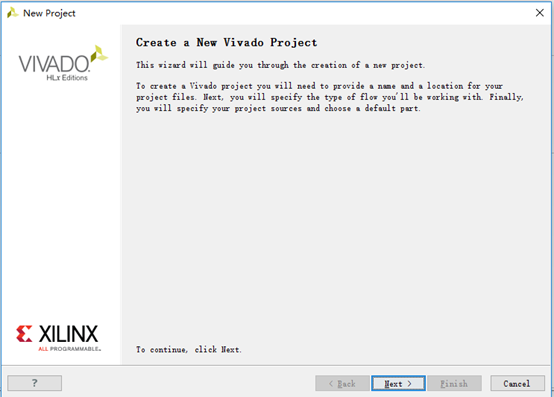

点击Next;

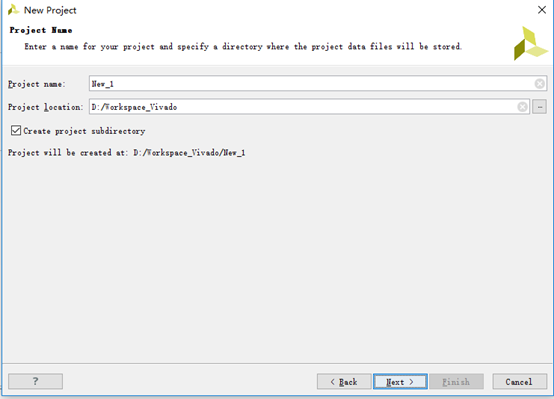

输入工程名称和路径。

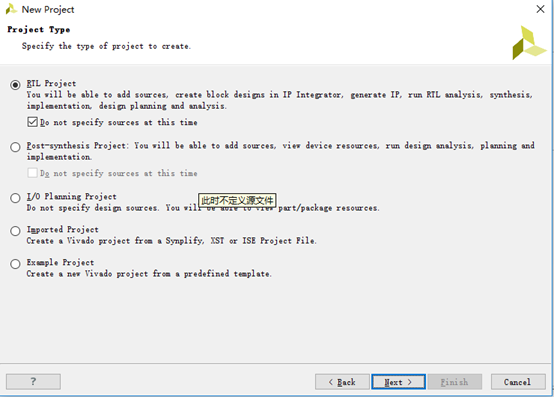

选择RTL Project,勾选Do not specify sources at this time(这样可以跳过添加源文件的步骤,源文件可以后面再添加)。

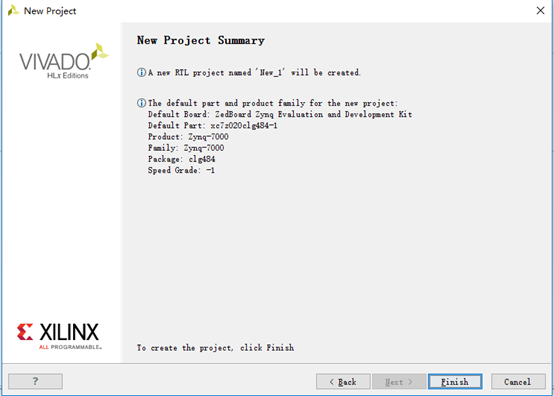

直接选择Boards,然后选择Zedboard Zynq Evaluation and Development Kit 硬件开发包。

点击Next,再点击Finish,项目新建完成

添加Verilog设计文件(Design Source)

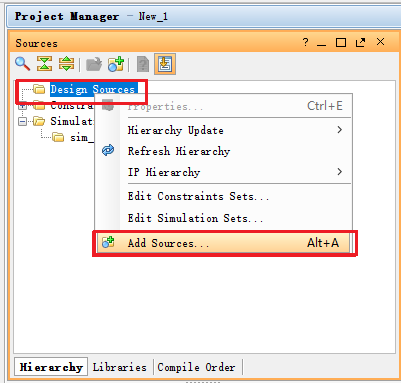

在Project Manager窗口中,右击选择Design Sources,在空白处或任意文件夹上右击,选择Add Sources。

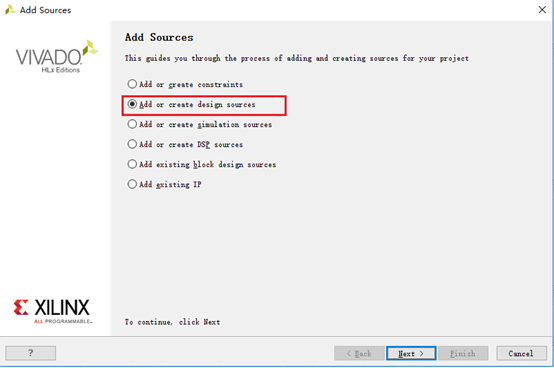

选择Add or Create Design Sources,点击Next。

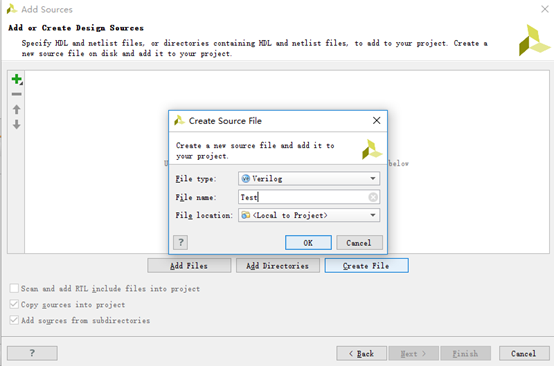

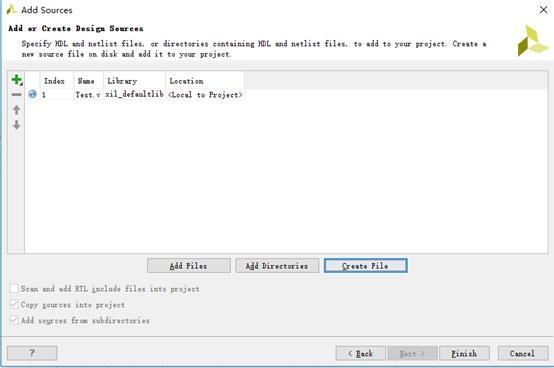

点击Create File按钮,弹出的小窗口中输入文件名,点击OK。

可以一次性新建或添加多个文件,最后点击Finish。

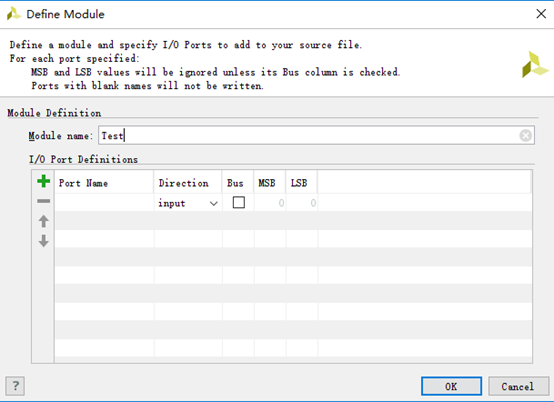

稍后会弹出定义模块的窗口,也就是刚刚添加的test文件。可以在这里设置test模块的输入输出端口;或者直接点击OK,稍后再自行编写。

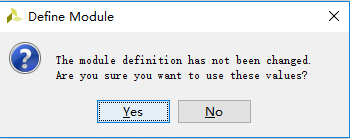

点击OK后,如果弹出下面窗口直接点击Yes。

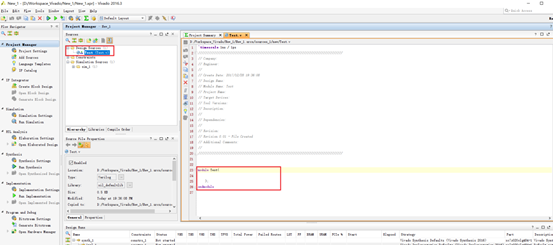

test文件和对应的模块即创建完成,如下图。

添加Verilog仿真文件(Simulation Source)

操作和上一步添加Verilog设计文件基本一致,唯一的区别是选择Add or Create Simulation Sources。新建一个名为simu的仿真文件。

设计文件新建完成后,在Design Sources和Simulation Sources中都有,而仿真文件只会出现在Simulation Sources文件夹中。设计文件可以用于仿真,也可以用于最终烧写进开发板,而仿真文件仅用于仿真。

编写代码

打开设计test模块,编写代码实现一个如下。

module Test(a,b,c,d,e);// 模块接口

input [:] a; // 输入信号a

input [:] b; // 输入信号b

input [:] c; // 输入信号c

input [:] d; // 输入信号d

output[:] e; // 求和输出信号

wire [:]outa1,outa2; // 定义输出网线型

assign e = outa2+outa1; // 把两部分输出结果合并

/*

通常,我们模块的调用写法如下:

被调用的模块名字- 自定义的名字- 括号内信号

这里比如括号内的信号,.ina(ina1)

这种写法最常用,信号的顺序可以调换

*/

adder myadder1 (.ina(a),.inb(b),.outa(outa1));

// 调用adder 模块,自定义名字为myadder1

adder myadder2 (.ina(c),.inb(d),.outa(outa2));

// 调用adder 模块,自定义名字为myadder2

endmodule

//adder 子模块

module adder(ina,inb,outa );// 模块接口

input [:] ina; // ina-输入信号

input [:] inb; // inb-输入信号

output [:] outa; // outa-输入信号

assign outa = ina + inb; // 求和

// 模块结束

endmodule

行为仿真(Behavioral Simulation)与Testbench

为了验证代码是否正确,可以对代码进行行为仿真。行为仿真时,输入信号可以使用Testbench编写。

如果直接修改test模块,在其中添加Testbench代码,再进行仿真,是一种不太正确的做法。因为test模块是设计文件,后面可能会直接烧写进板子。进行仿真时添加了Testbench代码,之后再烧写进板子又得删掉Testbench代码,这样容易出现错误,而且操作起来也比较麻烦。尤其是接口数量多,内部比较复杂的模块。

所以我们将Testbench代码全部写到仿真文件simu中,并在simu文件中调用test模块,从而进行仿真。

编写仿真代码

在simu模块中编写代码如下:

module simu();

reg [:] a;

reg [:] b;

reg [:] c;

reg [:] d;

wire[:] e;

reg [:] i; //中间变量

// 调用被仿真模块模块

Test myTest (.a(a), .b(b),.c(c),.d(d),.e(e));

initial begin // initial是仿真用的初始化关键词

a=;b=;c=;d=; // 必须初始化输入信号

for(i=;i<;i=i+) begin

# ;

a = i;

b = i;

c = i;

d = i;

end // 给是输入信号a 赋值

end

initial begin

$monitor($time,,,"%d + %d + %d + %d ={%d}",a,b,c,d,e); // 信号打印输出

# $finish;

end

endmodule

代码说明:

Test myTest (.a(a), .b(b),.c(c),.d(d),.e(e))调用了前面写好的Test模块,其中myTest是模块名称, Test为类名,而myTest为对象名称。同样,Verilog中调用模块时,可以实例化多个Test对象。

行为仿真

右击simu模块,选择Set as Top,将simu模块设置为仿真时的顶层模块。顶层模块类似于C编程时的入口函数,即main函数。main`函数可以调用其他子函数;类似的,顶层模块可以调用其他模块。(或保持默认设置,即如果没有将仿真模块设置为顶层文件时,执行此操作)。

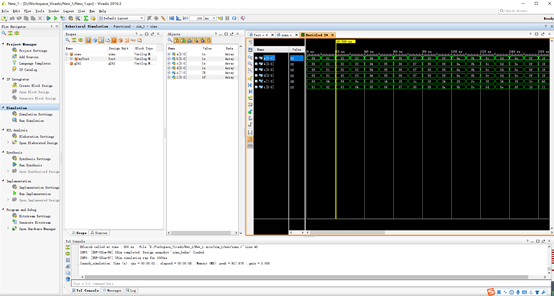

在Flow Navigator窗口中点击Run Simulation - Run Behavioral Simulation;或者在菜单中选择Flow - Run Simulation - Run Behavioral Simulation,即可启动行为仿真。

稍后Behavioral Simulation窗口打开,即可看到输出的仿真波形。

操作技巧

双击图中右侧的Untitled 2标签,可以最大化仿真波形窗口。在波形窗口按住Ctrl键并滚动鼠标滚轮,可以横向缩放波形;按住Shift并滚动鼠标滚轮,可以横向平移波形。

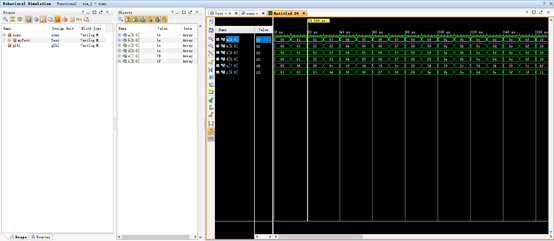

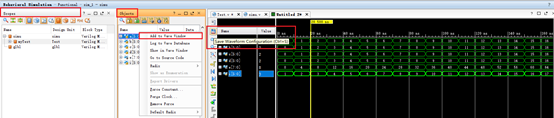

在Behavioral Simulation窗口中的Scopes子窗口,根据模块调用关系选中myTest,在右侧的Objects窗口即可看到test模块中所有的信号。右击信号,选择Add To Wave Window,可将波形添加到右侧的仿真波形窗口,保存仿真文件,再次仿真时就可以看到该信号的波形。

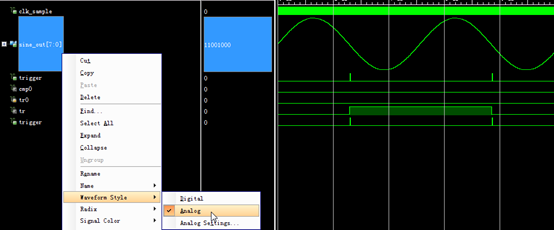

对于一些输出数字信号波形的情况,例如让reg [7:0] sine_out输出正弦波,仿真后右击信号,选择Waveform Style - Analog,即可以波形的形式查看信号。如图显示的就是正弦波信号(注意这里信号本身还是数字信号,并不是模拟信号,只是用软件显示出了其幅值随时间变化的波形)。

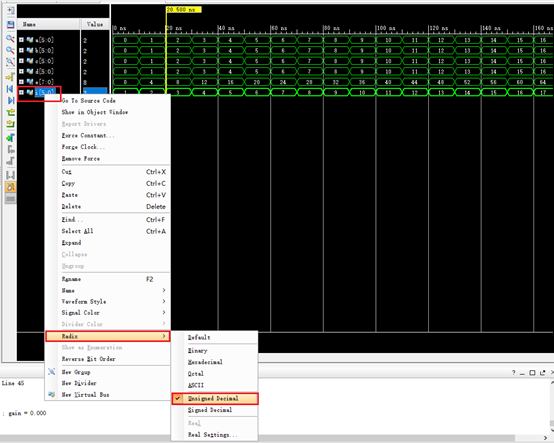

对于多位信号例如wire [7:0] p,默认使用二进制形式显示,可以根据需要修改。例如右击选择Radix - Unsigned Decimal即可设置为无符号十进制显示,如图。

如有疑问,请联系447574829@qq.com,欢迎FPGA爱好者。

之前,详细写了一系列关于Vivado SDK FPGA的教程。这个系列会不断更新,欢迎订阅查看。

Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真的更多相关文章

- xilinx Vivado的使用详细介绍(2):创建工程、添加文件、综合、实现、管脚约束、产生比特流文件、烧写程序、硬件验证

xilinx Vivado的使用详细介绍(2):创建工程.添加文件.综合.实现.管脚约束.产生比特流文件.烧写程序.硬件验证 Author:zhangxianhe 新建工程 打开Vivado软件,直接 ...

- Xilinx Vivado的使用详细介绍(3):使用IP核

ilinx Vivado的使用详细介绍(3):使用IP核 Author:zhangxianhe IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器.除法器.浮点运算 ...

- Xilinx Vivado的使用详细介绍(4):Zedboard+vivado之流水灯(加SDK)

Vivado+zedboard之初学流水灯 Author:zhangxianhe 环境:vivado 2016.3(已验证适用于2015.4) 开发板:Zedboard version xc7z020 ...

- Xilinx Vivado的使用详细介绍(2):综合、实现、管脚分配、时钟设置、烧写

前面一篇介绍了从新建工程一直到编写代码进行行为仿真,这篇继续进行介绍. 修改器件型号 新建工程时选择过器件型号,如果新建好工程后需要修改型号,可以选择菜单Tools - Project Setting ...

- Xilinx Vivado的使用详细介绍(5):调用用户自定义封装的IP核

Zedboard OLED Display Controller IP v1 介绍 Author:zhangxianhe 本文档提供了快速添加,连接和使用ZedboardOLED v1.0 IP内核的 ...

- 关联容器:unordered_map详细介绍(附可运行代码)

介绍 1 特性 2 Hashtable和bucket 模版 1 迭代器 功能函数 1 构造函数 12示例代码 2 容量操作 21 size 22 empty 3 元素操作 31 find 32 ins ...

- CCS V5 使用教程二:创建工程和配置软件仿真

新建CCS项目 选择File/New/CCS Project: 新建项目对话框 1) Project name: 指项目名称,这里要注意的项目名称不区分大小写. 2) Ou ...

- Xamarin iOS编写第一个应用程序创建工程

Xamarin iOS编写第一个应用程序创建工程 在Xcode以及Xamarin安装好后,就可以在Xamarin Studio中编写程序了.本节将主要讲解在Xamarin Studio中如何进行工程的 ...

- 72.xilinx vivado zynq vdma仿真及应用详解(一)

很多人用zynq平台做视频图像开发,但是对vdma了解比较少,上手起来稍微有些困难,我针对这一现象,做了一个基于vivado和modelsim的仿真和应用测试工程,并写篇文章做些介绍,希望能对大家有帮 ...

随机推荐

- 使用Apache JMeter对SQL Server、Mysql、Oracle压力测试(三)

接第二篇写 第四步,测试Oracle数据库的性能. a.加载JDBC Oracle驱动,添加线程组和线程属性和前面两部一样,如果有需要可以往前翻看. b.设置JDBC Connection Oracl ...

- Java基础之数组详解

数组对于每一门编程语言来说都是重要的数据结构之一,当然不同语言对数组的实现及处理也不尽相同. Java 语言中提供的数组是用来存储固定大小的同类型元素. 你可以声明一个数组变量,如 numbers[1 ...

- 浅谈Linux文件与目录权限

作为一个程序员,在工作的过程中或多或少都会接触都Linux,那么对于权限这块肯定有所了解,今天有空想谈谈觉得比较绕的权限问题,即文件权限与目录权限 1.文件权限,对于文件权限这个是比较简单的,也很容易 ...

- 《ASP.NET Core In Action》读书笔记系列一 ASP.NET Core 的诞生

最近打算系统学习一下asp.net core ,苦于没有好的中文书藉,只好找来一本英文的 <ASP.NET Core In Action>学习.我和多数人一样,学习英文会明显慢于中文.希 ...

- qt手写输入法资料

论文: https://max.book118.com/html/2015/1229/32204490.shtm 开源库: zinna Linux下使用的Tegaki就是使用的这个库 csdn博客资料 ...

- PyTorch in Action: A Step by Step Tutorial

PyTorch in Action: A Step by Step Tutorial PyTorch in Action: A Step by Step Tutorial Installation ...

- Net Core API网关Ocelot

Ocelot在github的地址 https://github.com/TomPallister/Ocelot , 非常给力的是在课程当天完成了.NET Core 2.0的升级,升级过程请看https ...

- python画手绘图

第一步:插入代码 #e17.1HandDrawPic.py from PIL import Image import numpy as np vec_el = np.pi/2.2 # 光源的俯视角度, ...

- Holer下载

Holer下载 经常使用开源的holer将本地的应用映射到公网上访问,本文介绍如何下载holer软件包和注意事项,以及相关的帮助文档. 1. Java版本的holer软件包 格式: holer-cli ...

- redis的数据持久化策略

redis提供了两种不同的持久化方法来将数据存储到硬盘里面.一种方法叫快照,它可以将存在于某一时刻的所有数据都写入硬盘里面.另一种方法叫只追加文件(AOF),它会在执行写命令时,将被执行的写命令复制到 ...