s3c6410_MMU地址映射过程详述

参考:

1)《ARM1176 JZF-S Technical Reference Manual》:

Chapter 3 System Control Coprocessor

Chapter 6 Memory Management Unit

2)u-boot源码:

u-boot-x.x.x/cpu/s3c64xx/start.S

u-boot-x.x.x/board/samsung/smdk6410/lowlevel_init.S

1. ARMv6 MMU简述

1)MMU由协处理器CP15控制;

2)MMU功能:地址映射(VA->PA),内存访问权限控制;

3)虚拟地址到物理地址的转换过程:Micro TLB->Main TLB->Page Table Walk

参考《ARM1176 JZF-S Technical Reference Manual》6.3节,Memory access sequence

摘录参考手册中的一段描述:

When the processor generates a memory access, the MMU:

. Performs a lookup for a mapping for the requested virtual address and current ASID and

current world, Secure or Non-secure, in the relevant Instruction or Data MicroTLB.

. If step misses then a lookup for a mapping for the requested virtual address and current

ASID and current world, Secure or Non-secure, in the main TLB is performed.

If no global mapping, or mapping for the currently selected ASID, or no matching NSTID, for

the virtual address can be found in the TLBs then a translation table walk is automatically

performed by hardware, unless Page Table Walks are disabled by the PD0 or PD1 bits in the

TTB Control register, that cause the processor to return a Section Translation fault. See

Hardware page table translation on page -.

If a matching TLB entry is found then the information it contains is used as follows:

. The access permission bits and the domain are used to determine if the access is permitted.

If the access is not permitted the MMU signals a memory abort, otherwise the access is

enabled to proceed. Memory access control on page - describes how this is done.

. The memory region attributes control the cache and write buffer, and determine if the

access is Secure or Non-secure cached, uncached, or device, and if it is shared, as Memory

region attributes on page - describes.

. The physical address is used for any access to external or tightly coupled memory to

perform Tag matching for cache entries.

2. 址映射过程详述

参考《ARM1176 JZF-S Technical Reference Manual》6.11节,Hardware page table translation

关于页表:ARMv6的MMU进行地址映射时涉及到两种页表,一级页表(first level page table)和二级页表(coarse page table)。

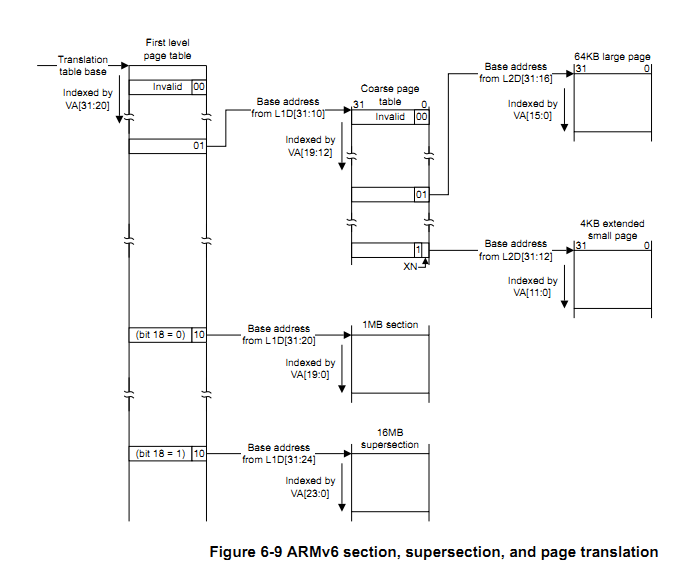

关于映射方式:映射方式有两种,段映射和页映射。段映射只用到一级页表,页映射用到一级页表和二级页表。

关于映射粒度:段映射的映射粒度有两种,1M section和16M supersection;页映射的映射粒度也有两种,4K small page和64K large page。

硬件在做地址转换时,如何知道当前是什么映射方式以及映射粒度是多少呢?

这些信息可以从页表的入口描述符中获得。

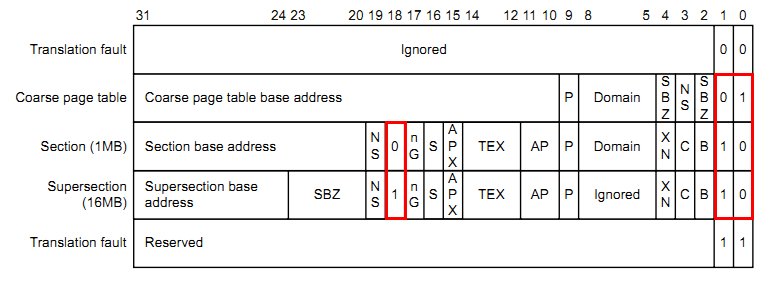

一级页表的入口描述符(first-level descriptor)格式如下:

第[1:0]位决定映射方式:

[1:0]=10b时,是段映射,此时只需作一级映射,描述符的最高12或8位存放的是段基址;

[1:0]=01b时,是页映射,此时虚拟地址转换为物理地址需要经历二级映射,描述符的最高22位存放的是二级页表的物理地址;

第[18]位决定段映射的粒度:

[18]=0b时,映射粒度为1M,描述符的最高12位存放段基址;

[18]=1b时,映射粒度为16M,描述符的最高8位存放段基址;

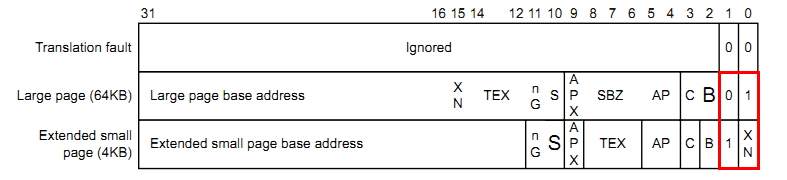

当映射方式为页映射时,我们用到二级页表,二级页表的入口描述符(second-level descriptor)格式如下:

第[1:0]位决定页映射的映射粒度:

[1:0]=10b或11b时,映射粒度为4KB,描述符的最高20位为页基址;

[1:0]=01b时,映射粒度为64KB,描述符的最高16位为页基址;

下面分4种情况对地址映射过程做详细描述:

1)段映射,映射粒度为1M

2)段映射,映射粒度为16M

3)页映射,映射粒度为4K

4)页映射,映射粒度为64K

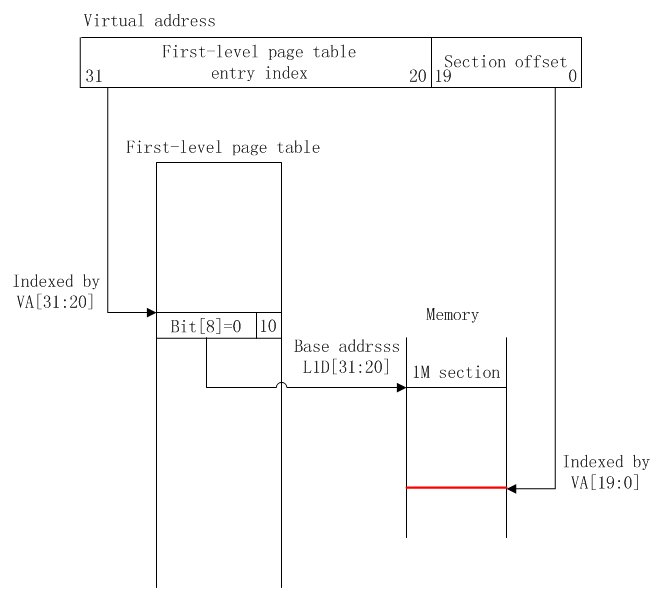

2.1段映射,映射粒度为1M

当映射方式为段映射,且映射粒度为1M时,映射图如下:

虚拟地址到物理地址的映射过程如下:

虚拟地址的[31:20]位存放一级页表的入口index,[19:0]位存放段偏移;

从TTBR(translation table base register,协处理器CP15中的一个寄存器,用于存放一级页表的基址)寄存器中获取一级页表的基址;

一级页表基址+ VA[31:20] = 该虚拟地址对应的页表描述符的入口地址;

页表描述符的[31:20]位为该虚拟地址对应的物理段基址;

物理段基址+ VA[19:0]段偏移= 物理地址

由映射图可知,一个虚拟地址可以索引2^12个一级页表入口,每个入口映射2^20大小的内存,故虚拟地址可以映射的最大物理内存为:2^12 * 2^20,即4G。

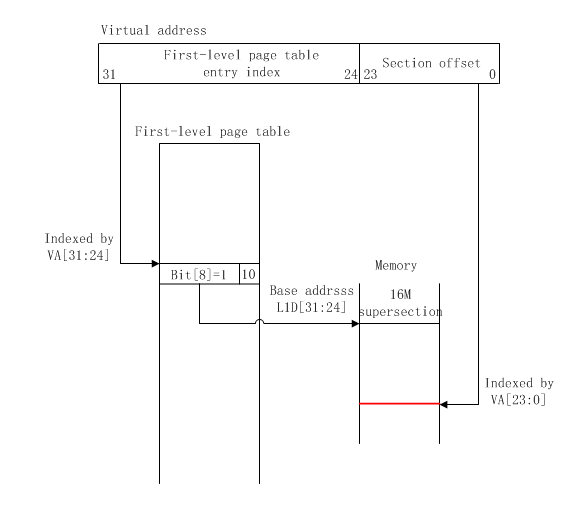

2.2 段映射,映射粒度为16M

当映射方式为段映射,且映射粒度为16M时,映射图如下:

虚拟地址到物理地址的映射过程如下:

虚拟地址的[31:24]位存放一级页表的入口index,[23:0]位存放段偏移;

从TTBR(translation table base register,协处理器CP15中的一个寄存器,用于存放一级页表的基址)寄存器中获取一级页表的基址;

一级页表基址+ VA[31:24] = 该虚拟地址对应的页表描述符的入口地址;

页表描述符的[31:24]位为该虚拟地址对应的物理段基址;

物理段基址+ VA[23:0]段偏移= 物理地址

由映射图可知,一个虚拟地址可以索引2^8个一级页表入口,每个入口映射2^24大小的内存,故虚拟地址可以映射的最大物理内存为:2^8 * 2^24,即4G。

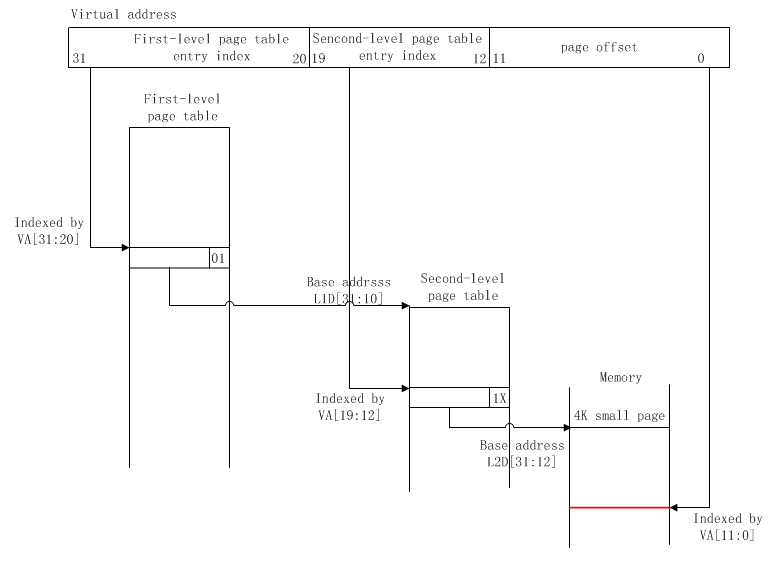

2.3 页映射,映射粒度为4K

当映射方式为页映射,且映射粒度为4K时,映射图如下:

虚拟地址到物理地址的映射过程如下:

虚拟地址的[31:20]位存放一级页表的入口index,[19:12]位存放二级页表的入口index,[11:0]位存放页偏移;

从TTBR(translation table base register,协处理器CP15中的一个寄存器,用于存放一级页表的基址)寄存器中获取一级页表的基址;

一级页表基址+ VA[31:20] = 一级页表描述符的入口地址;

一级页表描述符的[31:10]位存放二级页表的基址;

二级页表基址+ VA[19:12] = 二级页表描述符的入口地址;

二级页表描述符的[31:12]位存放该虚拟地址在内存中的物理页基址;

物理页基址+ VA[11:0]页偏移= 物理地址

由映射图可知,一个虚拟地址可以索引2^12个一级页表入口,每个一级页表入口指向的二级页表最大可以有2^8个二级页表入口,每个二级页表入口映射2^12大小的内存,故虚拟地址可以映射的最大物理内存为:2^12 * 2^8 * 2^12 ,即4G。

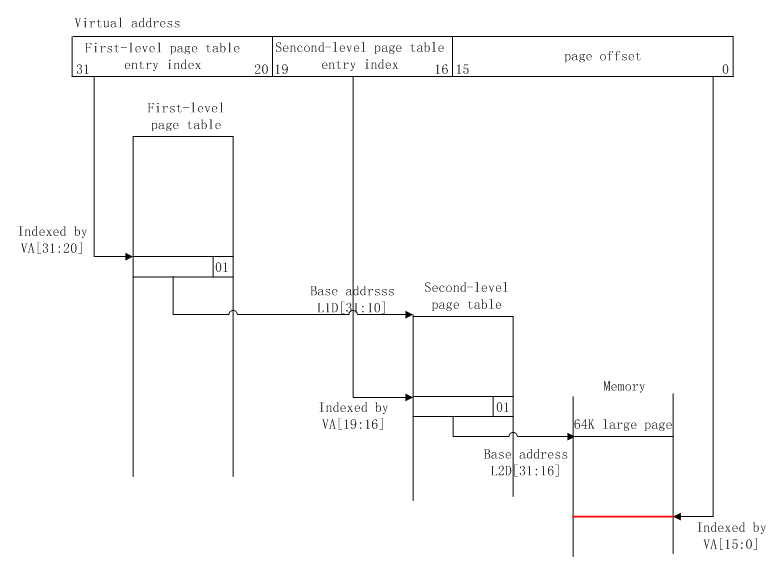

2.4 页映射,映射粒度为64K

当映射方式为页映射,且映射粒度为64K时,映射图如下:

虚拟地址到物理地址的映射过程如下:

虚拟地址的[31:20]位存放一级页表的入口index,[19:16]位存放二级页表的入口index,[15:0]位存放页偏移;

从TTBR(translation table base register,协处理器CP15中的一个寄存器,用于存放一级页表的基址)寄存器中获取一级页表的基址;

一级页表基址+ VA[31:20] = 一级页表描述符的入口地址;

一级页表描述符的[31:10]位存放二级页表的基址;

二级页表基址+ VA[19:16] = 二级页表描述符的入口地址;

二级页表描述符的[31:16]位存放该虚拟地址在内存中的物理页基址;

物理页基址+ VA[15:0]页偏移= 物理地址

由映射图可知,一个虚拟地址可以索引2^12个一级页表入口,每个一级页表入口指向的二级页表最大可以有2^4个二级页表入口,每个二级页表入口映射2^16大小的内存,故虚拟地址可以映射的最大物理内存为:2^12 * 2^4 * 2^16 ,即4G。

2.5 地址映射总图

《ARM1176 JZF-S Technical Reference Manual》中有一张对上述四种映射情况的汇总图:

关于一级页表基地址

-->

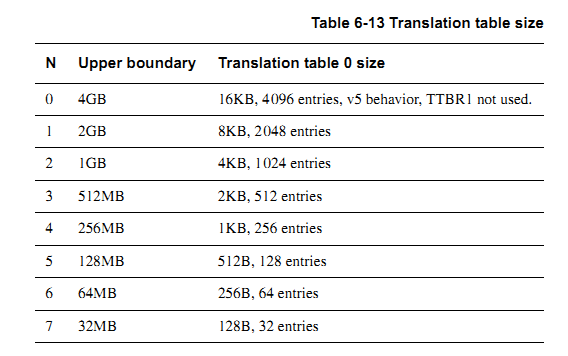

3. 关于一级页表基址

参考《ARM1176 JZF-S Technical Reference Manual》6.12 MMU descriptors

ARMv6中有两个协处理器寄存器用来存放一级页表基地址,TTBR0和TTBR1。操作系统把虚拟内存划分为内核空间和用户空间,TTBR0存放用户空间的一级页表基址,TTBR1存放内核空间的一级页表基址。

In this model, the virtual address space is divided into two regions:

• 0x0 -> <<(-N) that TTBR0 controls

• <<(-N) -> 4GB that TTBR1 controls.

N的大小由TTBCR寄存器决定。0x0 -> 1<<(32-N)为用户空间,由TTBR0控制,1<<(32-N) -> 4GB为内核空间,由TTBR1控制。

N的大小与一级页表大小的关系图如下:

操作系统为用户空间的每个进程分配各自的页表,即每个进程的一级页表基址是不一样的,故当发生进程上下文切换时,TTBR0需要被存放当前进程的一级页表基址;TTBR1中存放的是内核空间的一级页表基址,内核空间的一级页表基址是固定的,故TTBR1中的基址值不需要改变。

4. u-boot中MMU初始化代码分析

u-boot中的MMU地址映射方式为段映射,映射粒度为1M,只用到一级页表。

start.S中的MMU初始化代码如下:

#ifdef CONFIG_ENABLE_MMU

enable_mmu:

/* enable domain access */

ldr r5, =0x0000ffff

mcr p15, , r5, c3, c0, @ load domain access register /* Set the TTB register */

ldr r0, _mmu_table_base

ldr r1, =CFG_PHY_UBOOT_BASE

ldr r2, =0xfff00000

bic r0, r0, r2

orr r1, r0, r1

mcr p15, , r1, c2, c0, /* Enable the MMU */

mmu_on:

mrc p15, , r0, c1, c0,

orr r0, r0, # /* Set CR_M to enable MMU */

mcr p15, , r0, c1, c0,

nop

nop

nop

nop

#endif

…

…

…

#ifdef CONFIG_ENABLE_MMU

_mmu_table_base:

.word mmu_table

#endif

对协处理器的寄存器操作参考:

《ARM1176 JZF-S Technical Reference Manual》Chapter 3 System Control Coprocessor

MMU初始化过程中有一步是将页表基址(CFG_PHY_UBOOT_BASE + mmu_table)存入TTBR0中,在lowlevel_init.S中可以看到对页表的初始化:

#ifdef CONFIG_ENABLE_MMU /*

* MMU Table for SMDK6400

*/ /* form a first-level section entry */

.macro FL_SECTION_ENTRY base,ap,d,c,b

.word (\base << ) | (\ap << ) | \

(\d << ) | (<<) | (\c << ) | (\b << ) | (<<)

.endm

.section .mmudata, "a"

.align

// the following alignment creates the mmu table at address 0x4000.

.globl mmu_table

mmu_table:

.set __base,

// 1:1 mapping for debugging

.rept 0xA00

FL_SECTION_ENTRY __base,,,,

.set __base,__base+

.endr // access is not allowed.

.rept 0xC00 - 0xA00

.word 0x00000000

.endr // 128MB for SDRAM 0xC0000000 -> 0x50000000

.set __base, 0x500

.rept 0xC80 - 0xC00

FL_SECTION_ENTRY __base,,,,

.set __base,__base+

.endr // access is not allowed.

.rept 0x1000 - 0xc80

.word 0x00000000

.endr #endif

下面对页表的初始化代码作详细解释:

/* form a first-level section entry */

.macro FL_SECTION_ENTRY base,ap,d,c,b

.word (\base << ) | (\ap << ) | \

(\d << ) | (<<) | (\c << ) | (\b << ) | (<<)

.endm

定义一个宏FL_SECTION_ENTRY用来设置页表入口描述符,base即物理基址,ap即access permission,d即domain,c即cacheable,b即bufferable。

内存访问控制和段属性相关描述请参考:

《ARM1176 JZF-S Technical Reference Manual》6.6 Memory access control和6.7 Memory region attributes。

.section .mmudata, "a"

.align

// the following alignment creates the mmu table at address 0x4000.

定义一个名为mmudata的段,段属性为“a”,allowable,该段16K对齐。从u-boot.lds中可以看到,u-boot的各个段在内存中的分布依次为:.text,.rodata,.data,.got,.u_boot_cmd,.mmudata,.bss。

为什么页表是16K对齐呢?

在上一节我们讲过:有两个寄存器TTBR0和TTBR1用来存放一级页表基址,操作系统把虚拟地址空间划分为用户空间和内核空间,0x0 -> 1<<(32-N)为用户空间,由TTBR0控制,1<<(32-N) -> 4GB为内核空间,由TTBR1控制,N的大小由TTBCR寄存器决定。由于u-boot主要作用是硬件初始化和引导操作系统,所以没有必要对虚拟地址空间进行划分,即N=0,整个虚拟地址空间由TTBR0控制,TTBR0的格式如下:

N=0时,[31:14]存放页表基址,即一级页表的基址为([31:14]<<14),2^14为16K。

.set __base,

// 1:1 mapping for debugging

.rept 0xA00

FL_SECTION_ENTRY __base,,,,

.set __base,__base+

.endr

对虚拟地址0x0-0xA0000000作平行映射(flat mapping),即把虚拟地址0x0-0xA0000000映射到物理地址0x0-0xA0000000。

// access is not allowed.

.rept 0xC00 - 0xA00

.word 0x00000000

.endr

不对虚拟地址空间0xA0000000-0xC0000000作映射,即禁止访问虚拟地址空间0xA0000000-0xC0000000。

// 128MB for SDRAM 0xC0000000 -> 0x50000000

.set __base, 0x500

.rept 0xC80 - 0xC00

FL_SECTION_ENTRY __base,,,,

.set __base,__base+

.endr

把虚拟地址空间0xC0000000-0xC8000000映射到物理地址空间0x50000000-0x58000000,0x50000000-0x58000000为sdram的地址空间,此时sdram有128M。

// access is not allowed.

.rept 0x1000 - 0xc80

.word 0x00000000

.endr

不对虚拟地址空间0xc8000000-0xffffffff作映射,即禁止访问虚拟地址空间0xc8000000-0xffffffff。

s3c6410_MMU地址映射过程详述的更多相关文章

- Linux启动过程详述

http://www.ibm.com/developerworks/cn/linux/kernel/startup/index.html Linux启动第1步:引导内核 Linux启动第2步:内核部分 ...

- Ogre中Mesh的加载过程详述

转自:http://blog.csdn.net/yanonsoftware/article/details/1031891 如果新开始写一个3D渲染引擎,Mesh应该是一个很好的切入点.当一个看似简单 ...

- MFC程序开始的执行过程详述

1)我们知道在WIN32API程序当中,程序的入口为WinMain函数,在这个函数当中我们完成注册窗口类,创建窗口,进入消息循环,最后由操作系统根据发送到程序窗口的消息调用程序的窗口函数.而在MFC程 ...

- ARM MMU

关于MMU,以下几篇文章写得通俗易懂: s3c6410_MMU地址映射过程详述 追求卓越之--arm MMU详解 基于S3C6410的ARM11学习(十五) MMU来了 这里总结MMU三大作用: 1. ...

- [No0000167]CPU内部组成结构及指令执行过程

计算机的基本硬件系统由运算器.控制器.存储器和输入.输出设备五大部件组成.运算器和控制器等部件被集成在一起统称为中央处理单元(Central Processing Unit,CPU). CPU的功能 ...

- Linux内存地址映射

引言 看过原博主的一些文章,写得很好,虽然博主不提倡这种拿来主义,但我还是忍不住一时手痒.呵呵本文是针对32位x86 CPU中Linux内核地址映射过程的详细介绍和示例.其中由浅入深,介绍了相关寄存器 ...

- Android10_原理机制系列_AMS(ATMS)之应用的第一次启动的过程

概述 该篇基于Android 10的代码.在 AMS之AMS的启动---Android Framework(Android 10) 中已经介绍了,在Android 10中,activity的调度和管理 ...

- linux 内核源代码情景分析——地址映射的全过程

linux 内核采用页式存储管理.虚拟地址空间划分成固定大小的"页面",由MMU在运行时将虚拟地址映射成某个物理内存页面中的地址.页式内存管理比段式内存管理有很多好处,但是由于In ...

- 页置换算法FIFO、LRU、OPT

页置换算法FIFO.LRU.OPT 为什么需要页置换 在地址映射过程中,若在页面中发现所要访问的页面不再内存中,则产生缺页中断.当发生缺页中断时操作系统必须在内存选择一个页面将其移出内存,以便为即将调 ...

随机推荐

- linux下shell脚本学习

在Linux系统中,虽然有各种各样的图形化接口工具,但是sell仍然是一个非常灵活的工具.Shell不仅仅是命令的收集,而且是一门非常棒的编程语言.您可以通过使用shell使大量的任务自动化,shel ...

- iOS8远程通知处理

// IOS8 新系统需要使用新的代码注册推送if ([[[UIDevice currentDevice] systemVersion] floatValue] >= 8.0){ [[UI ...

- 解决Ubuntu不能挂载ntfs格式硬盘

以前都是自动可以挂在NTFS硬盘的,可是现在不能挂载了.搜了一下 这里有办法 http://forum.ubuntu.org.cn/viewtopic.php?t=313930 例如你是 Error ...

- 初始化ArrayList的两种方法

方式一: ArrayList<String> list = new ArrayList<String>(); String str01 = String("str ...

- Stream语法详解

1. Stream初体验 我们先来看看Java里面是怎么定义Stream的: A sequence of elements supporting sequential and parallel agg ...

- SQL查詢數據字典

SELECT d.name AS 表名 , f.value AS 表说明, 字段序号 = a.colorder , 字段名 = a.name , 标识 THEN '√' ELSE '' END , 主 ...

- 使用Nlog记录日志到数据库

Nlog是一个很不错的.NET日志记录组件,它可以将日志输出到控件台,保存到文本,也可以很方便的记录到数据库中. 可以在这里下载Nlog:http://nlog-project.org/ 这里分享一下 ...

- poj 1860 Currency Exchange :bellman-ford

点击打开链接 Currency Exchange Time Limit: 1000MS Memory Limit: 30000K Total Submissions: 16635 Accept ...

- VS打包资源文件,转自推酷,请小星同学查看

上篇博客把收费系统的总体设计进行了一遍讲解,讲解的同时掺杂了些有关.NET编译机制的总结.程序编写测试完成后接下来我们要做的是打包部署程序,但VS2012让人心痛的是没有了打包工具.不知道出于什么原因 ...

- ipv6 测试

# ifconfig wlp0s29f7u6: .... ... inet6 fe80::a00:20ff:fe9d:5c55 prefixlen 64 scopeid 0x20<link> ...