FPGA前世今生(二)

上期我们介绍了关于FPGA内部最基本的结构,在quartus下可以看到整体的结构。

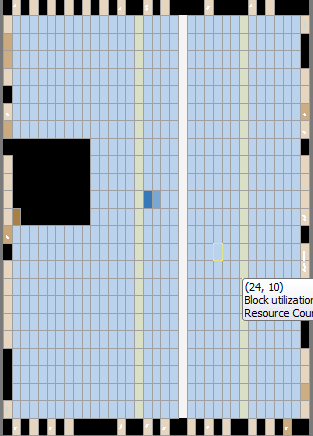

这是在平面规划图下看到的结构,其中蓝色的小格代表一个LAB。四周边上浅棕色的小格代表IO口。

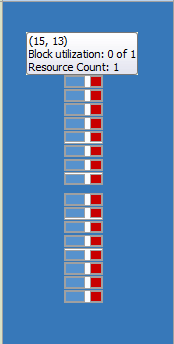

这是一个LAB的内部结构,其中蓝色小格和红色小格就是一个LE,一个LAB有16个LE组成。

从上图可以看到,一个LE包含一个4输入的LUT,一个进位逻辑和一个输出寄存器。

接下来我们介绍一下FPGA与外部通信的接口,IO口。FPGA内部有丰富的资源,一个很重要的资源就是可编程输入输出单元(IOB)。是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求, FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。

通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。目前,I/O口的频率也越来越高,一些高端的FPGA通过DDR寄存器技术可以支持高达2Gbps的数据速率。

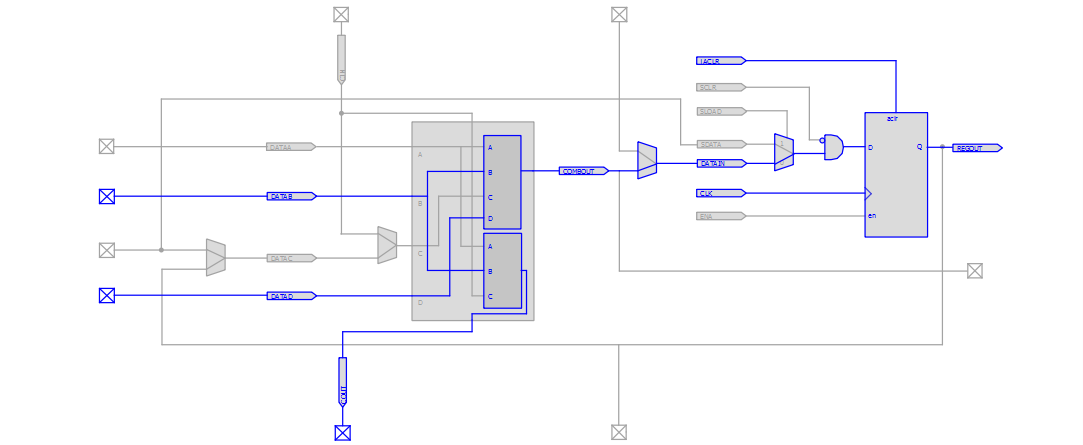

在QUARTUS下我们可以看到IO口的DDR寄存器。

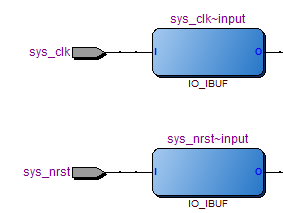

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。FPGA内部有输入、输出缓冲,可以提高信号的驱动力。

如上图我们可以看到,IO_IBUF是输入缓冲,加载在系统时钟和系统复位输入引脚上,提高这两个信号的负载能力。在ALTERA FPGA内部,对于系统时钟的输入缓冲是系统自己加入的。当使用普通IO口时,这个缓冲需要人为加入。当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

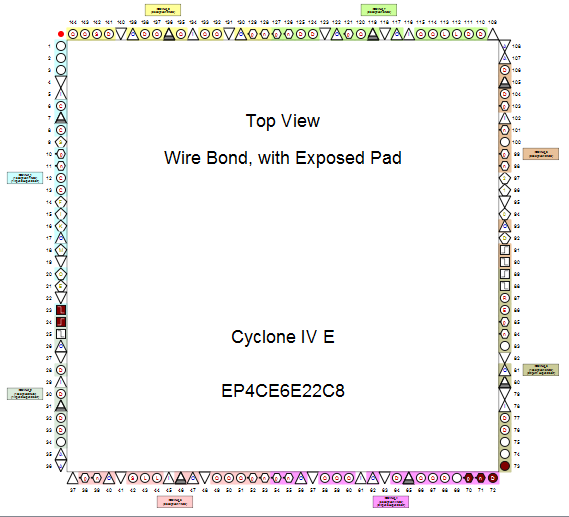

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO电压相同是接口标准的基本条件。

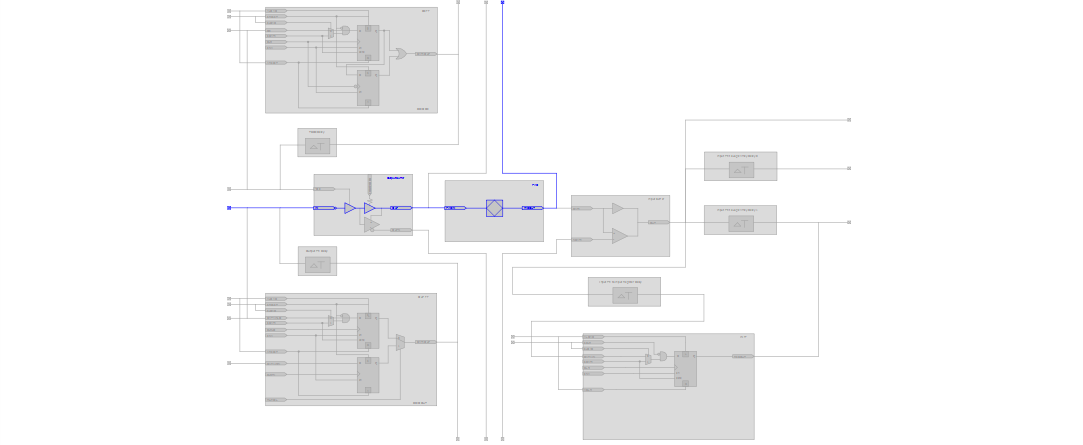

如上图,通常IOB分为8个BANK,每个BANK都可以独立的支持不同的电气标准。

版权所有权归卿萃科技,转载请注明出处

作者:卿萃科技ALIFPGA

原文地址:卿萃科技FPGA极客空间 微信公众号

扫描二维码关注卿萃科技FPGA极客空间

FPGA前世今生(二)的更多相关文章

- FPGA前世今生(四)

前几期我们一直介绍FPGA内部资源,今天我们将用最后的篇幅来介绍剩下的内部资源部分,结束我们FPGA的前世今生.之所以起名字为FPGA前世今生,其实就是介绍一下FPGA内部资源,前世的内部结构资源就不 ...

- FPGA前世今生(一)

关于FPGA,我想做硬件的或多或少都听过.从上世纪80年代算来,FPGA已走过了30多个年头.我们以FPGA两大生产厂商,两大巨头之一的INTEL(altera)公司的FPGA为例,为大家逐步介绍FP ...

- FPGA前世今生(三)

上期介绍了关于FPGA的IOB单元,这期我们介绍一下FPGA内部的其他资源,这些都是学好FPGA的基础.不管前世的沧桑,还是后世的风光,我们都要把我现在的时光,打好基础,学好FPGA. 大多数FPGA ...

- 【FPGA篇章二】FPGA开发流程:详述每一环节的物理含义和实现目标

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照下图进行,有些步骤可能由于其在当前项目中的条件 ...

- 稀疏编码(Sparse Coding)的前世今生(二)

为了更进一步的清晰理解大脑皮层对信号编码的工作机制(策略),须要把他们转成数学语言,由于数学语言作为一种严谨的语言,能够利用它推导出期望和要寻找的程式.本节就使用概率推理(bayes views)的方 ...

- [C#] 回眸 C# 的前世今生 - 见证 C# 6.0 的新语法特性

回眸 C# 的前世今生 - 见证 C# 6.0 的新语法特性 序 目前最新的版本是 C# 7.0,VS 的最新版本为 Visual Studio 2017 RC,两者都尚未进入正式阶段.C# 6.0 ...

- Android平台二维码之生成,扫描 & 识别

1.二维码的前世今生 “二维条码/二维码(2-dimensional bar code)是用某种特定的几何图形按一定规律在平面(二维方向上)分布的黑白相间的图形记录数据符号信息的:在代码编制上巧妙地利 ...

- FPGA开发流程1(详述每一环节的物理含义和实现目标)

要知道,要把一件事情做好,不管是做哪们技术还是办什么手续,明白这个事情的流程非常关键,它决定了这件事情的顺利进行与否.同样,我们学习FPGA开发数字系统这个技术,先撇开使用这个技术的基础编程语言的具体 ...

- FPGA开发流程

需求说明:Verilog设计 内容 :FPGA开发基本流程及注意事项 来自 :时间的诗 原文来自:http://www.dzsc.com/data/2015-3-16/1080 ...

随机推荐

- Maven+Struts+Hibernate+Spring简单项目搭建

这段时间学习如何使用Maven+Struts+Hibernate+Spring注解方式建立项目,在这里感谢孙宇老师. 第一次写博客,主要是方便自己查看,同时分享给大家,希望对大家有所帮助,我也是 ...

- GPL,BSD,Apache,MIT开源许可协议

在linux环境下学习的多了,这些开源协议也听的见的越来越多,感觉有必要仔细了解一下. 1. BSD 先说BSD是因为它的自由度相对来说是比较大的.BSD全称Berkeley Software Dis ...

- java中的Properties

Properties类继承自HashTable类并实现了Map接口,也是使用一种键值对的形式来保存属性集.不过Properties有特殊的地方,就是它的键和值都是字符串类型. Properties中的 ...

- mysql数据库优化课程---9、php用什么写的

mysql数据库优化课程---9.php用什么写的 一.总结 一句话总结:php是用c语言写的,所以php里面的那些模块什么都是c语言 c 1.php用什么写的? c php是用c语言写的,所以php ...

- Robot Framework(一)

一. 定义 Robot Framework是一款python编写的功能自动化测试框架,具有良好的可扩展性,支持关键字驱动,可以同时测试多种类型的客户端或者接口,可以进行分布式测试执行 二. Robot ...

- nginx 相关资料

1.https://juejin.im/post/5a2600bdf265da432b4aaaba (nginx从入门到实践) 2.https://blog.csdn.net/hzsunshine/a ...

- sql server数据库课程设计分析

课题:能源管理收费系统 系统功能的基本要求: (1)用户基本信息的录入:包括用户的单位.部门.姓名.联系电话.住址 : (2)用户水.电.气数据的录入(每个月的数据的录入): (3)水.电.气价格的管 ...

- Ceph配置项动态变更机制浅析

转自:https://www.ustack.com/blog/ceph%e9%85%8d%e7%bd%ae%e9%a1%b9%e5%8a%a8%e6%80%81%e5%8f%98%e6%9b%b4%e ...

- Workflow Builder 2.6.3 Certified on Windows 10 for EBS 12.x

By Steven Chan - EBS-Oracle on May 17, 2016 Workflow Builder 2.6.3 is now certified on Windows 10 de ...

- thinking java

public class CrossContainerIteration{ public static void display(Iterator<Pet> it){ while(it.h ...