全国产!全志A40i+Logos FPGA核心板(4核ARM Cortex-A7)硬件说明

硬件资源

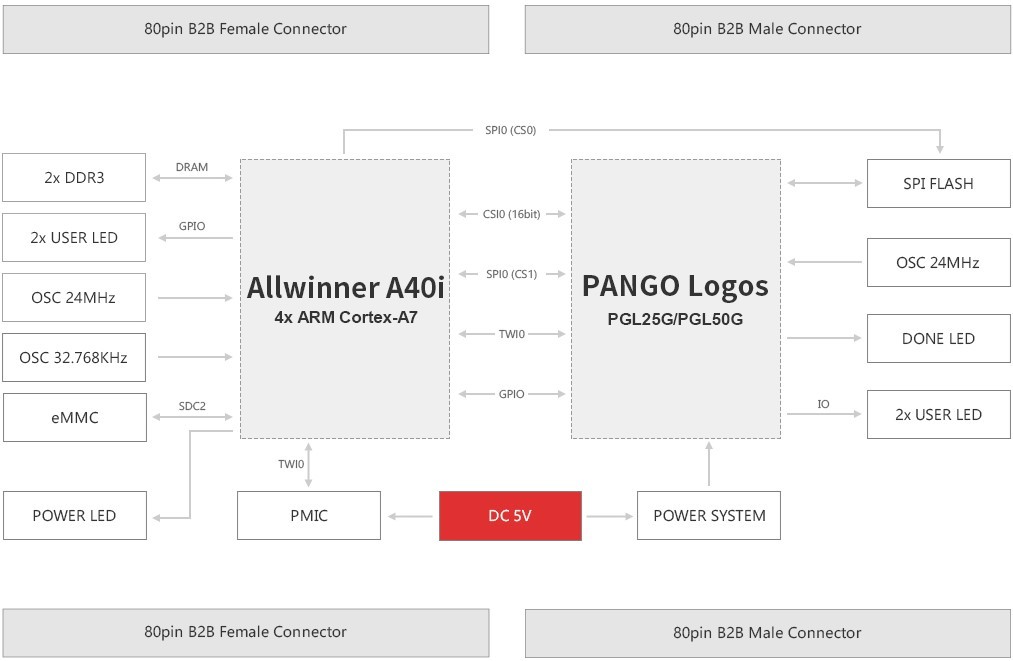

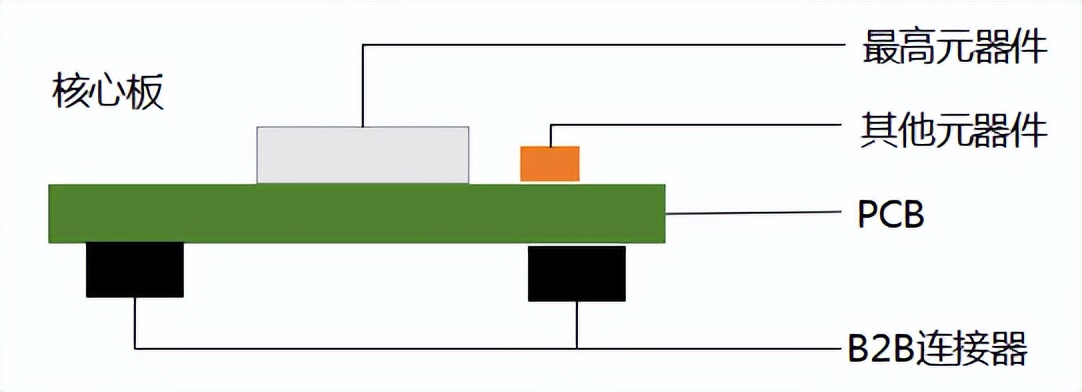

SOM-TLA40iF核心板板载ARM、FPGA、ROM、RAM、晶振、电源、LED等硬件资源,并通过B2B连接方式引出IO。核心板所有器件(包括B2B连接器)均采用国产工业级方案,国产化率100%。

图 1 核心板硬件框图

图 1 核心板硬件框图 图 2

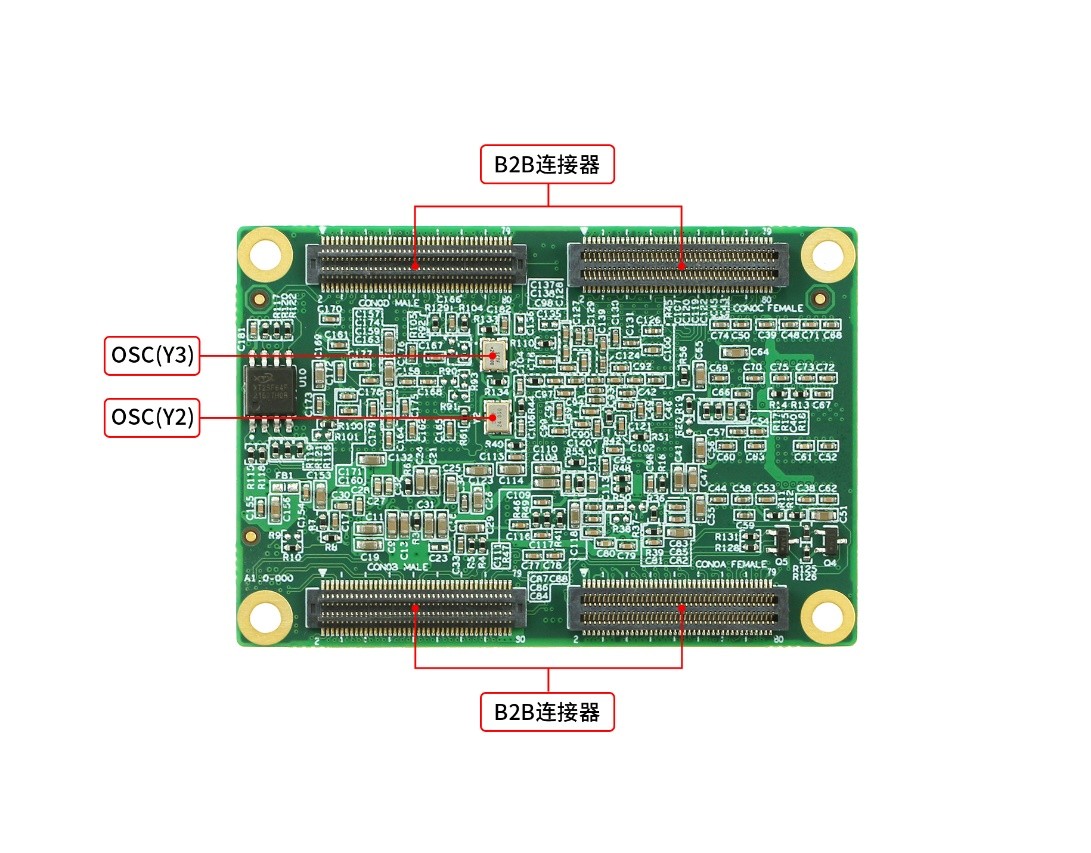

图 2 图 3

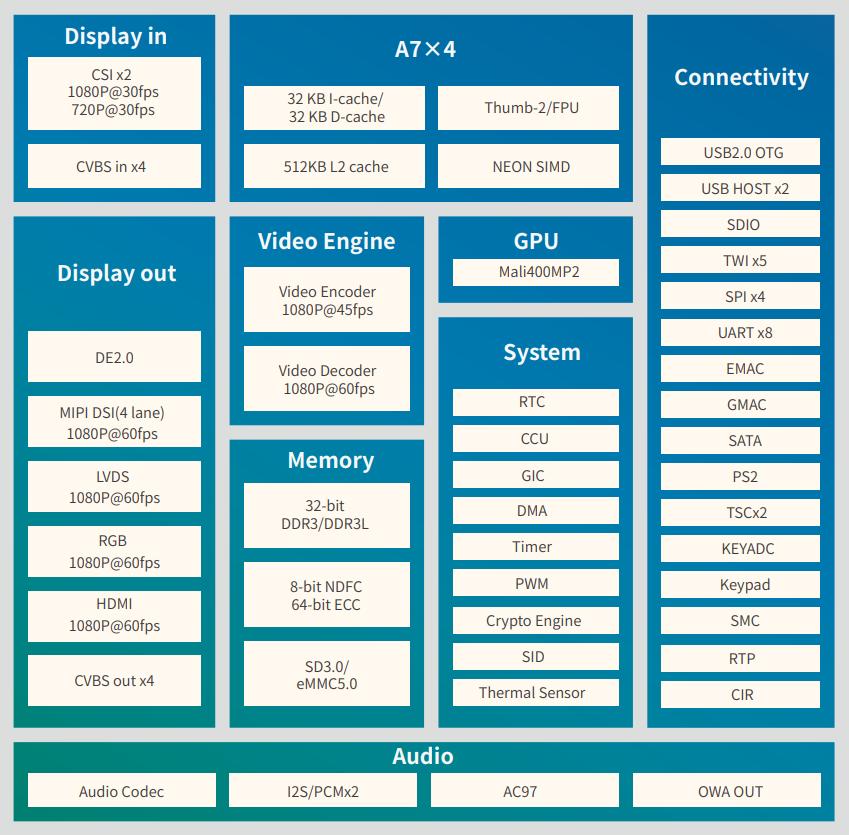

图 3ARM

ARM型号为全志科技A40i,LFBGA封装,工作温度为-40°C~85°C,引脚数量为468个,尺寸为16mm*16mm。

A40i处理器架构如下:

表 1

|

A40i |

4x ARM Cortex-A7,每核主频高达1.2GHz |

|

GPU:Mali400 MP2,支持OpenGL ES 1.1/2.0、Open VG 1.1 |

|

|

Encoder:支持1080P@45fps H.264视频硬件编码 |

|

|

Decoder:支持1080P@45fps H.264视频硬件解码 |

图 4 A40i处理器功能框图

图 4 A40i处理器功能框图FPGA

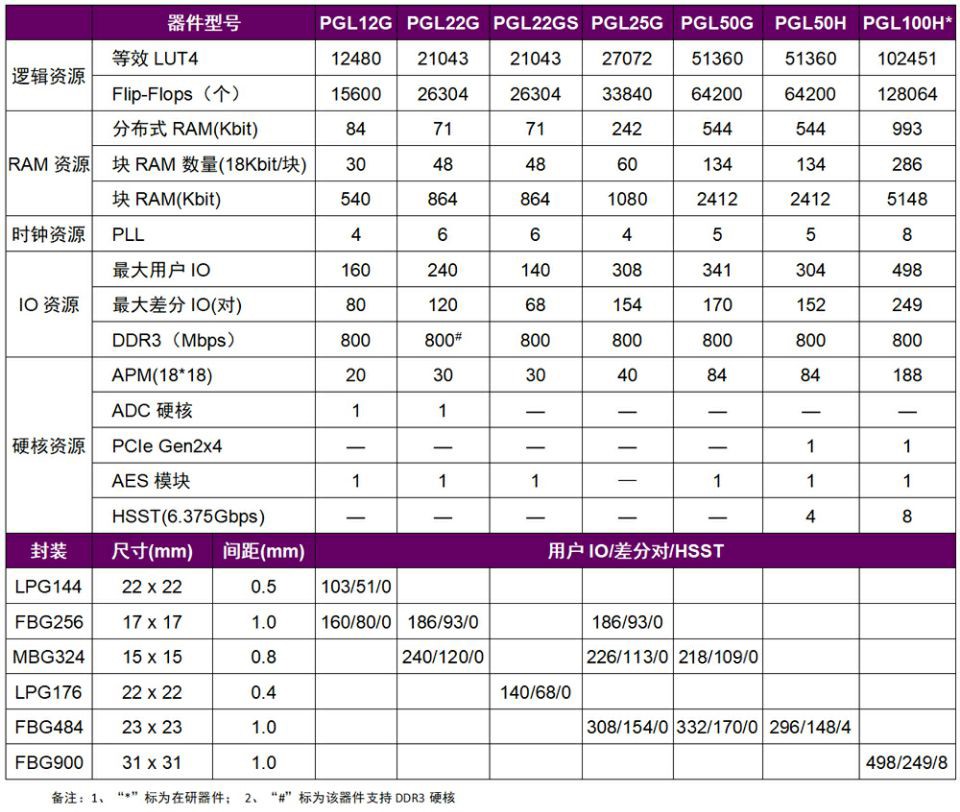

FPGA型号兼容紫光同创PGL25G-6IMBG324(MBG324封装)、PGL50G-6IMBG324(MBG324封装),工作温度为-40°C~100°C,引脚数量为324个,尺寸为15mm*15mm。

表 2

|

FPGA |

紫光同创Logos PGL25G-6IMBG324 |

紫光同创Logos PGL50G-6IMBG324 |

|

ROM |

64Mbit SPI FLASH |

|

|

Logic Cells(LUT4) |

27072 |

51360 |

|

Flip-Flops |

33840 |

64200 |

|

DSP Slice |

40(APM,Arithmetic Process Module) |

84(APM,Arithmetic Process Module) |

|

Block RAM(18Kbit) |

60 |

134 |

|

CMT |

4(PLL) |

5 |

|

IO |

单端(1个),差分对(48对),共97个IO |

|

|

LED |

2x 用户可编程指示灯 |

|

|

1x DONE指示灯 |

||

图 5 Logos特性

图 5 Logos特性ROM

1.3.1 eMMC

核心板通过SMHC(主机控制器)连接至eMMC,使用SDC2总线,采用8bit数据线。eMMC型号兼容江波龙(Longsys)公司的FEMDRW008G-88A39(8GByte)、康盈(Kowin)公司的KAS0311D(8GByte)。

1.3.2 SPI FLASH

FPGA端通过SPI总线连接工业级SPI FLASH,型号为芯天下(XTX)公司的XT25F64FSSIGT(64Mbit)。ARM端通过SPI总线经过模拟开关切换后,亦可连接至SPI FLASH,实现固化FPGA端可执行程序的功能。

RAM

核心板通过专用SDRAM总线连接2片DDR3,分别采用16bit数据线,共32bit。DDR3型号兼容紫光国芯(UniIC)公司的SCB13H4G160AF-11MI(512MByte)和SCB13H8G162BF-13KI(1GByte)、江波龙(Longsys)公司的F60C1A0004-M79W(512MByte),支持DDR3-1152工作模式(576MHz)。

晶振

核心板采用2个工业级晶振Y1和Y2。Y1晶振时钟频率为32.768KHz,精度为±20ppm,Y2晶振时钟频率为24MHz,精度为±10ppm,为ARM端提供系统时钟源。

核心板采用工业级晶振Y3。Y3晶振时钟频率为24MHz,精度为±20ppm,为FPGA端提供系统时钟源。

电源

ARM端采用工业级PMIC电源管理芯片,满足系统的供电要求和CPU上电、掉电时序要求,核心板采用5V直流电源供电。

FPGA端采用分立电源输出1.2V及3.3V电源,满足FPGA端的供电要求,使用ARM端3.3V电源控制电源使能,分立电源采用5V直流电源供电。

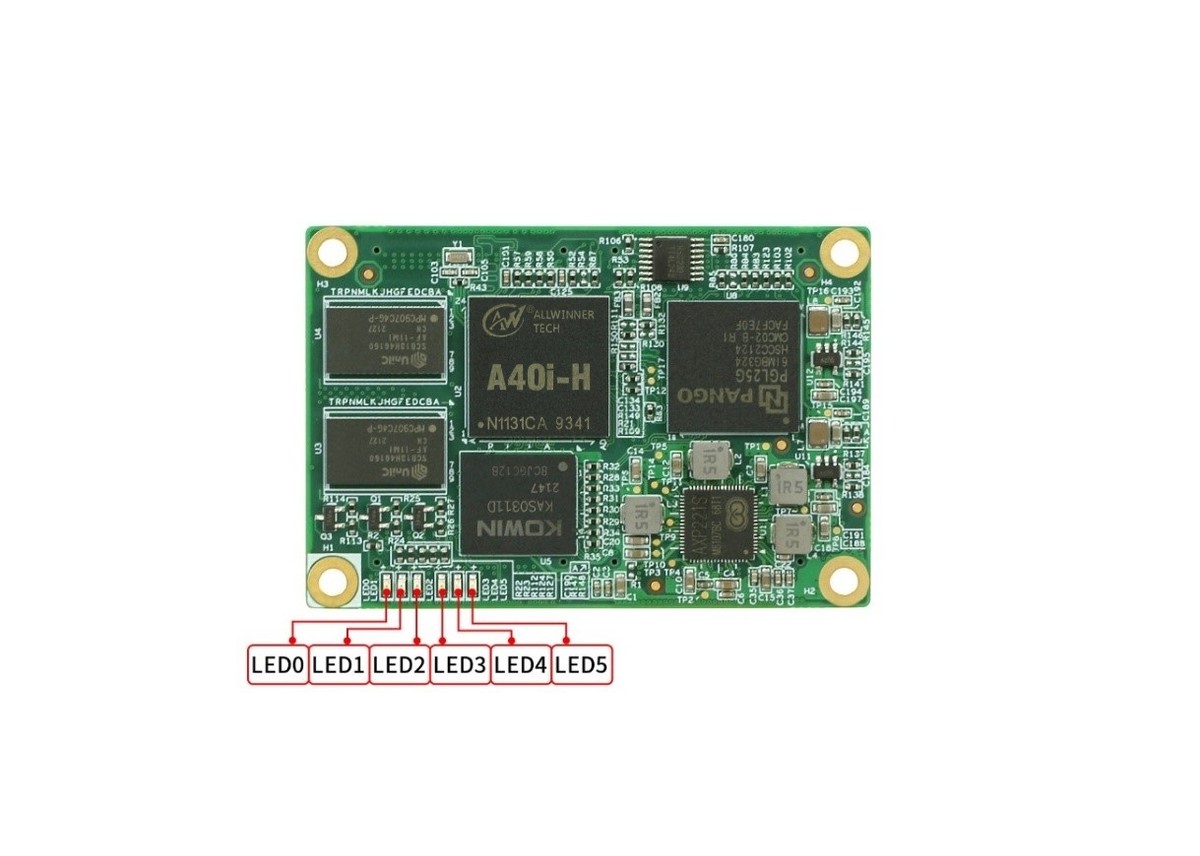

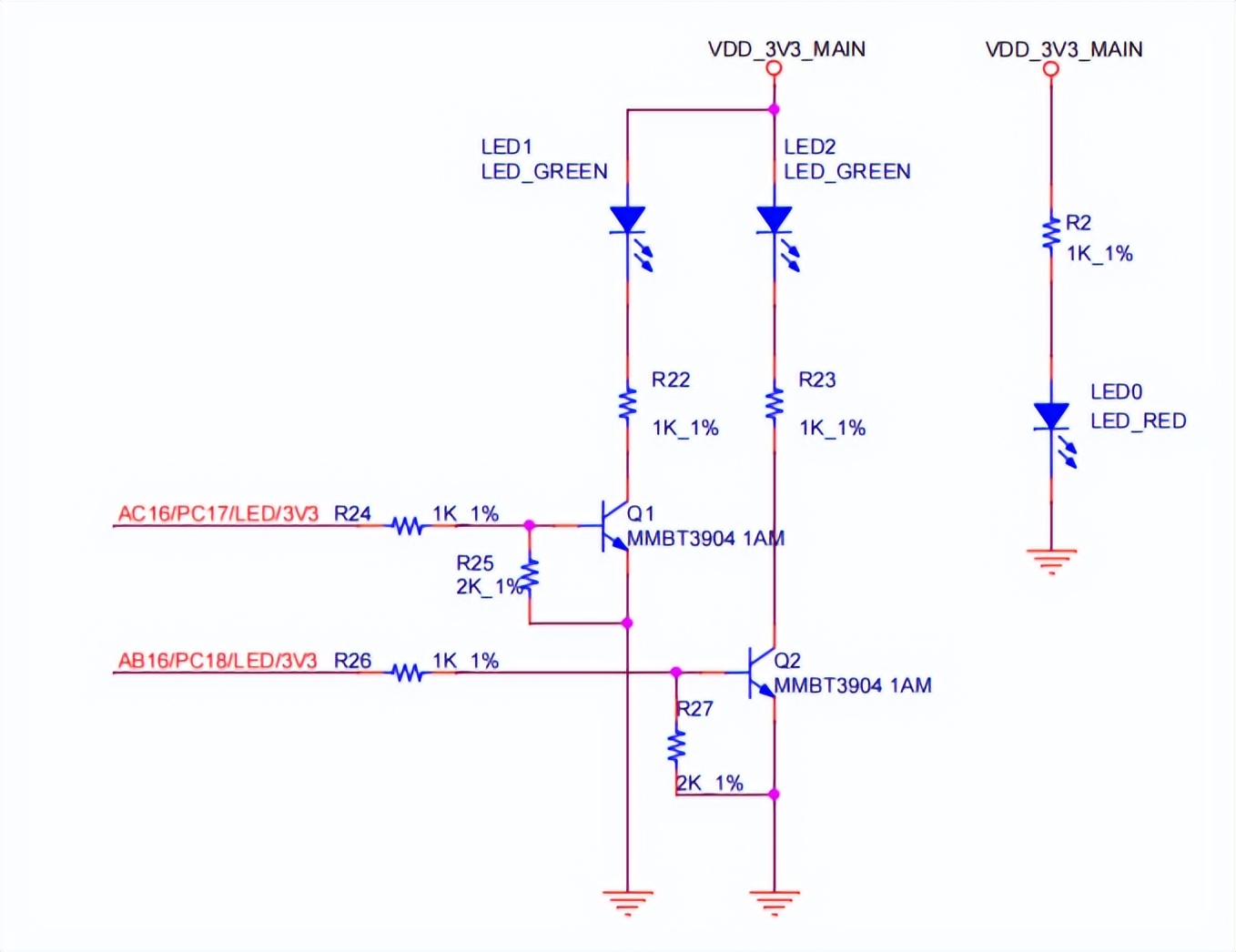

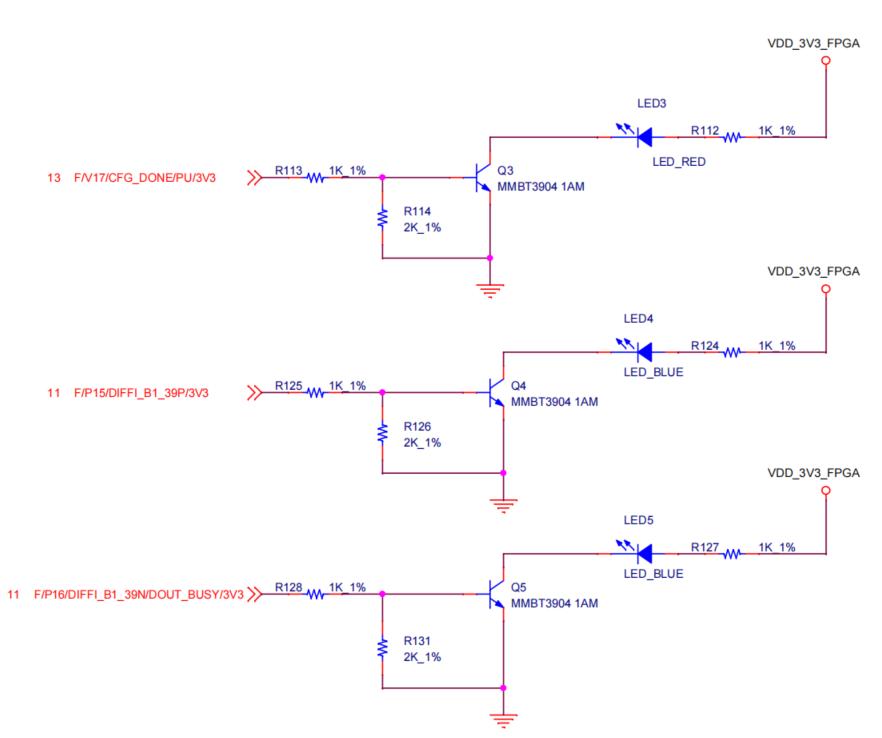

LED

核心板板载6个LED,其中LED0为电源指示灯,默认上电时点亮。LED1和LED2为ARM端用户可编程指示灯,分别对应PC17和PC18两个引脚,高电平点亮。LED3为FPGA端DONE指示灯,FPGA端加载可执行程序后点亮。LED4和LED5为FPGA端用户可编程指示灯,分别对应P15和P16两个引脚,高电平点亮。

图 6

图 6 图 7

图 7 图 8

图 8B2B连接器

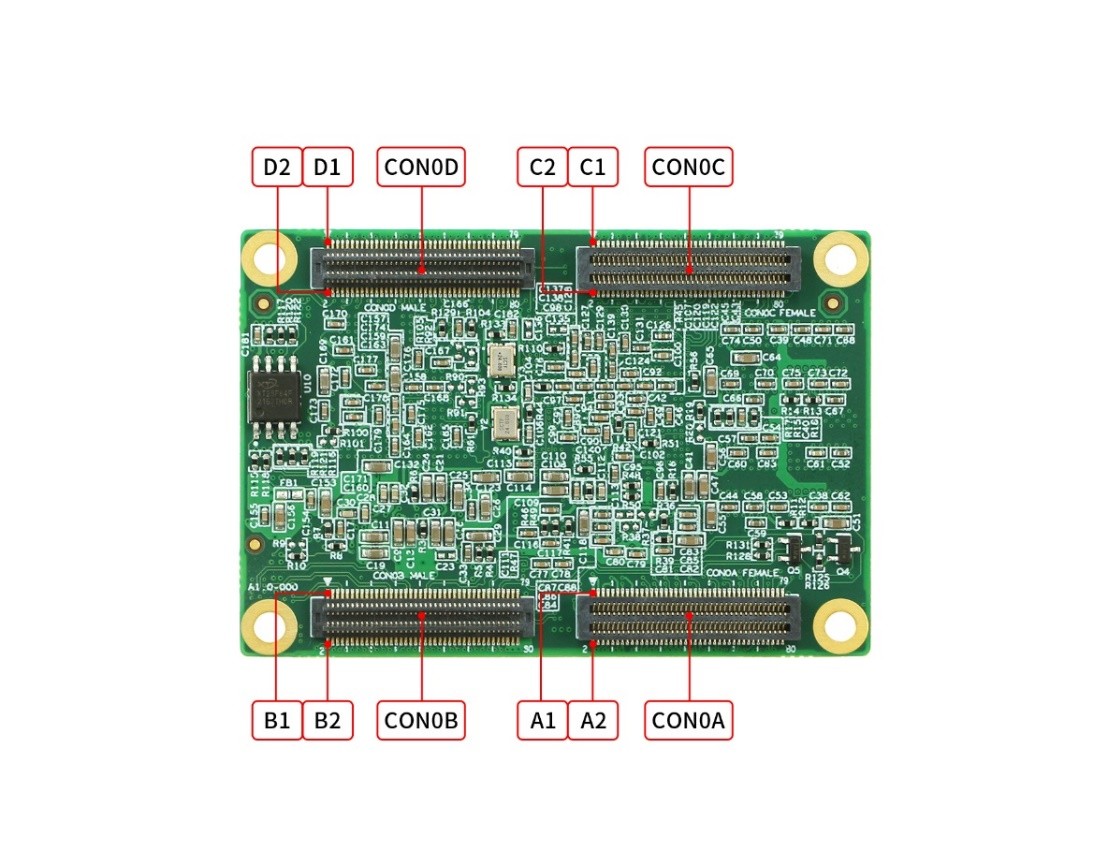

核心板采用爱特姆公司的4个工业级B2B连接器,共320pin,间距0.5mm,合高4.0mm。其中2个80pin公座B2B连接器,型号BTB050080-F1D08200,高度1.0mm。2个80pin母座B2B连接器,型号BTB050080-F1D08200,高度3.0mm。

外设资源

核心板引出的ARM端主要外设资源及性能参数如下表所示。

表 3

|

外设资源 |

数量 |

性能参数 |

|

CSI |

1 |

CSI1:(CMOS sensor parallel interface),支持720P@30fps; 备注:在核心板内部,CSI0(16bit)已连接至FPGA,且未引出至B2B连接器 |

|

TVIN |

4 |

CVBS输入,支持NTSC和PAL制式; |

|

TVOUT |

4 |

CVBS输出,支持NTSC和PAL制式; |

|

RGB DISPALY |

2 |

包含LCD0、LCD1输出,支持1080p@60fps; |

|

LVDS DISPALY |

2 |

包含LVDS0、LVDS1输出,支持 1080p@60fps; 备注:LVDS0、LVDS1与LCD0(RGB DISPALY)引脚复用 |

|

MIPI DSI |

1 |

包含4个数据通道,支持1080p@60fps; 符合MIPI DSI V1.01和MIPI D-PHY V1.00; |

|

HDMI OUT |

1 |

HDMI 1.4规范,支持1080p@60fps; |

|

SMHC |

3 |

支持SD3.0,SDIO2.0,MMC5.0; SDC0:4位数据总线(推荐作为底板Micro SD功能); SDC1:4位数据总线; SDC3:4位数据总线; 备注:核心板板载eMMC已使用SDC2,且SDC2未引出至B2B引脚 |

|

TWI(I2C) |

5 |

TWI0~TWI4,支持标准模式(100Kbps)和高速模式(400Kbps); 备注:在核心板内部,TWI0已连接至FPGA、PMIC,同时引出至B2B连接器 |

|

SPI |

3 |

每路SPI支持2个片选信号; 时钟频率高达100MHz; 支持Master Mode、Slave Mode; 备注:在核心板内部,SPI0(CE0)已连接至FPGA端SPI FLASH,SPI0(CE1)已连接至FPGA,且SPI0未引出至B2B连接器 |

|

UART |

8 |

支持4Mbps波特率; 支持硬件或软件流控; |

|

TSC |

2 |

可作为SPI(Synchronous Parallel Interface)或SSI(Synchronous Serial Interface)接口; |

|

CIR |

2 |

可通过红外线进行远程控制; |

|

RTP |

1 |

四线电阻触摸,12位SAR型A/D转换器,采样率2MHz; |

|

USB OTG |

1 |

USB2.0(USB0),支持高速模式(480Mbps)、全速模式(12Mbps)、低速模式(1.5Mbps); |

|

USB HOST |

2 |

USB2.0(USB1、USB2),支持高速模式(480Mbps)、全速模式(12Mbps)、低速模式(1.5Mbps); |

|

I2S/PCM |

2 |

全双工,采样率8KHz~192KHz; |

|

AC97 |

1 |

可变采样率AC97编解码器; 全双工,串行接口,采样率高达48KHz; |

|

OWA |

1 |

One Wire Audio,兼容S/PDIF协议; |

|

Audio Codec |

1 |

包含2通道ADC,采样率8KHz~48KHz; 包含2通道DAC,采样率8KHz~192KHz; 包含2路单声道MIC IN、1路立体声LINE IN、1路立体声FM IN;包含1路差分PHONE OUT、1路立体声H/P(Headphone) OUT; |

|

Ethernet |

2 |

1路EMAC,支持MII PHY接口(10/100Mbps); 1路GMAC,支持MII/RMII/RGMII PHY接口(10/100/1000Mbps); |

|

SATA |

1 |

支持设备热插拔,支持3.0Gbps速率; |

|

PS2 |

2 |

兼容IBM PS/2协议; |

|

SCR |

1 |

Smart Card Reader,时钟速率可调; 支持ISO/IEC 7816-3和EMV2000(4.0)规范; |

|

KEYADC |

2 |

多按键检测接口,6bit分辨率,输入电压范围为0~2V; 转换速率最高可达250Hz; |

|

KEYPAD |

1 |

8 x 8键盘矩阵接口; |

|

PWM |

8 |

支持PWM输出、输入捕获,输出频率高达24/100MHz; 支持0~100%可调占空比; |

|

JTAG |

1 |

支持边界扫描; 支持IEEE 1149.1和IEEE 1149.6标准。 |

备注:核心板引出的FPGA端主要资源为BANK0、BANK2部分IO。

引脚说明

引脚排列

核心板B2B连接器分别为CON0A(母座,对应评估底板CON0A)、CON0B(公座,对应评估底板CON0B)、CON0C(母座,对应评估底板CON0C)、CON0D(公座,对应评估底板CON0D),引脚排列如下图所示。

图 9 核心板引脚排列示意图

图 9 核心板引脚排列示意图电气特性

工作环境

表 14

|

环境参数 |

最小值 |

典型值 |

最大值 |

|

工作温度 |

-40°C |

/ |

85°C |

|

存储温度 |

-50°C |

/ |

90°C |

|

工作湿度 |

35%(无凝露) |

/ |

75%(无凝露) |

|

存储湿度 |

35%(无凝露) |

/ |

75%(无凝露) |

|

工作电压 |

/ |

5.0V |

/ |

功耗测试

表 15

|

工作状态 |

电压典型值 |

电流典型值 |

功耗典型值 |

|

状态1 |

5.0V |

0.21A |

1.05W |

|

状态2 |

5.0V |

0.55A |

2.75W |

备注:功耗基于TLA40iF-EVM评估板测得。测试数据与具体应用场景有关,仅供参考。

状态1:系统启动,评估板不接入其他外接模块,ARM端不运行程序,FPGA端运行LED测试程序。

状态2:系统启动,评估板不接入其他外接模块,ARM端运行DDR压力读写测试程序,4个ARM Cortex-A7核心使用率约为100%,FPGA端运行IFD测试程序。

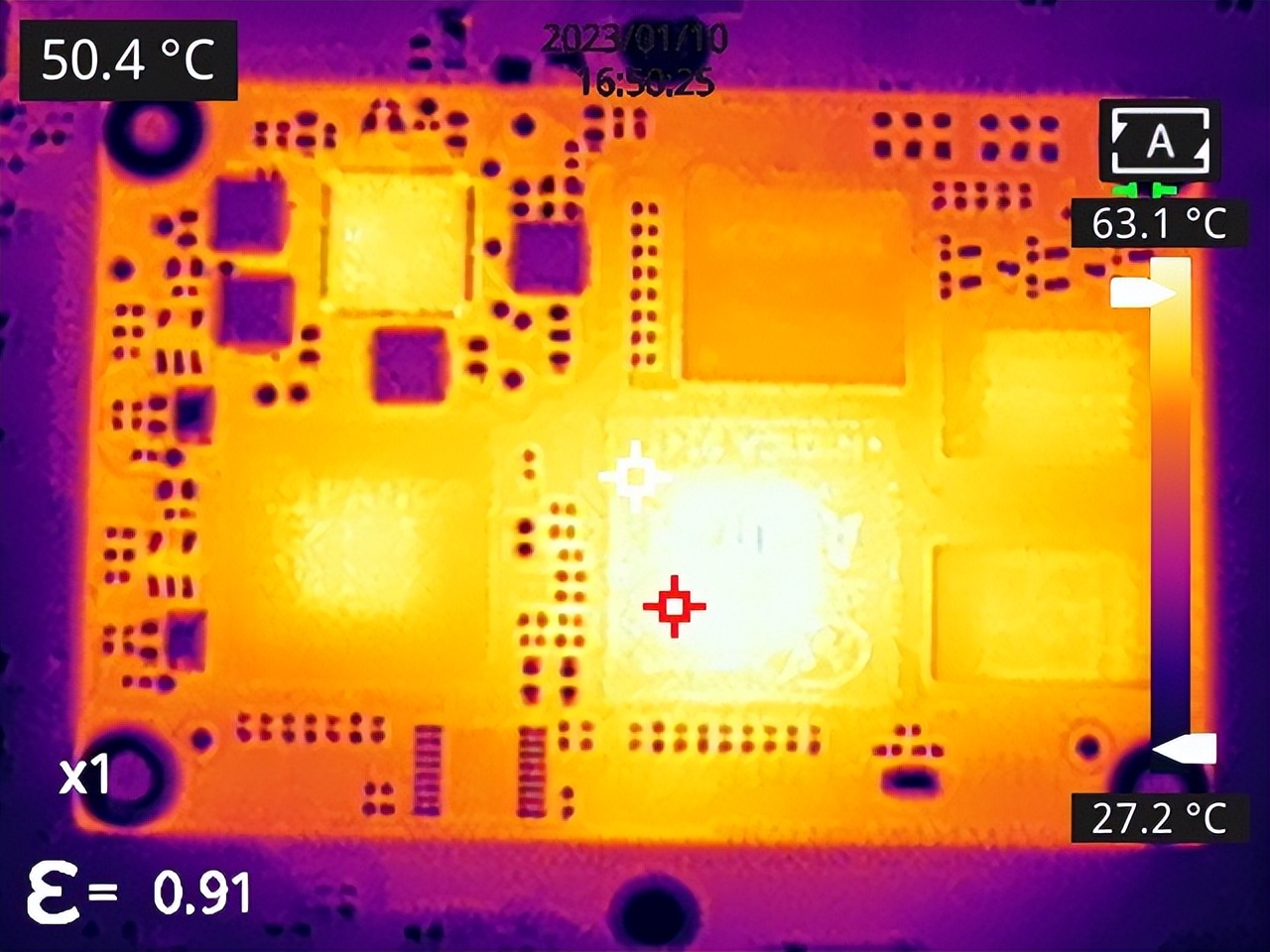

热成像图

核心板未安装散热片与风扇,在常温环境、自然散热、满负荷状态下稳定工作10min后,测得热成像图如下所示。其中红色测温点为最高温度点(64.3℃),绿色测温点为最低温度点(28.8℃),白色测温点为画面中心温度点(46.8℃)。

备注:不同测试条件下结果会有所差异,数据仅供参考。

图 10

图 10请参考如上测试结果,并根据实际情况合理选择散热方式。

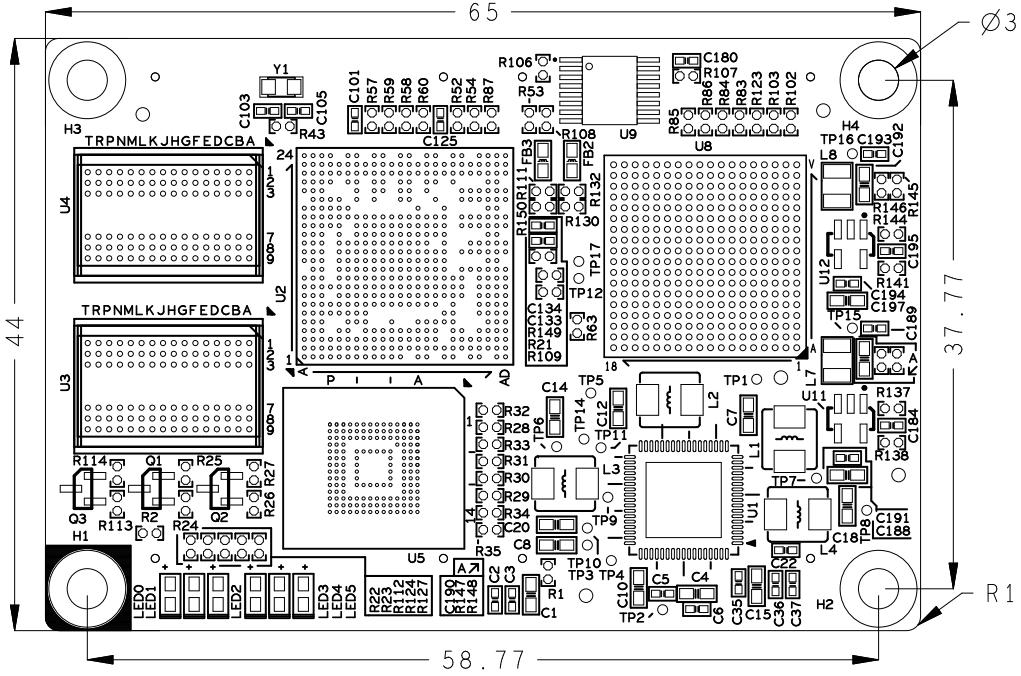

机械尺寸

核心板主要硬件相关参数如下所示,仅供参考。

表 16

|

PCB尺寸 |

65mm*44mm |

|

PCB层数 |

10层 |

|

元器件最高高度 |

2.0mm |

|

PCB板厚 |

2.0mm |

|

重量 |

19.8g |

图 11

图 11 图 12

图 12元器件最高高度:指核心板最高元器件水平面与PCB正面水平面的高度差。核心板最高元器件为电感(L1)。

底板设计注意事项

最小系统设计

基于SOM-TLA40iF核心板进行底板设计时,请务必满足最小系统设计要求,具体如下。

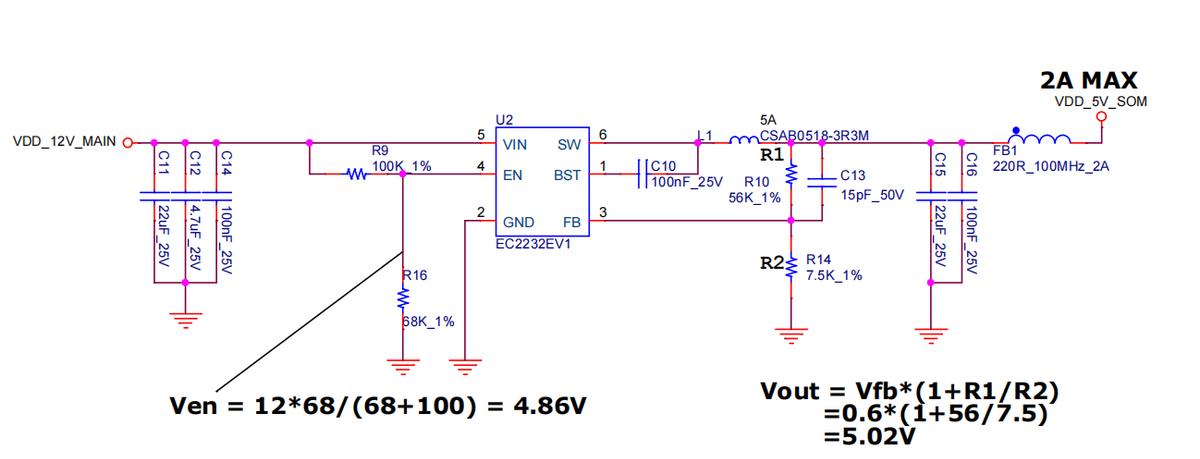

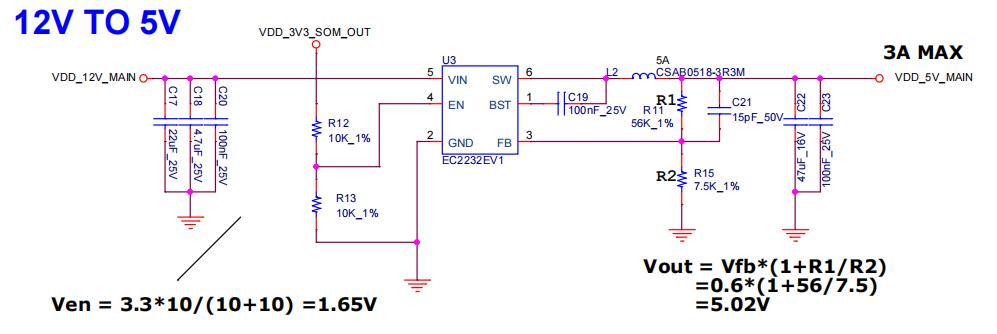

电源设计说明

- VDD_5V_SOM

VDD_5V_SOM为核心板的主供电输入,电源功率建议参考评估板按最大10W进行设计,并且在靠近核心板电源输入端放置50uF左右的储能电容。

图 13

图 13- VDD_5V_MAIN & VDD_3V3_MAIN

VDD_5V_MAIN、VDD_3V3_MAIN为底板提供的外设电源。为使VDD_5V_MAIN、VDD_3V3_MAIN满足处理器的上电、掉电时序要求,推荐使用VDD_3V3_SOM_OUT来控制VDD_5V_MAIN和VDD_3V3_MAIN的电源使能。

图 14

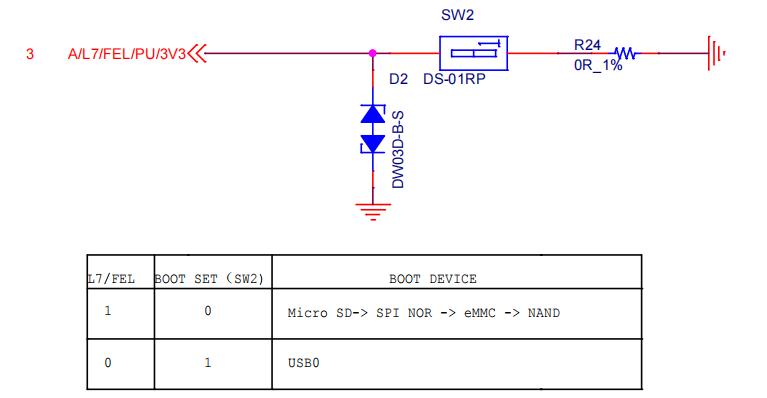

图 14系统启动配置

核心板内部L7/FEL已设计10K上拉电阻,设计系统启动配置电路时,请参考评估底板BOOT SET部分电路进行相关设计。当L7/FEL为高电平时,CPU会按顺序检测对应设备启动。

图 16

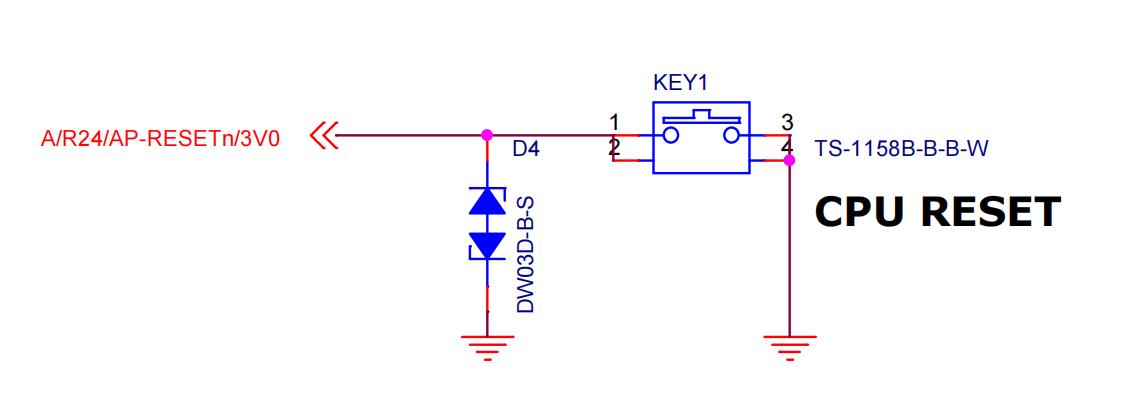

图 16系统复位信号

R24/AP-RESETn(PMIC_PWROK)

R24/AP-RESETn为CPU的复位输入引脚,同时与PMIC的复位输出PWROK相连,可用于输出控制外设接口的复位。该复位在VDD_3V3_SOM_OUT延迟60ms后拉高。当使用该复位作为其他外设复位信号时,需考虑外设电源与复位之间的时序是否满足要求。

图 17

图 17PMIC_PWRON

PMIC_PWRON为PMIC的开关机控制引脚,PMIC内部已上拉100K电阻到1.8V,默认情况请悬空处理。

其他设计注意事项

保留Micro SD卡接口

评估底板通过SDC0总线引出Micro SD接口,主要用于调试过程中使用Linux系统启动卡来启动系统,或批量生产时可基于Micro SD卡快速固化系统至eMMC,底板设计时建议保留此外设接口。

保留UART0接口

评估底板将F23/PB23/UART0_RX和F22/PB22/UART0_TX引脚通过CH340T芯片引至Type-C接口,作为系统调试串口使用,底板设计时建议保留UART0作为系统调试串口。

全国产!全志A40i+Logos FPGA核心板(4核ARM Cortex-A7)硬件说明的更多相关文章

- arm + fpga 核心板

- 迅为IMX6Q四核核心板商业级|工业级|IMX6Plus版本|IMX6DL双核核心板

IMX6Q处理器:兼容单核,双核,工业级,汽车级,IMX6Q最新Plus版本,共用同一底板,高端产品无忧. i.MX6系列针对消费电子.工业控制和汽车应用领域,它将ARM Cortex-A9架构的高功 ...

- 迅为IMX6核心板兼容工业级、商业扩展级、Plus版本核心板

IMX6核心板兼容单核.双核.四核.工业级.汽车级.iMX6Q最新Plus版本,可根据用户需求更换,百变定制,高端产品无忧! iMX6Q核心板(四核商业级) iMX6DL核心板(双核商业级) iMX6 ...

- 【iCore1S 双核心板_ARM】例程七:通用定时器实验——定时点亮LED

实验原理: 通过STM32的三个GPIO口来驱动LED灯的三个通道:设定GPIO为推挽 输出模式,采用灌电流的方式与LED连接,输出高电平LED灭,输出低电平 LED亮,通过通用定时器TIM3实现50 ...

- 恩智浦iMX6Q核心板/飞思卡尔Cortex-A9高稳定性低功耗开发板

iMX6Q核心板-商业级 iMX6Q-Plus核心板 iMX6DL核心板-商业级 iMX6Q核心板-工业级 iMX6核心板区别: 名称 主频 内存 存储 SATA接口 运行温度 引角扩展 iMX6Q核 ...

- IMX6核心板系列解决方案-工业级|商业级|四核|双核|Plus核心板

i.MX 6Quad四核商业级和工业级系列的应用处理器将可扩展平台与广泛的集成和高能效处理功能相结合,尤其适合多媒体应用.i.MX6 Quad处理器的特性包括: 满足操作系统和游戏的MIPS需求,增强 ...

- 基于全志A40i开发板——Linux-RT内核应用开发教程(1)

目录 1 Linux-RT内核简介 3 2 Linux系统实时性测试 3 3 rt_gpio_ctrl案例 10 4 rt_input案例 15 本文为Linux-RT内核应用开发教程的第一章节--L ...

- 【新产品发布】【iCore2 ARM / FPGA 双核心板】

iCore2是一款包含ARM / FPGA两大利器的双核心板.ARM方面,采用意法半导体高性能的32位Cortex-M3内核STM32F103VE微处理器,主频达72MHz,并包含丰富外设接口.FPG ...

- 202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC72K325T的高速数据处理核心板

基于TI DSP TMS320C6678.Xilinx K7 FPGA XC72K325T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

- 175-基于TI DSP TMS320C6455、Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板

基于TI DSP TMS320C6455.Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

随机推荐

- 开源电子邮件营销平台 listmonk 使用教程

做产品肯定要做电子邮件营销,特别是面向海外的产品,电子邮件营销已成为企业与客户沟通.建立品牌忠诚度和推动销售的重要工具,可以直接接触到目标受众,提供个性化内容,并以相对较低的成本获得可观的投资回报.你 ...

- linux 系统tar文件压缩打包命令

打包成tar.gz格式压缩包 # tar -zcvf renwolesshel.tar.gz /renwolesshel 解压tar.gz格式压缩包 # tar zxvf renwolesshel.t ...

- Linux下的目录

FHS 因为利用Linux来开发产品或distributions的社群/公司与个人实在太多了, 如果每个人都用自己的想法来配置文件放置的目录,那么将可能造成很多管理上的困扰. 你能想象,你进入一个企业 ...

- C语言:头文件ctype.h的内置函数

#include <stdio.h> #include <ctype.h>//内置函数的头文件 #include <math.h> int main() { int ...

- IPv6 — 实践

目录 文章目录 目录 前文列表 常用命令 开启/关闭 IPv6 支持 在 CentOS7 上配置 IPv6 地址 自动获取链路本地地址 配置静态全球唯一地址 配置临时 IPv6 地址 添加 IPv6 ...

- Python 将PowerPoint (PPT/PPTX) 转为HTML

PPT是传递信息.进行汇报和推广产品的重要工具.然而,有时我们需要将这些精心设计的PPT演示文稿发布到网络上,以便于更广泛的访问和分享.本文将介绍如何使用Python将PowerPoint文档转换为网 ...

- Android OpenMAX(五)高通OMX Core实现

上一节了解了OMX Core提供的内容,这一节我们看看高通OMX Core是如何实现的.本节代码参考自: omx_core_cmp.cpp registry_table_android.c qc_om ...

- WPF开发快速入门【0】前言与目录

前言 WPF是一个生不逢时的技术,刚推出的时候由于是XP时代,WPF技术有两个不方便的地方: 1.由于操作系统没有自带Framework,需要另外安装,比较麻烦: 2.程序第一次启动时,由于要加载Fr ...

- 『手撕Vue-CLI』下载指定模板

开篇 经上篇文章的介绍,实现了获取下载目录地址,接下来实现下载指定模板的功能. 背景 通过很多章节过后,已经可以拿到模板名称,模板版本号,下载目录地址,这些信息都是为了下载指定模板做准备的. 实现 如 ...

- tab切换之循环遍历

<style> *{ margin: 0; padding:0; } ul,ol,li{ ...