HDLbits——Mt2015 lfsr

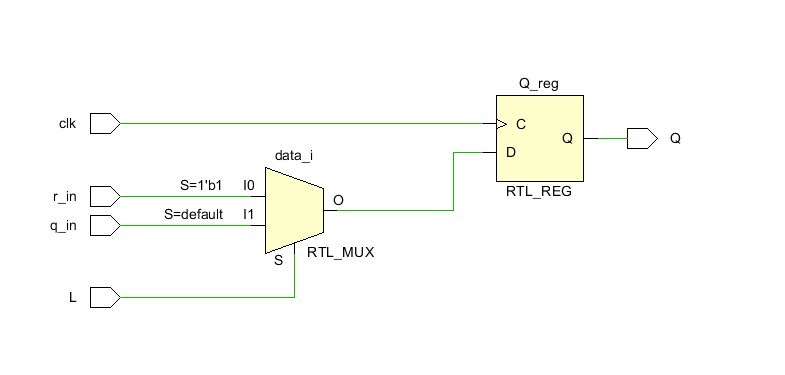

1.描述电路图里面的一个子模块

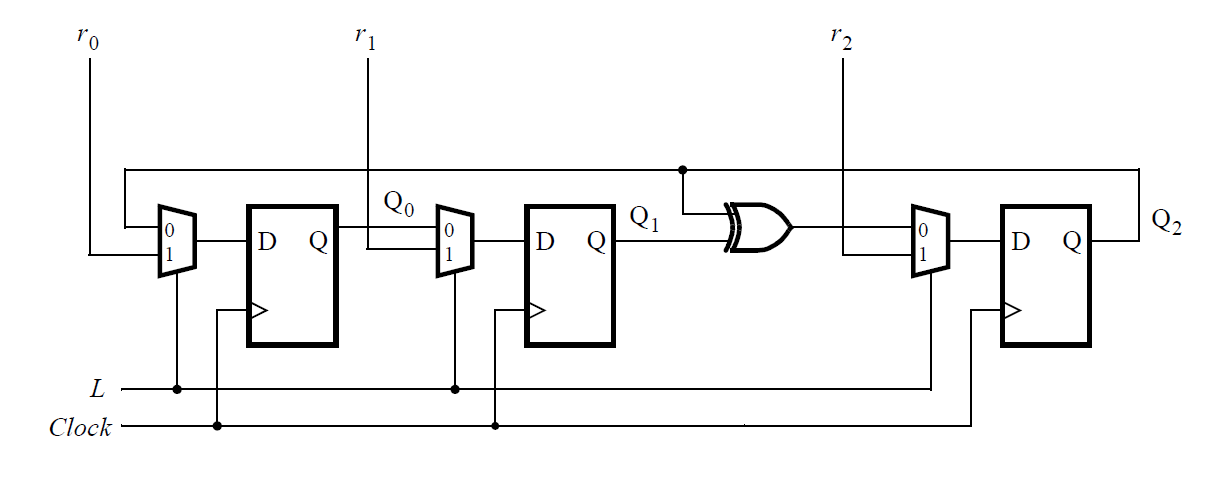

Assume that you want to implement hierarchical Verilog code for this circuit,

using three instantiations of a submodule that has a flip-flop and multiplexer in it.

Write a Verilog module (containing one flip-flop and multiplexer) named top_module for this submodule.

module dff(

input clk,

input q_in,

input L,

input r_in,

output reg Q

);

wire data;

always @(posedge clk) begin

Q <= data;

end

assign data = L ? r_in:q_in;

endmodule

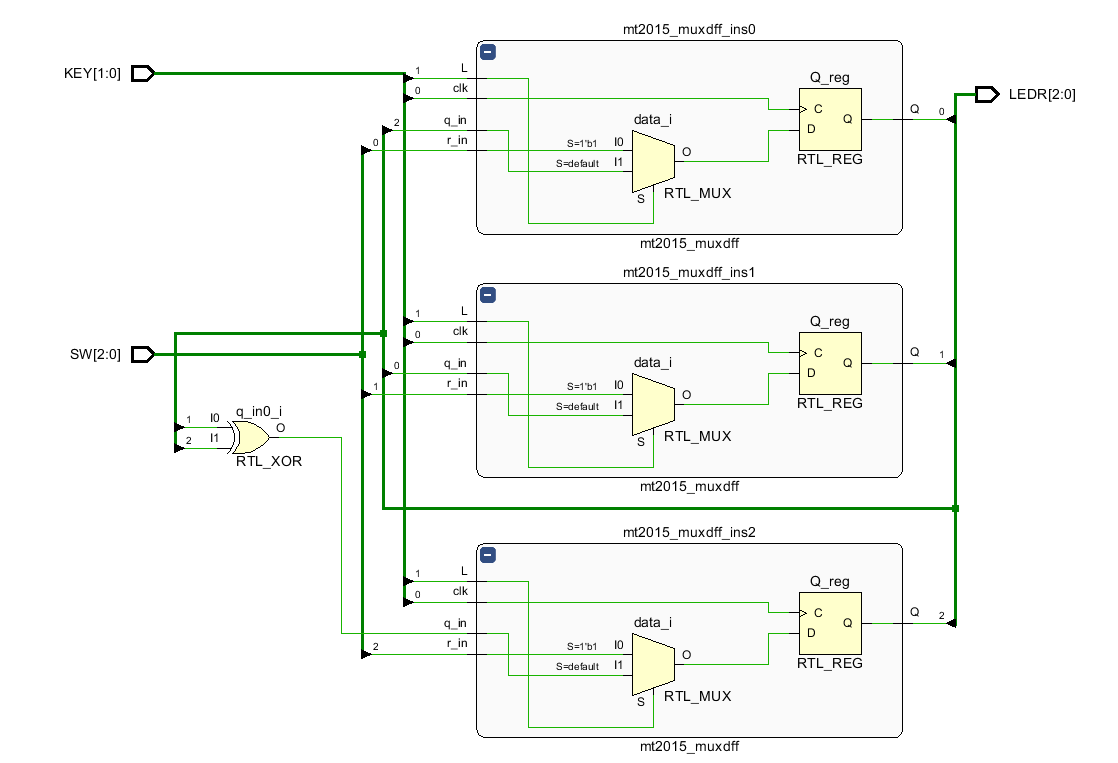

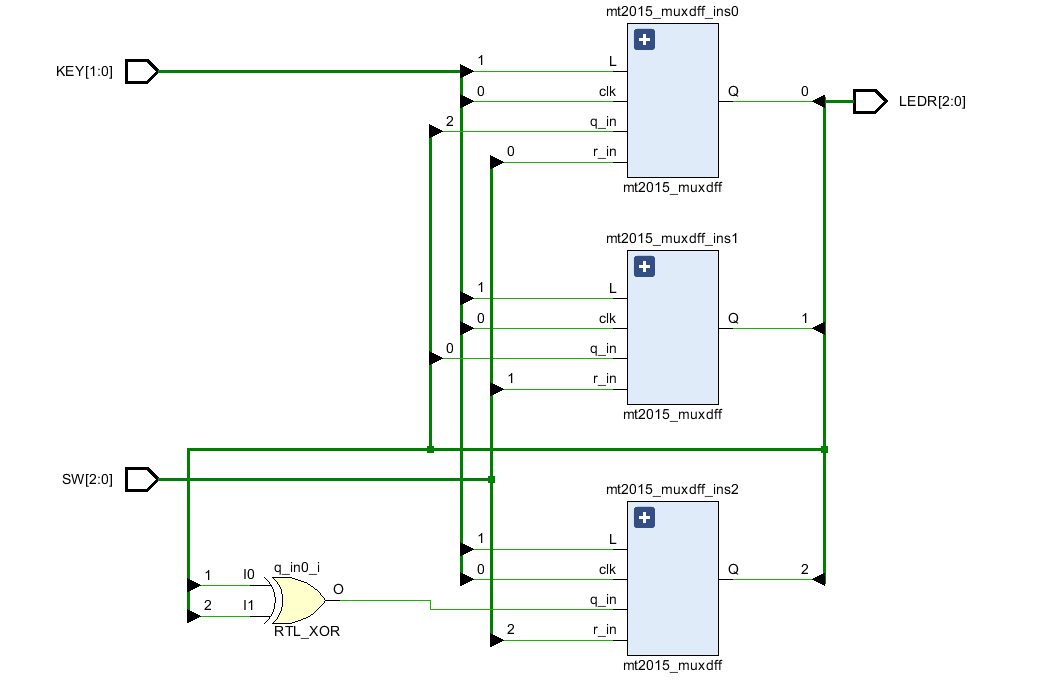

2.例化子模块

Write the Verilog code for this sequential circuit (Submodules are ok, but the top-level must be named top_module).

Assume that you are going to implement the circuit on the DE1-SoC board.

Connect the R inputs to the SW switches, connect Clock to KEY[0], and L to KEY[1]. Connect the Q outputs to the red lights LEDR.

```C

//Connect the R inputs to the SW switches, connect Clock to KEY[0], and L to KEY[1].

//Connect the Q outputs to the red lights LEDR.

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

wire Q_0;

mt2015_muxdff mt2015_muxdff_ins0(

.clk(KEY[0]),

.L(KEY[1]),

.q_in(LEDR[2]),

.r_in(SW[0]),

.Q(LEDR[0])

);

mt2015_muxdff mt2015_muxdff_ins1(

.clk(KEY[0]),

.L(KEY[1]),

.q_in(LEDR[0]),

.r_in(SW[1]),

.Q(LEDR[1])

);

mt2015_muxdff mt2015_muxdff_ins2(

.clk(KEY[0]),

.L(KEY[1]),

.q_in(LEDR[1]^LEDR[2]),

.r_in(SW[2]),

.Q(LEDR[2])

);

endmodule

module mt2015_muxdff(

input clk,

input q_in,

input L,

input r_in,

output reg Q

);

wire data;

always @(posedge clk) begin

Q <= data;

end

assign data = L ? r_in:q_in;

endmodule

RTL原理图

HDLbits——Mt2015 lfsr的更多相关文章

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- 尝试设计LFSR加密器,并用CAP4验证随机性

在CPA4软件中有提供设计LFSR加密器的功能: 输入LFSR的大小,初始密钥,还有反馈密钥. 点击Set Key后点击Show LFSR 观察LFSR,发现初始密钥是1101,转成十六进制是D,反馈 ...

- 使用LFSR搭建误差补偿系统

使用LFSR搭建误差补偿系统 首先弄明白什么是LFSR 线性反馈移位寄存器(LFSR)是内测试电路中最基本的标准模块结构,既用作伪随机测试码产生器,也作为压缩测试结果数据的特征分析器. 一个n阶的LF ...

- FPGA入门实例一:LFSR

一:任务: 要求使用Verilog语言在Xilinx Virtex-6开发板上实现线性反馈移位寄存器(LFSR)的硬件逻辑设计. 二:前期准备: 基本上完成一个简单的设计需要用到以下几个软件 逻辑:U ...

- 线性反馈移位寄存器(LFSR)-非线性反馈移位寄存器的verilog实现(产生伪随机数)

一.线性反馈移位寄存器(LFSR) 通过对事先选定的种子做运算使得人工生成的伪随机序列的过程,在实际中,随机种子的选择决定了输出的伪随机序列的不同,也就是说随机种子的选择至关重要. 产生伪随机数的方法 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- 线性反馈移位寄存器(LFSR)

LFSR用于产生可重复的伪随机序列PRBS,该电路有n级触发器和一些异或门组成,如下图所示. 其中,gn为反馈系数,取值只能为0或1,取为0时表明不存在该反馈之路,取为1时表明存在该反馈之路:这里的反 ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

随机推荐

- linux开放指定端口

sudo ufw allow 端口号

- 数据库基础day1

数据库基础 MySQL概述 SQL 函数 概念 函数 是指一段可以直接被另一段程序调用的程序或代码. 3.1字符串函数 函数 功能 CONCAT(S1,S2,...Sn) 字符串拼接,将S1,S2,. ...

- vue跨行跨列动态表格生成

一.思路步骤: 根据后台传输的数据进行格式转化: 索引为多少的时候进行跨行: <table id="table"> <thead> <tr> & ...

- CodeGym自学笔记08——交互对象

交互对象 用 Java 语言编写的每个程序都由类和对象组成. 1."Java 程序员就像设计工程师一样,只是他们不制作蓝图,而是编写类.船舶零件是根据蓝图制造的,而对象是基于类创建的.&qu ...

- C语言的qsort函数

C函数----qsort 函数 qsort()看起来和C++的sort()差不多,但是其实差别很大, qsort的cmp函数,传入的是指针,返回值是int sort的则传入值,返回值是bool 当qs ...

- TP开发项目时遇到的问题记录

1.下载功能. TP自带Http下载类,使用时new一个就行,示例代码: public function download(){ //接收公文id $id = I('get.fid'); //根据公文 ...

- 2023-03-02 TypeError: null is not an object (evaluating 'ImageCropPicker.openPicker')

问题描述:rn项目使用到了一个插件react-native-image-crop-picker,运行后报错. 原因:安装该插件的时候没有link到android包里. 解决方案: react-nati ...

- Android使用volley发送带参数的post请求

用参数方式可以解决E/Volley: [777] BasicNetwork.performRequest: Unexpected response code 500 for XXXXX 1.Strin ...

- verilog 和system verilog 文件操作

1. 文件操作 Verilog具有系统任务和功能,可以打开文件.将值输出到文件.从文件中读取值并加 载到其他变量和关闭文件. 1.1 Verilog文件操作 1.1.1 打开和关闭文件 module ...

- sqlalchemy+pandas:错误 'OptionEngine' object has no attribute 'execute','str' object has no attribute '_execute_on_connection'

场景:使用 sqlalchemy+pandas 1. 'OptionEngine' object has no attribute 'execute' import pandas as pd fro ...