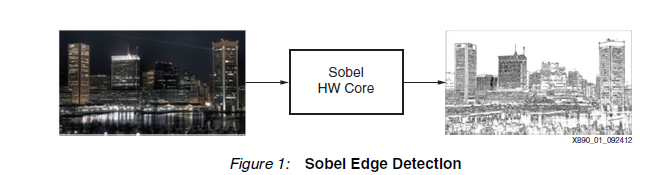

zedboard zynq 学习 sobel 边缘检测 IP核 制作 根据 文档 Xapp890

官方文档http://www.xilinx.com/support/documentation/application_notes/xapp890-zynq-sobel-vivado-hls.pdf

准备工作

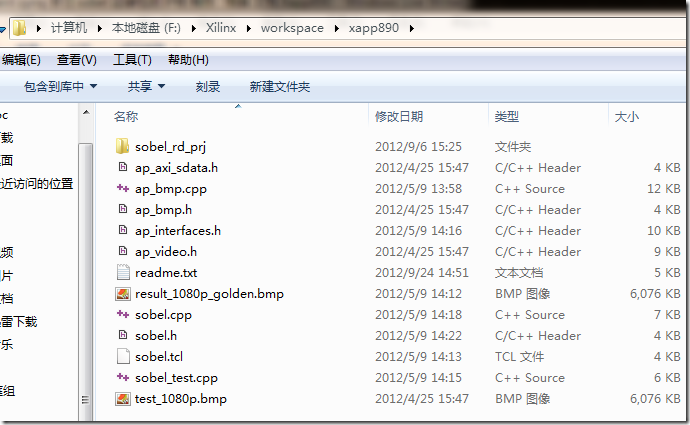

下载 工程文件 http://pan.baidu.com/s/1eQqwjBk 这是我用百度云分享的

如果不行了, 可以用 官方链接 https://secure.xilinx.com/webreg/clickthrough.do?cid=193509

sobel 算子边缘检测原理 这里不多说

就是一个卷积的过程 提取图片的边缘

例子

C代码如下

for(i = 0; i < height, i++){

for(j=0; j < width; j++){

x_dir = 0;

y_dir = 0;

if((i > 0 && (i < (height-1)) && (j > 0) && (j < (width-1))){

for(rowOffset = -1; rowOffset <= 1; rowOffset++){

for(colOffset = -1; colOffset <=1; colOffset++){

x_dir = x_dir + input_image[i+rowOffset][j+colOffset]* Gx[1+rowOffset][1+colOffset];

y_dir = y_dir + input_image[i+rowOffset][j+colOffset]* Gy[1+rowOffset][1+colOffset];

}

}

edge_weight = ABS(x_dir) + ABS(y_dir);

output_image[i][j] = edge_weight;

}

先把下载的压缩包在你的工作空间解压

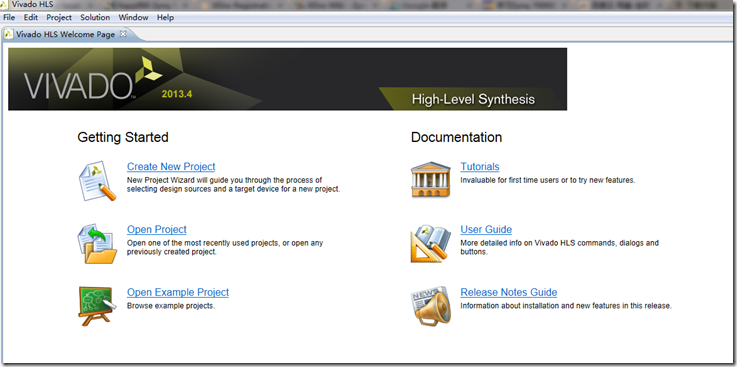

那么接下来 打开vivado HLS 注意不是 vivado

点击 Open Project

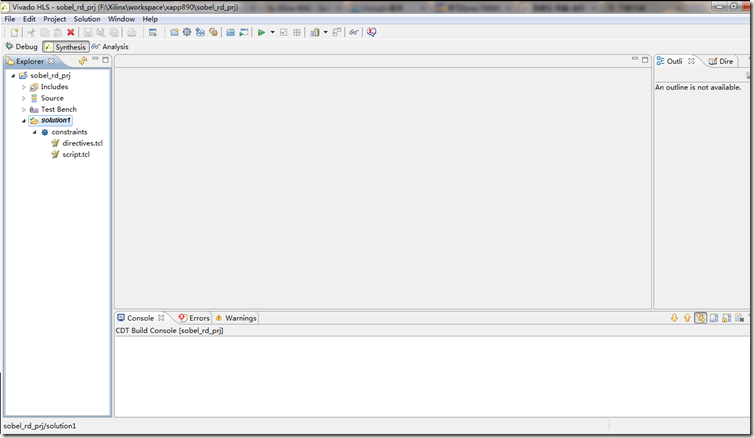

打开刚才解压的工程 xapp890\sobel_rd_prj 点击 ok

有如下界面

这是eclipse 改的

Source中是cpp文件

Test Bench中是 测试文件

可以看到 sobel_test.cpp 里面有 main函数

点击  生成RTL级算法文件

生成RTL级算法文件

如果有FLEXnet Licensing error:-5,357

去申请一个30天试用license 教程 http://blog.sina.com.cn/s/blog_6759fd540101huec.html

可以看到 syn下面 有 Verilog 和 vhdl 文件夹 这就是生成的算法

然后点击 间HDL文件打包 传给EDK

间HDL文件打包 传给EDK

好,后面我也不知道了。 不想学习,去玩耍了

zedboard zynq 学习 sobel 边缘检测 IP核 制作 根据 文档 Xapp890的更多相关文章

- OpenCV训练分类器制作xml文档

OpenCV训练分类器制作xml文档 (2011-08-25 15:50:06) 转载▼ 标签: 杂谈 分类: 学习 我的问题:有了opencv自带的那些xml人脸检测文档,我们就可以用cvLoad( ...

- PHP制作pdf文档方法

原文:PHP制作pdf文档方法 本篇博客是在看完 php+mysql web书以后自己的测试代码,虽然是测试代码,但不是简单的粘贴复制,为了学习thinkPHP框架,自己就用这个来做的,而且这本书已经 ...

- 关于如何利用Pocket CHM Pro制作帮助文档

关于如何利用Pocket CHM Pro制作帮助文档 编写人:CC阿爸 2015-4-6 今天在这里,我想与大家一起分享如何利用Pocket CHM Pro制作软件系统的帮助文档,在此做个小结,以供参 ...

- python_docx制作word文档

一.docx模块 Python可以利用python-docx模块处理word文档,处理方式是面向对象的.也就是说python-docx模块会把word文档,文档中的段落.文本.字体等都看做对象,对对象 ...

- Altera DDR2 IP核学习总结3-----------DDR2 IP核的使用

根据上一篇生成的IP核,例化之后如上图,Local开头的数据是用户侧数据,其他数据暂时不用纠结,不用管. 这些是需要关注的信号,但是初学阶段很难对这些信号形成具体的概念,这里参考明德扬的代码进行二次封 ...

- Altera DDR2 IP核学习总结2-----------DDR2 IP核的生成

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next PLL reference clock frequency填入板子晶振的频率50MHZ,这里设 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- QuickChm 制作chm文档 chm文档脚本错误,乱码

最近学习bootstrap,到网上找了一些chm格式的文档,发现有些老旧,于是决定自己制作一个 用过以下这些chm制造器,包括easychm,chm精灵,chmeditor,chmfactory等等, ...

随机推荐

- Spring Security 之Session管理配置

废话不多说,直接上代码.示例如下: 1. 新建Maven项目 session 2. pom.xml <project xmlns="http://maven.apache.o ...

- django.template.exceptions.TemplateSyntaxError: 'article_tags' is not a registered tag library.

django.template.exceptions.TemplateSyntaxError: 'article_tags' is not a registered tag library. Must ...

- 递归遍历目录拷贝cdh下的lib到一个目录

destpath='/home/hadoop/soft/hadoop-2.0.0-cdh4.5.0/cdhlib/'jarpath='/home/hadoop/soft/hadoop-2.0.0-cd ...

- JavaScript你必须掌握的8大知识点

一:JavaScript思维导图之<基本dom操作> 二.JavaScript思维导图之<变量>的学习 三. JavaScript思维导图之<函数基础> 四.J ...

- 一篇SSM框架整合友好的文章(一)

转载请标明出处: http://blog.csdn.net/forezp/article/details/53730333 本文出自方志朋的博客 最近实在太忙,之前写的<rxjava系列文章&g ...

- python解析ini文件

python解析ini文件 使用configparser - Configuration file parser sections() add_section(section) has_section ...

- tomcat.apache startup.bat闪退两种解决方法

tomcat bin文件夹中的startup.bat闪退原因及解决方法两种 方法一:在启动tomcat时闪退,重新检查java的jre运行环境.如果环境变量忘记配置一定会导致了tomcat的闪退. 追 ...

- Python——列表

应用场景,要统计大量的人员信息.就可以用列表的形式进行.name = ['邱秀','玄永俊','杨栋豪']查:print(name[2],name[0]) #取号码进行识别print(name[1:3 ...

- js、jquery中全局替换replace

str.replace(/需要替换的/g,"新字符串") //此处使用正则表达式

- spring cloud 学习之服务消费者(Feign)

一.Feign简介 Feign是一个声明式的伪Http客户端,它使得写Http客户端变得更简单.使用Feign,只需要创建一个接口并注解.它具有可插拔的注解特性,可使用Feign 注解和JAX-RS注 ...