Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器。在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还是有一些不方便,所以我便直接使用Modelsim独立仿真,但是对于IP Core的话,就需要添加Vivado IP Core的库文件,本人查阅了很多资料,最终实现了使用Modelsim仿真Vivado Clocking Wizard IP Core,软件版本,Vivado 2017.3、Modelsim SE10.4。具体流程如下,实测记录。

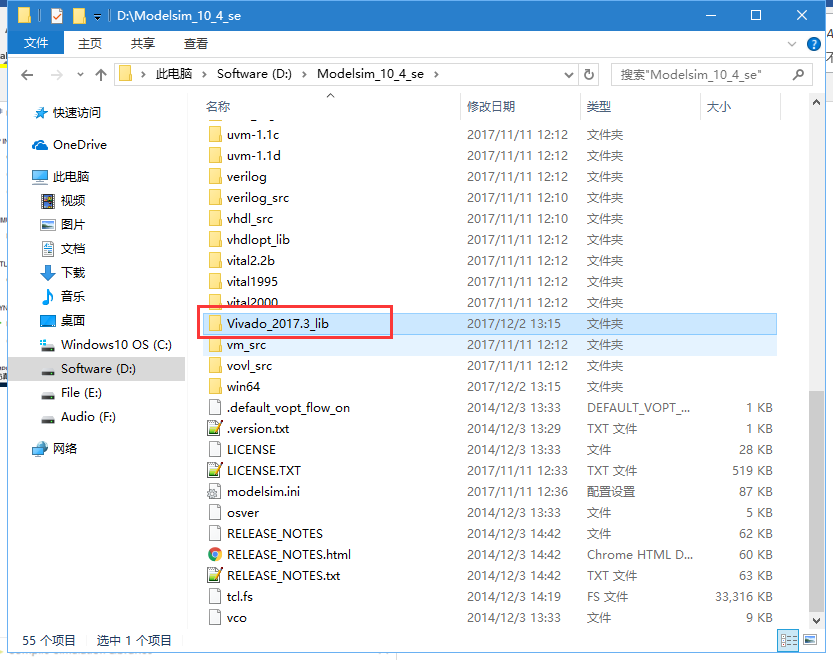

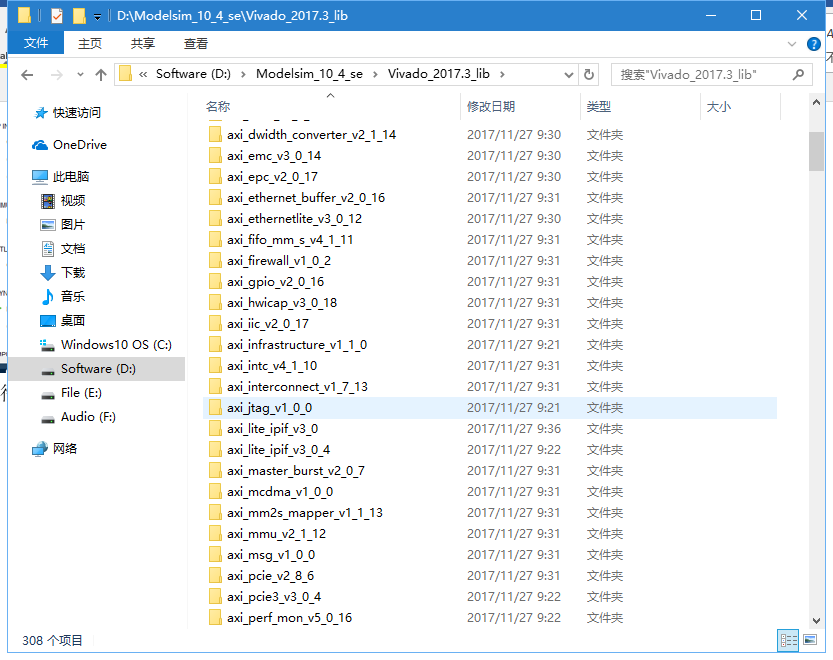

首先,在 Modelsim 的安装目录下新建一个文件夹,我这里是D:\Modelsim_10_4_se\Vivado_2017.3_lib

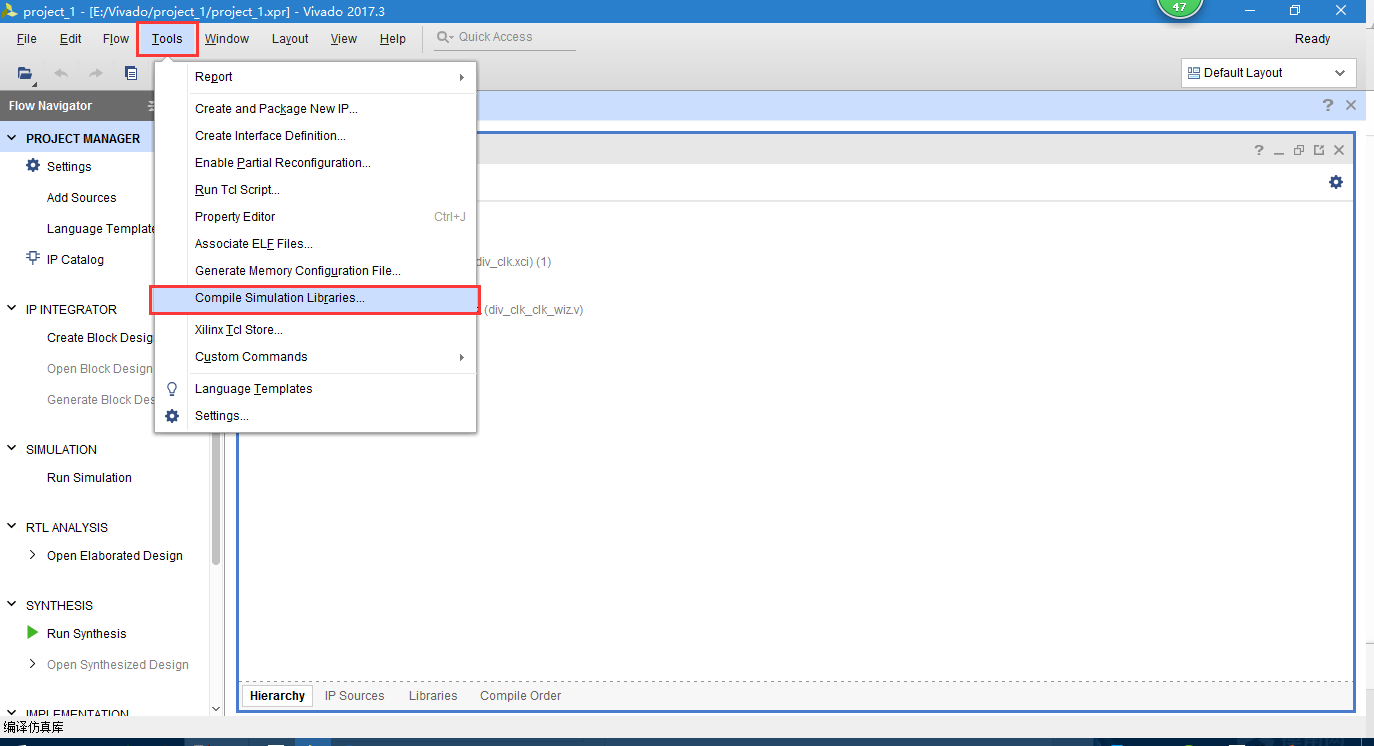

然后,打开Vivado软件,主界面菜单栏点击Tools下的Compile Simulation Libraries编译Vivado仿真库

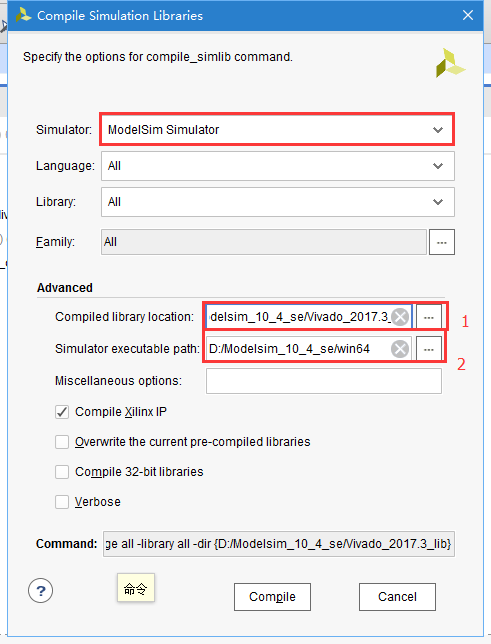

弹出如下窗口然后按如图所示选择,1处路径为刚才我们新建的文件夹中,2处为Modelsim的运行程序路径。设置好后点击compile。

在编译的过程中窗口会打印出来如下信息。

等待一段时间,Vivado的库文件编译完成后我们可以看到文件夹下都是Vivado的库文件

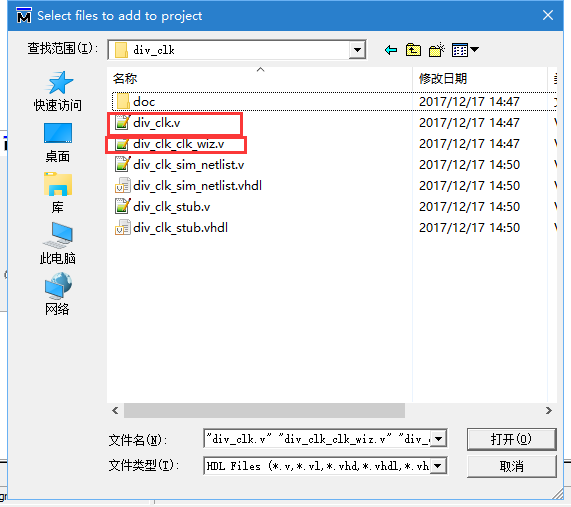

然后使用Vivado新建一个调用的Clocking Wized IP Core的工程,编写好测试文件,然后再用Modelsim新建一个仿真工程,将测试文件和顶层添加进来。这里省略掉这些步骤。这里需要将IP Core中生成的两个文件添加进来,如下图所示。

直接在work右键点击test bench文件进行仿真会出现如下错误,这是因为没有添加所仿IP Core的库文件

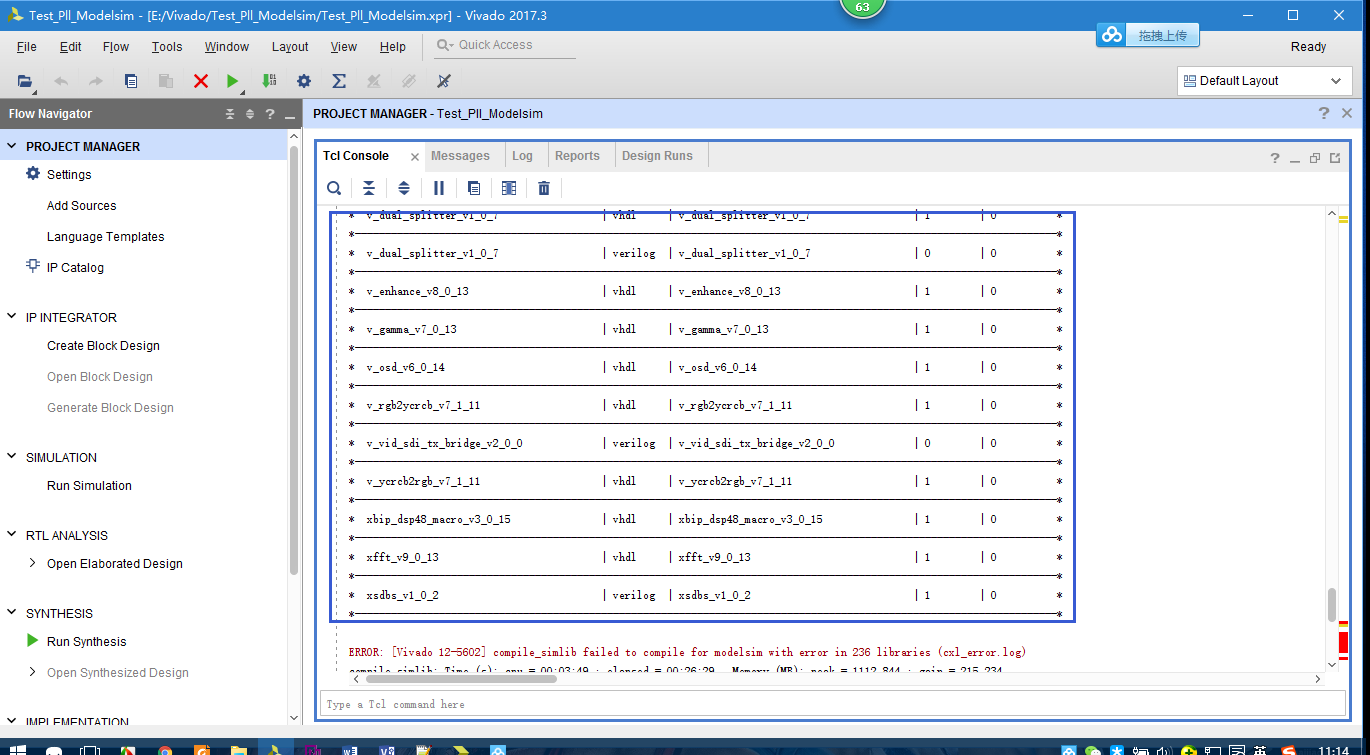

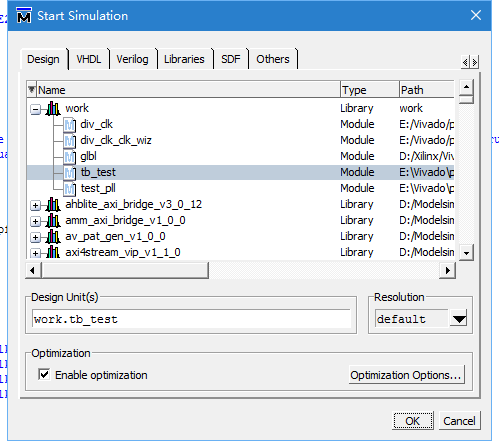

点击标题栏simulator——start simulator,在work里选中test bench。

点击libraries,点击添加所需要的库,这里只需要simprims_ver

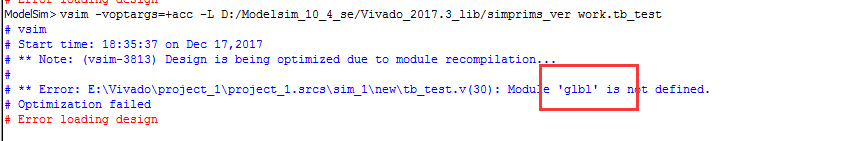

点击这里后还是会出现错误,打印出来的信息如下,提示缺少glbl模块,

这是Xilinx的全局复位模块,该模块的路径在你Vivado的安装路径里,比如我的是D:\Xilinx\Vivado2017.3\Vivado\2017.3\data\verilog\src中,把它添加到工程里面,在test bench中如图所示例化一下这个模块,然后重新仿真一次。

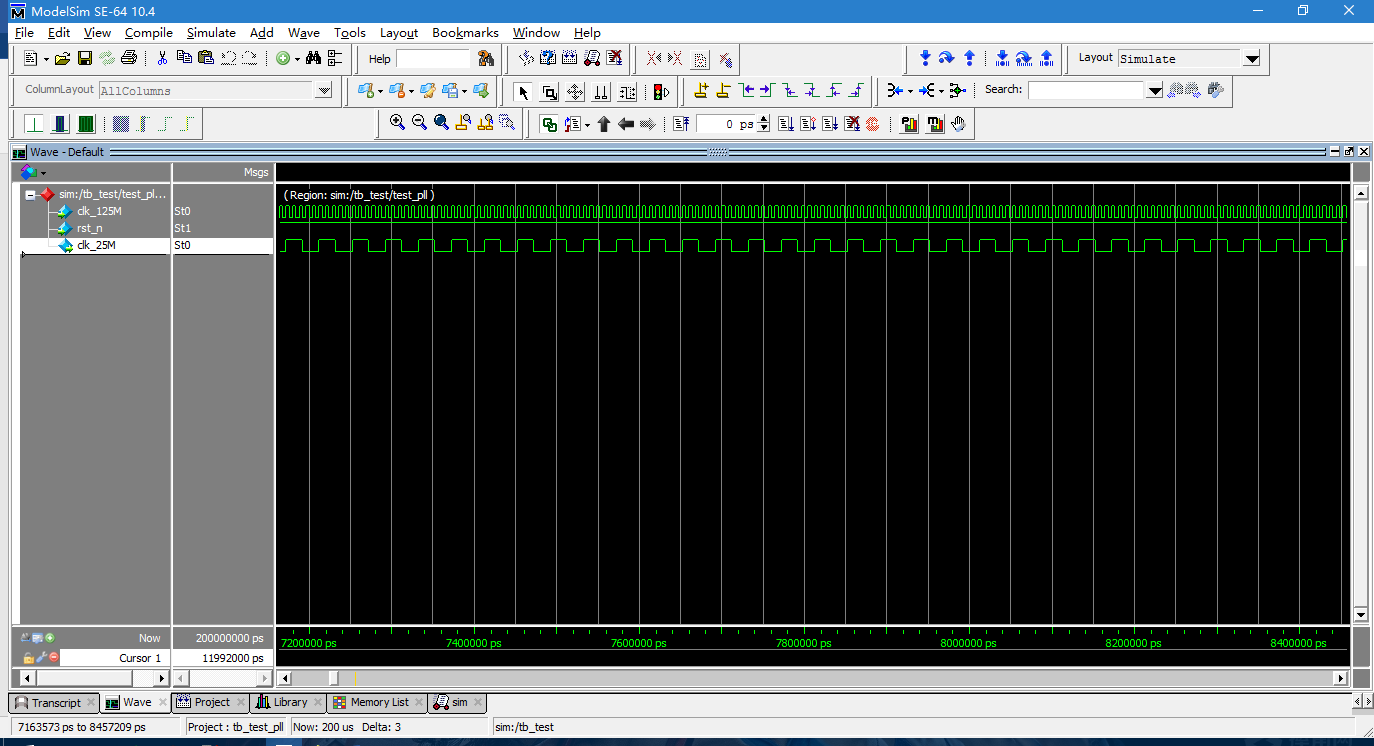

然后就可以看到波形了

我这里的测试工程师一个125Mhz分25Mhz的五分频。

接下来本人会继续尝试使用Modelsim仿真FIFO、RAM/ROM、Shift_RAM等常用IP Core,如果你有什么更加高效的方法,欢迎提出,欢迎指点。如果需要Modelsim软件请关注我的微信订阅号:开源FPGA,后台回复“Modelsim”即可获得,欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8305925.html

Modelsim独立仿真Vivado Clocking Wizard IP Core的更多相关文章

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- [Xilinx]Modelsim独立仿真Vivado生成的PLL核

EDA Tools: 1.Vivado 2015.1(64-bit) 2.Modelsim SE-64 10.1c Time: 2016.05.26 ------------------------- ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- Vivado&ISE&Quartus II调用Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真

Vivado中的MIG已经集成了modelsim仿真环境,是不是所有IP 都有这个福利呢,不知道哦,没空去验证. 第一步:使用vivado中的MIG IP生成一堆东西 ,这个过程自己百度.或者是ug5 ...

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- Vivado 与 Modelsim 联合仿真

1 编译库 用命令行 用vivado工具 vivado 有很多 IP核的接口 已经与 ISE的核 不太一样了,比如fir ,接口就是这样的: fir_lp fir_lp_ip( .aclk ( ...

随机推荐

- springboot整合redis

springboot-整合redis springboot学习笔记-4 整合Druid数据源和使用@Cache简化redis配置 一.整合Druid数据源 Druid是一个关系型数据库连接池,是阿 ...

- vue2.0---vue-router总结(项目基于vue-cli)

vue2.0---vue-router总结(项目基于vue-cli) 1. 在项目中安装: npm install vue-router --save 2. 在项目中的引入: // The Vue b ...

- Java实现的电脑已连接WiFi热点的导入导出小工具

很多时候我们电脑连接了很多无线WiFi,只要连接过一次,电脑就会记下该热点的密码,方便我们下一次连接.但是问题来了,一旦我们重装系统,之前连接过的WiFi就丢失了,想要连接就得再输入密码,为了 解决这 ...

- 为什么覆写equals()方法的时候总是要覆写hashcode()?

要回答这个问题,我们应该先认识一下obj中的equals和hascode方法 1.equals()方法在obj中定义如下: public boolean equals(Object obj) { re ...

- 【java】获取当前环境属性及编码乱码示例

package 字符编码; import java.io.File; import java.io.FileOutputStream; import java.io.IOException; impo ...

- sqlserver 存储过程 分页搜索查询

具体调用实例见代码最后一行注释区域 --if exists(select * from sysobjects where id = object_id(N'page_search') and type ...

- Jstree 使用CheckBox插件 选中父节点时被禁用的子节点也会选中问题

问题描述: 最近用jstree遇到一个问题,使用CheckBox插件时,当父节点选中时,被禁用的子节点也会选中如下 解决方案: 1. 将jstree升级到最新的版本,v3.3.4及以上就可以 2. ...

- DCL的失效:现实与初衷的背离

最近看了Brian Goetz写的一篇有关DCL的文章:Double-checked locking: Clever, but broken.( 2001年发表于JavaWorld上) 这篇文章讲述了 ...

- Hello TensorFlow 三 (Golang)

在一台ubuntu 16.04.2虚拟机上为golang安装TensorFlow. 官方参考:https://www.tensorflow.org/install/install_go 首先安装go ...

- 由于DG Broker的配置导致RAC某实例无法mount

今天碰到一个我自己实验室发生的故障,起初看起来很简单,但实际上还很有趣,而且不细心的话还容易被忽视掉.相信在生产环境也会有客户会实际遇到. 环境:Oracle 11.2.0.4 RAC (2 node ...