SDRAM和dcfifo的联合

SDRAM和dcfifo的联合

设计原理

在"SDRAM突发读写页"实验中,留下了一个问题,就是从SDRAM读取数据的速度要与SDRAM的驱动时钟同步,这就造成了读出的数据的速率过快,我们很难通过在LED上观察其读出的结果。

在学习了dcfifo之后相信你已经了解了dcfifo的功能,没错这一节就是要用到dcfifo作为跨时域的桥梁,把100M的读时钟频率"降下来"。

通过测试模块往SDRAM写入一页的数据,当写如完成后便进入到延迟状态(当然这个延迟我们可以不要),延迟完成后接着进入到读数据状态,在读数据状态中分为两个部分:一个是写dcfifo,即在读出SDRAM的数据的同时将读出的数据写如dcfifo中,在读完SDRAM内部的256个数据之后也就是对dcfifo写完成了,这个过程读SDRAM和写dcfifo的时钟频率是100M。接着对dcfifo进行读操作,这里的读时钟是50M,在读完成后便接着再对SDRAM进行读操作,以此循环…………

SDRAM突发读写一页的接口

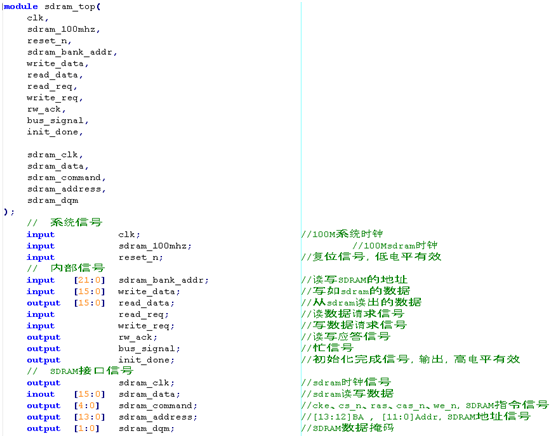

在"SDRAM突发读写页"实验中,驱动SDRAM的顶层接口如下图所示,主要分为3个部分,分别为系统信号、内部信号、SDRAM接口信号。其中系统信号为时钟信号和复位信号,内部信号为读写数据信号和读写控制信号,SDRAM接口信号为FPGA与外部的SDRAM的接口。

该是实验中,系统信号、SDRAM接口信号都很简单,只需配置好其硬件所对应的引脚,当然这里的时钟来源于PLL的倍频时钟。而内部信号要与dcfifo、测试模块进行连接,这也是本节的重点内容。

由于dcfifo只负责接收从SDRAM读出的数据,所以SDRAM顶层模块中的:read_req和read_data需要和dcfifo的顶层模块相连接,read_req也就是dcfifo的写使能write_reg。

异步dcfifo读写的接口

fifo_top只负责接收SDRAM的读出数据,并将其写入到fifo内部,然后再用低的时钟频率将数据读出。

顶层接口信号中的write_reg连接SDRAM的读申请信号read_req,因为读SDRAM的同时对fifo进行写操作,所以SDRAM的数据输出read_data连接到dcfifo的数据输入data_in,read_over用于反馈dcfifo的读操作完成,可以再往fifo内部写入数据。

接口拼接

测试模块

写操作

在判断SDRAM初始化完成后init_done有效,则对SDRAM进行写操作,发送写申请信号的同时发送写数据和写地址信号,在连续写入256个数据后判断rw_ack是否有效,有效则写入完成,将写申请信号清零,进入到延迟状态,延迟一定的时间。

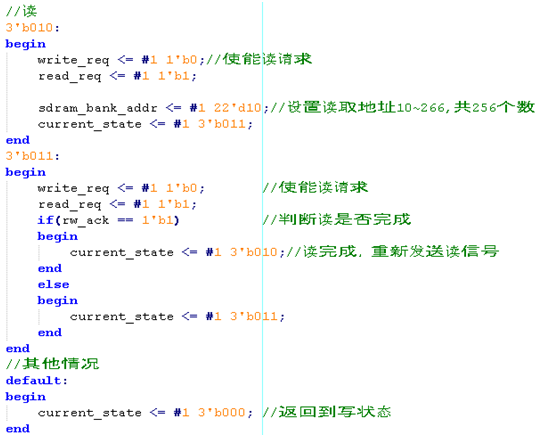

读操作

在延迟一定的时间后便进入到读操作,这时读申请信号有效,并同时发送读地址信号,在下一个状态中判断读操作是否完成(rw_ack是否为1),记住此时也是在对dcfifo进行写操作,当rw_ack有效时,则停止对SDRAM进行读操作,也停止对dcfifo进行写操作,此时进入到对dcfifo进行读操作,当read_over为1时表明对dcfifo读完成,便转入到对SDRAM读操作中,以此循环。

实验效果

实验的工程文件为"sdram_rw_page_fifo",其源代码文件如下:

实验中采用signaltap对输出到LED的数据进行观察,结果如下:

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

SDRAM和dcfifo的联合的更多相关文章

- 46.谈谈SDRAM的作用

SDRAM这个至今还在用的存储器,虽然被后来的DDR取代,掌握好它还是很重要的.之前在调试时,确实费了好大劲,它的复杂性毋庸置疑,一般人要想弄懂他,得花1个月左右吧,至少我这么认为.话说回来,SDRA ...

- SRAM、DRAM、SDRAM、DDR、DDR2、DDR3

RAM可分为SRAM(Static RAM/静态存储器)和DRAM(Dynamic RAM/动态存储器).SRAM是利用双稳态触发器来保存信息的,只要不掉电,信息是不会丢失的.SRAM存储元件所用MO ...

- 【黑金原创教程】【FPGA那些事儿-驱动篇I 】实验十九:SDRAM模块② — 多字读写

实验十九:SDRAM模块② — 多字读写 表示19.1 Mode Register的内容. Mode Register A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A ...

- 编写SDR SDRAM页突发模式控制器的注意点-下篇

本来是没打算写这些的,但是后面逐渐发现点问题,所以决定再写一个下篇来补充说明一下. 图一 细心的网友会发现上篇末尾的打印是有点问题的,因为我的数据产生器产生的是1-200,1-200,1-200,1- ...

- 编写SDR SDRAM页突发模式控制器的注意点

网上有很多的SDR SDRAM控制器的代码,但都是基于burst1/2/4/8模式下的,这种模式下传输高速的相机数据还是有点拮据的,所以花了几天把这些模式改造成了页突发模式.我的这个控制器模型是这样的 ...

- 模拟摄像头解码模块最新测试 TVP5150模块 FPGA+SDRAM+TVP5150+VGA 实现PAL AV输入 VGA视频输出

模拟摄像头解码模块最新测试 TVP5150模块 FPGA+SDRAM+TVP5150+VGA 实现PAL AV输入 VGA视频输出 测试使用电视机顶盒的AV模拟信号输入,VGA显示器输出测试,效 ...

- Dynamics CRM 之ADFS 使用 WID 的独立联合服务器

ADFS 的使用 WID 的独立联合服务器适用于自己的测试环境,常用的就是在虚机中使用. 拓扑图如下: wID:联合身份验证服务配置为使用 Windows 内部数据库

- Dynamics CRM 之ADFS 使用 WID 的联合服务器场

使用 WID 的联合服务器场 默认拓扑 Active Directory 联合身份验证服务 (AD FS) 是联合服务器场,使用 Windows 内部数据库 (WID). 在这种拓扑, AD FS 使 ...

- Hibernate(5)—— 联合主键 、一对一关联关系映射(xml和注解) 和 领域驱动设计

俗话说,自己写的代码,6个月后也是别人的代码……复习!复习!复习!涉及的知识点总结如下: One to One 映射关系 一对一单向外键(XML/Annotation) 一对一双向外键关联(XML/A ...

随机推荐

- Servlet/JSP-08 EL表达式

EL - Expression Language 一. 基本语法 EL表达式以 ${} 的形式访问变量的值 1. "." 和 "[]" 运算符 <%@ p ...

- 烂泥:KVM、kickstart与nginx集成

本文由秀依林枫提供友情赞助,首发于烂泥行天下. 前几篇文章介绍了FTP.NFS与KVM.kickstart集成的案例,从这篇文章开始,我们来介绍HTTP方式与KVM.kickstart集成. HTTP ...

- Mycat实现读写分离,主备热切换

实验环境:ubutu server 14 Master IP:172.16.34.212 Slave IP:172.16.34.34.156 Mycat server IP:172.16.34.219 ...

- LeetCode #303. Range Sum Query

问题: Given an integer array nums, find the sum of the elements between indices i and j (i ≤ j), inclu ...

- [转]在ASP.NET开发中容易忽略的2个小问题 Cookie乱码存取异常 和 iframe弹框的login跳转

本文转自:http://www.cnblogs.com/outtamyhead/p/3642729.html 本文地址:http://www.cnblogs.com/outtamyhead/p/364 ...

- python读取excel并制表输出

源码如下: #!/usr/bin/python #coding=UTF-8 import xlrd import sys from texttable import Texttable def she ...

- POJ 3384 Feng Shui --直线切平面

题意:房间是一个凸多边形,要在里面铺设两条半径为r的圆形地毯,可以重叠,现在要求分别铺设到哪,使地毯所占的地面面积最大. 解法:要使圆形地毯所占面积最大,圆形地毯一定是与边相切的,这样才能使尽量不重叠 ...

- POJ2157Maze[DFS !]

Maze Time Limit: 2000MS Memory Limit: 65536K Total Submissions: 3818 Accepted: 1208 Description ...

- POJ1985Cow Marathon[树的直径]

Cow Marathon Time Limit: 2000MS Memory Limit: 30000K Total Submissions: 5117 Accepted: 2492 Case ...

- C#类型转换运算符之 explicit implicit

类型转换运算符 explicit和implicit用于声明用户定义的类型转换运算符,如果可以确保转换过程不会造成数据丢失,则可使用这两个关键字在用户定义的类型和其他类型之间进行转换. explicit ...