8-3编码器,3-8译码器的verilog实现

在数字系统中,由于采用二进制运算处理数据,因此通常将信息变成若干位二进制代码。在逻辑电路中,信号都是以高,低电平的形式输出。编码器:实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码。

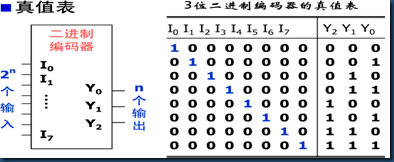

设计一个输入为8个高电平有效信号,输出代码为原码输出的3位二进制编码器。

化简逻辑表达式: 由逻辑表达式可以得出,普通的8-3编码器用或门即可实现。对应的verilog程序如下:

由逻辑表达式可以得出,普通的8-3编码器用或门即可实现。对应的verilog程序如下:

module mb_83(x,y);

input [7:0]x;

output [2:0]y;

reg [2:0]y;

always@(x)

begin

case (x)

8'b00000001:y=3'b000; //当 当 x=8 ’b00000001,则 则 y 输出为 3 ’b000

8'b00000010:y=3'b001; //当 当 x=8 ’b00000010,则 则 y 输出为 3 ’b001

8'b00000100:y=3'b010; //当 当 x=8 ’b00000100,则 则 y 输出为 3 ’b010

8'b00001000:y=3'b011; //当 当 x=8 ’b00001000,则 则 y 输出为 3 ’b011

8'b00010000:y=3'b100; //当 当 x=8 ’b00010000,则 则 y 输出为 3 ’b100

8'b00100000:y=3'b101; //当 当 x=8 ’b00100000,则 则 y 输出为 3 ’b101

8'b01000000:y=3'b110; //当 当 x=8 ’b01000000,则 则 y 输出为 3 ’b110

8'b10000000:y=3'b111; //当 当 x=8 ’b10000000,则 则 y 输出为 3 ’b111

default: y=3'b000;

endcase

end

endmodule

上述编码器有一个缺点,即在某一个时刻只允许有一个有效的输入,而同时若又有两个或两个以上的输入信号要求编码,输出端一定会发生混乱,出现错误。为了解决这个问题,引入了优先编码器。优先编码器的功能是允许同时在几个输入端有输入信号,编码器按照输入信号预先排定的优先顺序,只对同时输入的几个信号中有优先权高位的一个信号编码。

对应的真值表为

对应的verilog程序:(输入信号:i[7:0];输入使能端:ei;输出信号端:y: [2:0];输出使能端eo;优先标志端gs)

module yxbm_83(y,eo,gs,i,ei);

input [7:0] i; //8 位输入 i

input ei; // 使能输入端 ei

output eo,gs; // 使能输出端 eo ,优先标志端 gs

output[2:0] y; //3 位输出 y

reg[2:0] y; //3 位输出寄存器 y

reg eo,gs; // 使能输出寄存器,

always@(i,ei) // 电平触发方式,当 i 跟 跟 ei 有改变的时候,执行以下操作

begin

if(ei==1'b1) //当 ei 为 为 1 的时候

begin

y<=3'b111;

gs<=1'b1;

eo<=1'b1;

end

else

begin

if(i[7]==1'b0) //当 i 的第 8 为 为 0 时候

begin

y<=3'b000;

gs<=1'b0;

eo<=1'b1;

end

else if(i[6]==1'b0) //当 i 的第七位为 0 时候

begin

y<=3'b001;

gs<=1'b0;

eo<=1'b1;

end

else if(i[5]==1'b0) //当 i 的第 6 位为 0 时候

begin

y<=3'b010;

gs<=1'b0;

eo<=1'b1;

end

else if(i[4]==1'b0) //当 i 的第 5 位为 0 时候

begin

y<=3'b011;

gs<=1'b0;

eo<=1'b1;

end

else if(i[3]==1'b0) //当 i 的第 4 位为 0 时候

begin

y<=3'b100;

gs<=1'b0;

eo<=1'b1;

end

else if(i[2]==1'b0) //当 i 的第 3 位为 0 时候

begin

y<=3'b101;

gs<=1'b0;

eo<=1'b1;

end

else if(i[1]==1'b0) //当 i 的第 2 位为 0 时候

begin

y<=3'b110;

gs<=1'b0;

eo<=1'b1;

end

else if(i[0]==1'b0)//当 i 的第 1 位为 0 时候

begin

y<=3'b111;

gs<=1'b0;

eo<=1'b1;

end

else if(i==8'b11111111)//当 i 为 为 8'b11111111 时候

begin

y<=3'b111;

gs<=1'b1;

eo<=1'b0;

end

end

end

endmodule

时序仿真的结果:

译码器(Decoder):把代码状态的特定含义翻译过来的过程为译码。译码器:实现译码操作的逻辑电路,就是把一种代码转换为另一种代码的电路。

译码器与编码器图解:

设计一个具有三个使能端的3-8译码器:

真值表为:3位编码输入端a[2:0],使能输入端g1,g2,g3;输出信号:8位编码输出端y[7:0]。

module ym_3_8(a,g1,g2,g3,y);

input[2:0] a; //3 位 位 2 进制编码输入端

input g1,g2,g3; //3 个使能输入端

output[7:0] y; //8 位编码输出端

reg[7:0] y;

always@(a or g1 or g2 or g3) // 电平触发方式

begin

if(g1==0) y=8'b11111111; // 如果 g1 为 为 0 ,则 y 输出为 11111111

else if(g2==1) y=8'b11111111; // 如果 g2 为 为 1 ,则 y 输出为 11111111

else if(g3==1) y=8'b11111111; // 如果 g3 为 为 1 ,则 y 输出为 11111111

else

case(a[2:0]) // 判断 a 的值,并通过 a 的值来给 y

// 设置输出值

3'b000:y[7:0]=8'b11111110;

3'b001:y[7:0]=8'b11111101;

3'b010:y[7:0]=8'b11111011;

3'b011:y[7:0]=8'b11110111;

3'b100:y[7:0]=8'b11101111;

3'b101:y[7:0]=8'b11011111;

3'b110:y[7:0]=8'b10111111;

3'b111:y[7:0]=8'b11111111;

endcase

end

endmodule

8-3编码器,3-8译码器的verilog实现的更多相关文章

- 03-组合逻辑电路设计之译码器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计 实验平台:无 实验原理: 组合逻辑, ...

- 你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点. 二十进制编码器及Verilog HDL描述 二十进制编码器是数字电路中常用的电路单元 ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- FPGA编程—组合逻辑编码器等verilog实现

本篇博客主要实现对组合逻辑电路的一些常用模块的实现.组合逻辑中,包括译码器,编码器,输入输出选择器,数值比较器,算法单元等. 先来实现编码器,最常用的8-3编码器,这里先讲一下要用到的case ,c ...

- Verilog八线 - 三线优先编码器设计(74LS148)

百度百科_74LS148 if语句法 //8线-3线优先编码器设计(74LS148) // //EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO //0 | ...

- 用Verilog语言设计一个3-8译码器

case语句 if_case语句 源码下载 Github >>

- Verilog三线 - 八线译码器

参阅了一些书籍和网上的写法,在此Mark. 布尔表达式法 module decode3_8_assign (data_in,data_out,enable);//算法实现 :] data_in; in ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- 基础数字电路的Verilog写法

Verilog是硬件描述电路,我对此一直稀里糊涂,于是将锆石科技开发板附带的的一些基础数字电路Verilog程序整理记录下来,并且查看他们的RTL视图,总算有点理解了. 1.基本运算符 module ...

随机推荐

- 为什么重写equals一定要重写hashCode方法?

大家都知道,equals和hashcode是java.lang.Object类的两个重要的方法,在实际应用中常常需要重写这两个方法,但至于为什么重写这两个方法很多人都搞不明白. 下面我们看下Objec ...

- VS 引用dll版本冲突问题

1.删除项目中的对应引用: 2.如果是有用到NetGet引用的删除项目中的packages里面的对应包文件: 3.如果是在NetGet中引用的注释项目中packages.config对应的插件名: 4 ...

- 和我一起,重零开始学习Ant Design Pro开发解决方案(一)安装开发环境

安装NODEJS 什么是NODEJS? 百度一下吧,这个真不知道,老码农,别笑话我: 简单的说 Node.js 就是运行在服务端的 JavaScript.Node.js 是一个基于Chrome Jav ...

- 每周分享五个 PyCharm 使用技巧(六)

大家好,今天我又来给大家更新 PyCharm 的使用技巧. 从今年3月24号开始一直到今天,将近四个月的时间.包括本篇,一共更新了6篇文章,每篇 5 个小技巧,总计 30 个. 这30个使用技巧,全部 ...

- mac上使用gitlab拉项目报错Permissions 0644 for ...

解决办法:执行命令sudo chmod 0600 /Users/***(电脑名)/.ssh/id_rsa

- 记支付宝接口对接,涉及到提取证书SN号的解决方案

支付宝针对.NET SDK并未封装有提取证书SN序列号的方法,仅针对Java平台才有对应的方法(赤裸裸的歧视啊~~) 要想在提取这个SN序列号有两种方案: 1. 直接用Java SDK包来提取SN 2 ...

- Core Animation笔记(特殊图层)

1.shapeLayer: 渲染快速,内存占用小,不会被图层边界裁掉(可以在边界之外绘制),不会像素化(当做3D变化如缩放是不会失真) CGRect rect = self.containerView ...

- Cephfs 部署 创建 metadata 池 data池

上一次部署了ceph分布式存储,接下来我们部署ceph的文件系统.Ceph文件系统至少需要两个RADOS池,一个用于数据,一个用于元数据. 创建metadata 池 后面数字表示 PG 和pgp数 c ...

- [dev][nginx] 在阅读nginx代码之前都需要准备什么

前言 以前,我读过nginx的源码,甚至还改过.但是,现在回想起来几乎回想不起任何东西, 只记得到处都是回调和异步,我的vim+ctags索引起来十分吃力. 几乎没有任何收获,都是因为当时打开代码就看 ...

- 解决pycharm新建项目后按钮灰色问题

解决pycharm新建项目后按钮灰色问题 出现过多次该问题了, 在此记录一下 同样适用于导入别人的新项目后无法运行问题 原因一: pycharm没有设置系统解析器 解决方法一: 打开pycharm-& ...