千兆网数据CRC检验和过滤

项目简述

本次项目在计算机将图像数据信息通过千兆网发送给FPGA后,由于接收到的数据可能混乱和无效,需要对数据CRC校验和无效包过滤。

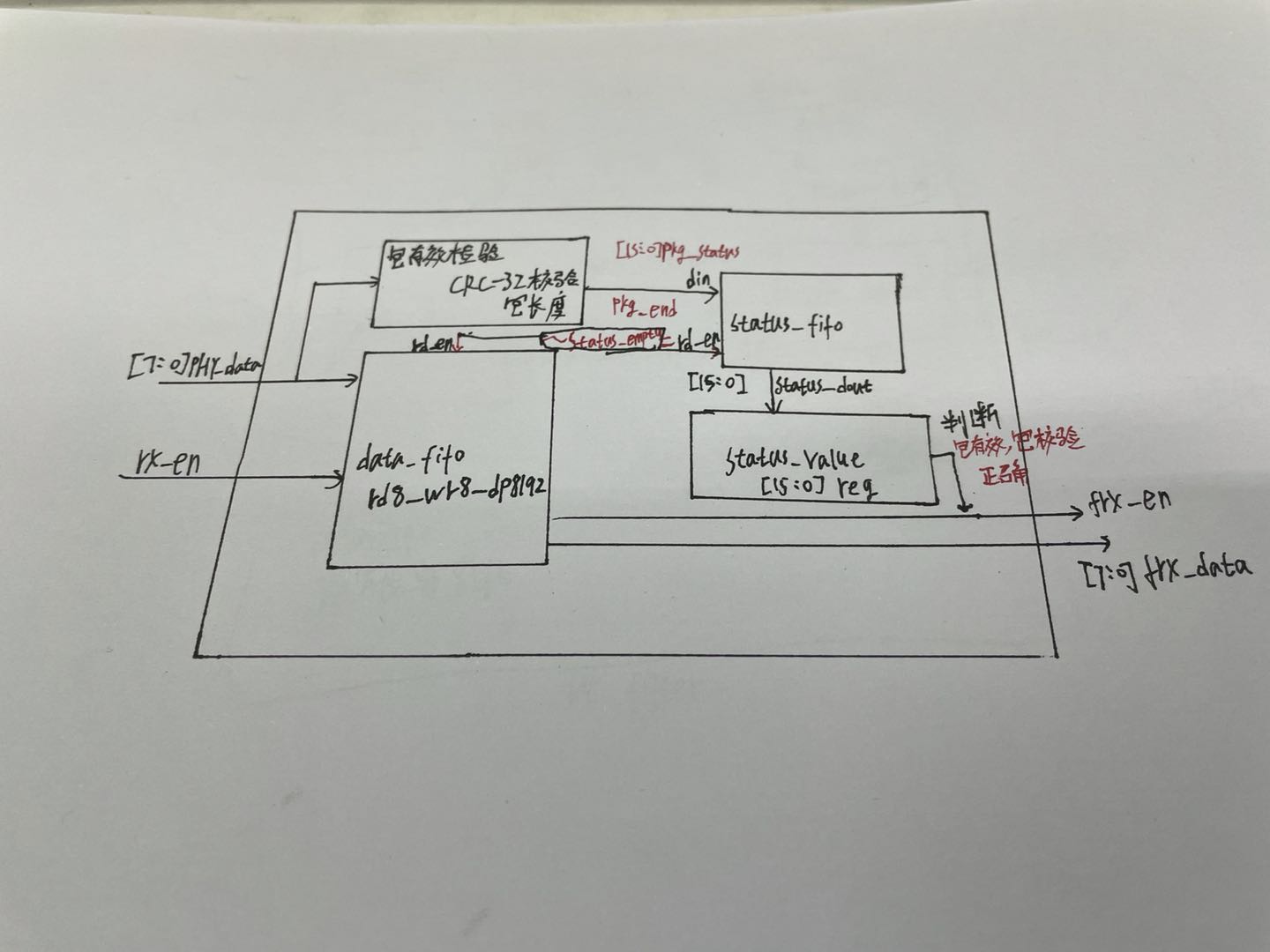

项目原理及框图

对iddr_ctrl模块的输入数据和使能信号,分成两部分处理:第一部分数据通过包有效检验,CRC32校验(单独建一个模块例化使用),包长度统计(通过rx_en和一个计数器来实现)后,把这三部分处理后的标志信号放在一个status_fifo中缓存,用一个16位位宽的status_value寄存器缓存;第二部分,将数据和使能信号缓存在一个数据FIFO中data_fifo模块中,待第一部分的status_fifo中缓存好了数据的状态信息如包有效标志,包长度,CRC32校验正确标志。通过判断status_value寄存器中的包有效标志,CRC32校验正确标志拉高,则数据校验和过滤完成,就将数据frx_data和使能信号frx_en输出。

大概的设计思路,先设计CRC32校验模块,然后再设计上面的rx_filter_buffer用来对数据进行过滤和有效包检验。

CRC32校验原理是本次设计的核心,对于CRC-32的理解:第一步,刚开始先看看CRC的原理,第二步看书上对CRC-8的两种推导,一是实际手算推导,二是移位寄存器方式实现CRC(硬件的实现方式)。第三步,则是在理解CRC-8的基础上,CRC-32与它类似,主要是理解移位寄存器方式和对应的CRC校验码。

1.CRC的原理是通过网上博客讲解,我的理解如下:

根本思想就是先在要发送的帧后面附加一个数(这个就是用来校验的校验码,但要注意,这里的数也是二进制序列的,下同),生成一个新帧发送给接收端。当然,这个附加的数不是随意的,它要使所生成的新帧能与发送端和接收端共同选定的某个特定数整除(注意,这里不是直接采用二进制除法,而是采用一种称之为“模2除法”)。到达接收端后,再把接收到的新帧除以(同样采用“模2除法”)这个选定的除数。因为在发送端发送数据帧之前就已通过附加一个数,做了“去余”处理(也就已经能整除了),所以结果应该是没有余数。如果有余数,则表明该帧在传输过程中出现了差错。

CRC校验原理就是以下几个步骤:

(1)先选择(可以随机选择,也可按标准选择,具体在后面介绍)一个用于在接收端进行校验时,对接收的帧进行除法运算的除数(是二进制比较特串,通常是以多项方式表示,所以CRC又称多项式编码方法,这个多项式也称之为“生成多项式”)。

(2)看所选定的除数二进制位数(假设为k位),然后在要发送的数据帧(假设为m位)后面加上k-1位“0”,然后以这个加了k-1个“0“的新帧(一共是m+k-1位)以“模2除法”方式除以上面这个除数,所得到的余数(也是二进制的比特串)就是该帧的CRC校验码,也称之为FCS(帧校验序列)。但要注意的是,余数的位数一定要是比除数位数只能少一位,哪怕前面位是0,甚至是全为0(附带好整除时)也都不能省略。

(3)再把这个校验码附加在原数据帧(就是m位的帧,注意不是在后面形成的m+k-1位的帧)后面,构建一个新帧发送到接收端,最后在接收端再把这个新帧以“模2除法”方式除以前面选择的除数,如果没有余数,则表明该帧在传输过程中没出错,否则出现了差错。

通过以上介绍,大家一定可以理解CRC校验的原理,并且不再认为很复杂吧。

从上面可以看出,CRC校验中有两个关键点:一是要预先确定一个发送端和接收端都用来作为除数的二进制比特串(或多项式);二是把原始帧与上面选定的除进行二进制除法运算,计算出FCS。前者可以随机选择,也可按国际上通行的标准选择,但最高位和最低位必须均为“1”,如在IBM的SDLC(同步数据链路控制)规程中使用的CRC-16(也就是这个除数一共是17位)生成多项式g(x)= x16 + x15 + x2 +1(对应二进制比特串为:11000000000000101);而在ISO HDLC(高级数据链路控制)规程、ITU的SDLC、X.25、V.34、V.41、V.42等中使用CCITT-16生成多项式g(x)=x16 + x15 + x5 +1(对应二进制比特串为:11000000000100001)。

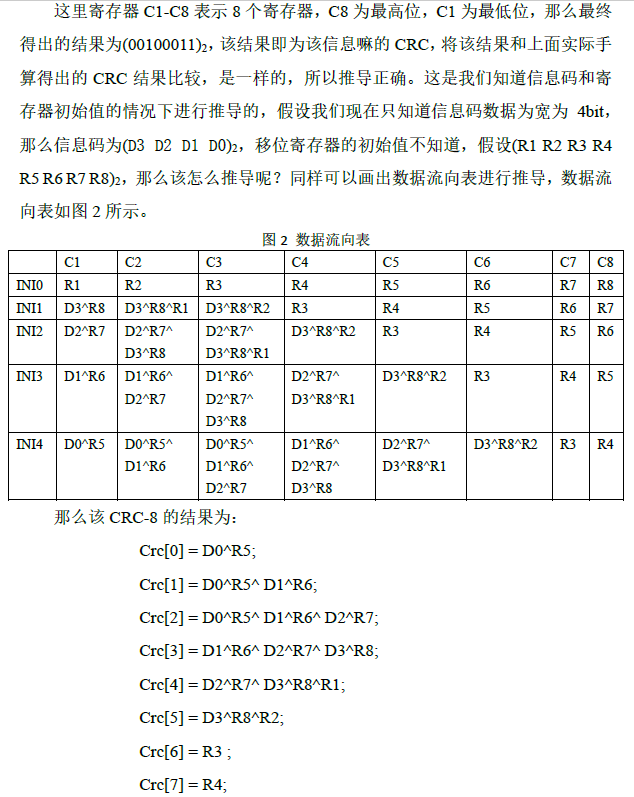

2.CRC-8的实现

对于FPGA来言,主要是通过移位寄存器实现CRC校验码。

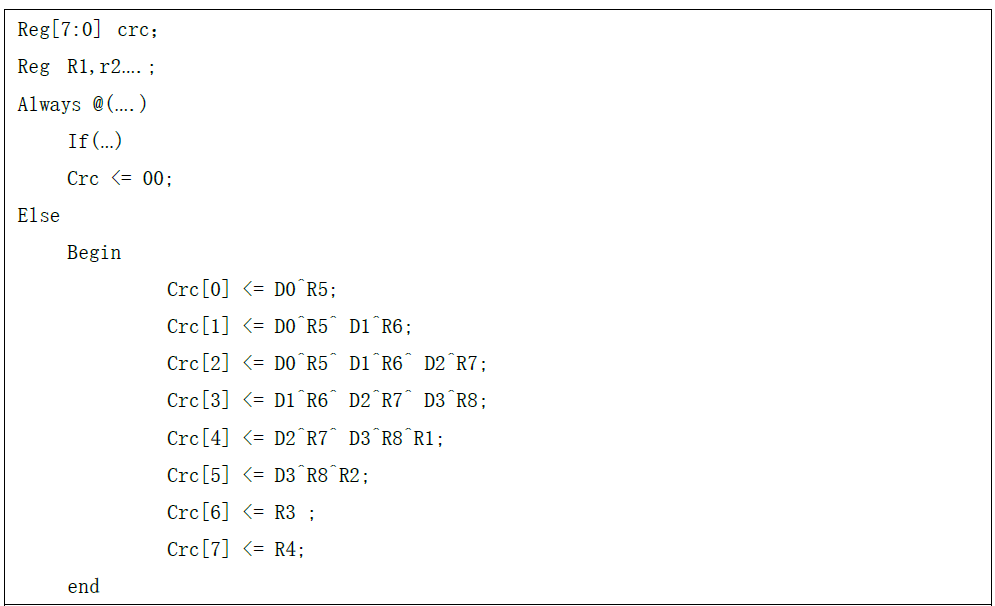

对于CRC-32的原理,我们直接给出它的校验码的化简结果,原理和CRC-8类似

对于以上原理的分析,设计的CRC-32的Verilog代码如下:主要是对校验码生成原理的理解,而校验结果直接通过查找表实现即可。

|

module crc32_d8_rec_02( ); reg dsin_r,crc32_end_r,crc_err_r; assign d = din; end assign crc32_cal_end = crc32_end_r; always@(posedge sclk)begin end end end //数据有效标志下降沿标志数据结束 //数据校验出错标志 endmodule |

第二个模块,数据的包有效检验和过滤模块的设计

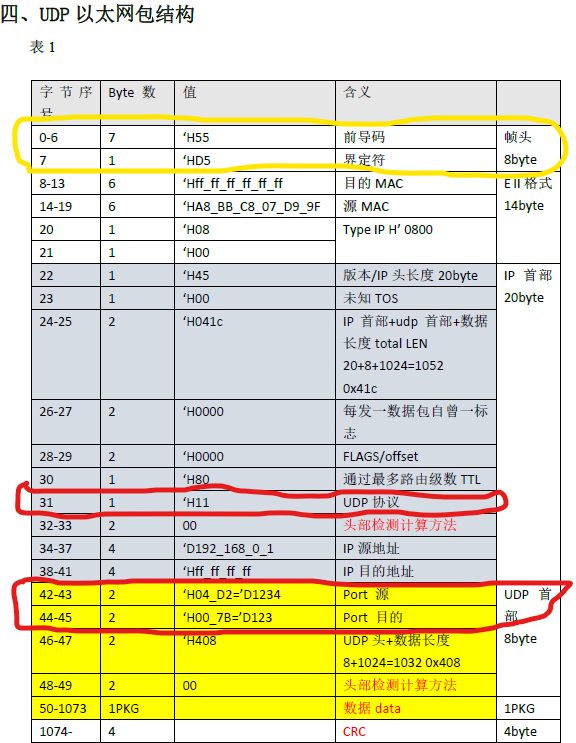

1、检测有效包,目前我们定义上位机软件设置源端口为 1 234 ,目的端口 1 23

U DP 协议字段为 8 ’h11 这样可以证明此包为来自于我们需要的应用 。 我们

在代码中需要检测这三个字段 检测到了后需要把此包的 vld_pkg 有效 这

样将来读取此包数据时会下发到下一级 。针对上图就是红色圈着的五个字节,只需要和标准值匹配则表明包有效。

关键代码如下

always @(posedge sclk) begin

if(rst) begin

pkg_value <= 40'd0;

end

else if(PHY_rx_cnt==31 || (PHY_rx_cnt>=42 && PHY_rx_cnt<=45)) begin

pkg_value <= {pkg_value[31:0],PHY_rxd};

end

end

always @(posedge sclk) begin

if(rst) begin

pkg_vld <= 1'b0;

end

else if(PHY_rx_neg && pkg_value==40'h11_04d2_007b) begin

pkg_vld <= 1'b1;

end

else begin

pkg_vld <= 1'b0;

end

end

2、C RC 是为了证明一个数据包是否出错 此 C RC 为 32 位校验码 只能用于验证

数据是否出错不能纠正错误 。 CRC 校验的区域为去掉 一帧 前 8 字节的所有数

据(去掉 7 个 0x 55 和 1 个 0xd 5

关键代码如下:rx_en_new为CRC校验模块的使能信号,是在去掉帧头后驱动这个模块

reg rx_en_new;

always @(posedge sclk or negedge rx_en) begin

if (rx_en == 1'b0) begin

rx_en_new <= 1'b0;

end

else if (PHY_rx_cnt == 'd7) begin

rx_en_new <= 1'b1;

end

end

rx_filter_buffer模块的时序图如上所示,根据时序图和原理框图可以很快设计出本模块代码如下所示:

|

module rx_filter_buffer( ); reg data_rd_en_r1; wire crc32_ok; assign crc32_ok =~crc_err ; wire pkg_end; reg [13:0] data_rd_en_cnt; reg [39:0] pkg_value; crc32_d8_rec_02 inst_crc32_d8_rec_02 //data_rd_cnt;dataFIFO读出的数据个数 else if(data_rd_en)begin always @(posedge sclk ) //data_rd_en always @(posedge sclk ) begin end // always @(posedge sclk ) begin reg phy_rx_ctrl_r; reg PHY_rx_neg; //包有效字段检验 always @(posedge sclk) begin always @(posedge sclk ) begin //status_value end //data_fifo always @(posedge sclk) begin endmodule |

由于没有A7的开发板,故本次设计了仿真文件验证:

仿真程序如下:

`timescale 1ns / 1ps

`define CLOCK 8

module tb_gigbit;

reg rst_n ;

reg gb_tx_data_en ;

reg gb_tx_clk ;

reg [ 7:0] gb_tx_data ;

wire [7:0] frx_data;

wire frx_en;

reg [7:0] mem[1073:0];

initial begin

$readmemb("./data.txt",mem);

end

// //D:\FPGA_class\3ZQ\10qianz

// initial begin

// $readmemb("D:/FPGA_class/3ZQ/10qianz/data.txt",mem);

// end

initial begin

rst_n = 1'b0;

gb_tx_clk = 1'b0;

gb_tx_data = 8'd0;

gb_tx_data_en = 1'b0;

#1000;

rst_n = 1'b1;

gen_data();

#100;

gb_tx_data_en = 1'b0;

end

always #(`CLOCK/2) gb_tx_clk = ~gb_tx_clk;

// task gen_data;

// integer i;

// integer j;

// begin

// @(posedge gb_tx_clk);

// gb_tx_data_en = 1'b1;

// for(j=0;j<1073;j=j+1)begin

// for (i=0;i<1073;i=i+1)begin

// gb_tx_data=mem[i];

// @(posedge gb_tx_clk);

// end

// end

// gb_tx_data = 8'h0;

// gb_tx_data_en = 1'b0;

// #(1000*`CLOCK);

// @(posedge gb_tx_clk);

// end

// endtask

task gen_data;

integer i;

begin

@(posedge gb_tx_clk);

gb_tx_data_en = 1'b1;

for (i=0;i<1073;i=i+1)begin

gb_tx_data=mem[i];

@(posedge gb_tx_clk);

end

@(posedge gb_tx_clk);

gb_tx_data = 8'h0;

gb_tx_data_en = 1'b0;

#(100*`CLOCK);

@(posedge gb_tx_clk);

end

endtask

rx_filter_buffer inst_rx_filter_buffer (

.sclk (gb_tx_clk),

.rst (~rst_n),

.PHY_rxd (gb_tx_data),

.rx_en (gb_tx_data_en),

.frx_en (frx_en),

.frx_data (frx_data)

);

endmodule

仿真波形如下:

这次千兆网的校验和数据包有效的测验,我领悟到,针对一个新的设计,关键是两点:第一是拆分。第二是针对同一个知识点,用多种方式去理解。

参考资料:

V3学院

CSDN博客

https://www.cnblogs.com/liushui-sky/p/9962123.html

咸鱼FPGA

https://www.cnblogs.com/xianyufpga/p/12147156.html

千兆网数据CRC检验和过滤的更多相关文章

- linux fedora 14(内核2.6.35.6) PF_RING+libpcap 极速捕获千兆网数据包,不丢包

前面讲到了libpcap 捕获数据包,尤其在千兆网的条件下,大量的丢包,网上搜索好久,大概都是PF_PACKET +MMAP,NAPI,PF_RING之类的方法,我对PF_RING+libpcap进行 ...

- FPGA千兆网UDP协议实现

接着上一篇百兆网接口的设计与使用,我们接着来进行FPGA百兆网UDP(User Datagram Protocol)协议的设计. 1)UDP简介 在此,参考博主夜雨翛然的博文“https://www. ...

- Dalsa Sherlock 直连千兆网相机(通用驱动)

支持 Sherlock 7.1.7.2,用于千兆网相机与 Sherlock 的连接. 可适用于很多厂商的相机,如:巴斯勒(Basler),JAI,堡盟相机(Baumer),灰点相机(Point Gre ...

- 010 FPGA千兆网UDP通信【转载】

一.以太网帧格式 图8‑12以太网帧格式 表8‑5以太网帧格式说明 类别 字节数 说明 前导码(Preamble) 8 连续 7 个 8'h55 加 1 个 8'hd5,表示一个帧的开始,用于双方设备 ...

- 华为S5700S-52P-LI-AC千兆网管交换机web登录界面配置

研究一下午,包装附的说明书根本就是错误的,通过技术售后和官方的文档结合,总算可以登录交换机的web管理界面. 首先需要使用通讯控制线缆(包装中附)连接电脑和交换机,一头接交换机的Console口,一头 ...

- 迅为双核imx6DL核心板_ARM定制专家_Cortex SATA 千兆网 4G GPS

核心板参数 尺寸:51mm*61mm CPU:Freescale Cortex-A9 双核精简版 i.MX6DL,主频 1.2 GHz 内存:1GB DDR3 存储:8GB EMMC 存储 EEPRO ...

- 011 FPGA千兆网TCP通信【转载】

一.LWIP 首先通过上面的简单分析,我们应该很清楚一件事:TCP协议很复杂,光握手过程就需要"三次握手.四次挥手"的复杂过程,不是特别适合FPGA的纯逻辑实现,因为用FPGA实现 ...

- 【转】简谈基于FPGA的千兆以太网

原文地址: http://blog.chinaaet.com/luhui/p/5100052903 大家好,又到了学习时间了,学习使人快乐.今天我们来简单的聊一聊以太网,以太网在FPGA学习中属于比较 ...

- FPGA设计千兆以太网MAC(2)——以太网协议及设计规划

上篇该系列博文中通过MDIO接口实现了PHY芯片的状态检测,验证其已处于1000M 全双工工作模式.在设计MAC逻辑之前,要先清楚MAC与PHY之间的接口以及以太网协议细节,这样才能保证网络的兼容性. ...

随机推荐

- CoaXPress 接口相机的控制方法--1

GenICam 介绍 简而言之,GenICam 定义了一个通用的相机接口,使得应用程序的编写.相机的控制可以与具体的型号解耦,这样就可以设计出通用的软件完成对不同相机的控制.我们实际使用的CoaXPr ...

- Solution -「SHOI2016」「洛谷 P4336」黑暗前的幻想乡

\(\mathcal{Description}\) link. 有一个 \(n\) 个结点的无向图,给定 \(n-1\) 组边集,求从每组边集选出恰一条边最终构成树的方案树.对 \(10^9+ ...

- Solution -「洛谷 P6158」封锁

\(\mathcal{Description}\) Link. 给定一个 \(n\times n\) 的格点图,横纵相邻的两格点有一条边权为二元组 \((w,e)\) 的边.求对于 \(S=( ...

- 公式编辑器CVE-2018-0798样本分析

当前样本是一个RTF文档,内嵌一个公式编辑器对象,该对象利用Office编辑器漏洞CVE-2018-0798执行shellcode,对EQNEDT32.exe进行代码注入,执行恶意代码. 使用 ...

- suse 12 二进制部署 Kubernetets 1.19.7 - 第12章 - 部署dashboard插件

文章目录 1.12.0.创建namespace 1.12.1.创建Dashboard rbac文件 1.12.2.创建dashboard文件 1.12.3.查看pod以及svc 1.12.4.获取 d ...

- Python小游戏之 - 飞机大战 !

用Python写的"飞机大战"小游戏 源代码如下: # coding=utf-8 import random import os import pygame # 用一个常量来存储屏 ...

- 解决UIWebView内存不释放问题

走访很多朋友,查阅了很多资料发现UIWebView这尼玛就是个坑,有人说是sdk自带的bug....... 所以一个新的方法诞生了#import <WebKit/WebKit.h> WKW ...

- logstash获取nginx日志的配置

nginx部分配置直接用json,省去很多麻烦 log_format json '{"@timestamp":"$time_iso8601",' '" ...

- kali linux安装nessus

详细介绍在 Kali 中安装 Nessus 的详细过程步骤以及插件下载失败解决方法. 实验环境 安装过程 下载 Nessus 安装 Nessus 启动 Nessus 获取激活码 登陆 web 界面 N ...

- 太骚了,用Excel玩机器学习

最近发现了一个好玩的Python库,它可以将训练好的机器学习模型转换为Java.C.JavaScript.Go.Ruby,VBA 本地代码,可以让连Python和机器学习一无所知的同学也能感受预测的神 ...