HDLbits——Shift18

// Build a 64-bit arithmetic shift register,

// with synchronous load. The shifter can shift both left and right,

// and by 1 or 8 bit positions, selected by amount.

// An arithmetic(算数) right shift shifts in the sign bit of the number in the shift register (q[63] in this case) instead of zero as done by a logical right shift. Another way of thinking about an arithmetic right shift is that it assumes the number being shifted is signed and preserves the sign, so that arithmetic right shift divides a signed number by a power of two.

// There is no difference between logical and arithmetic left shifts.

// load: Loads shift register with data[63:0] instead of shifting.

// ena: Chooses whether to shift.

// amount: Chooses which direction and how much to shift.

// 2'b00: shift left by 1 bit.

// 2'b01: shift left by 8 bits.

// 2'b10: shift right by 1 bit.

// 2'b11: shift right by 8 bits.

// q: The contents of the shifter.

**注意**:算数右移和逻辑右移的区别

>>逻辑右移不考虑符号位,空缺的位置补领操作即可

>>算数右移动需要考虑符号位,右移一位,如果符号位为1,则在符号位补1,如果符号位为0,则在符号位补0.即算数右移后,空缺的位置补符号位的数字即可

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk)begin

if(load)begin

q <= data;

end

else if(ena) begin

case(amount)

2'b00: q <= {q[62:0],1'b0};

2'b01: q <= {q[55:0], 8'b0};

2'b10: q <= {q[63],q[63:1]};//有符号数右移动 如果符号位为1,则右移后是补1;如果符号位为0,则右移后是补0

2'b11: q <= { { 8{q[63]} },q[63:8]};

endcase

end

else q <= q;

end

endmodule

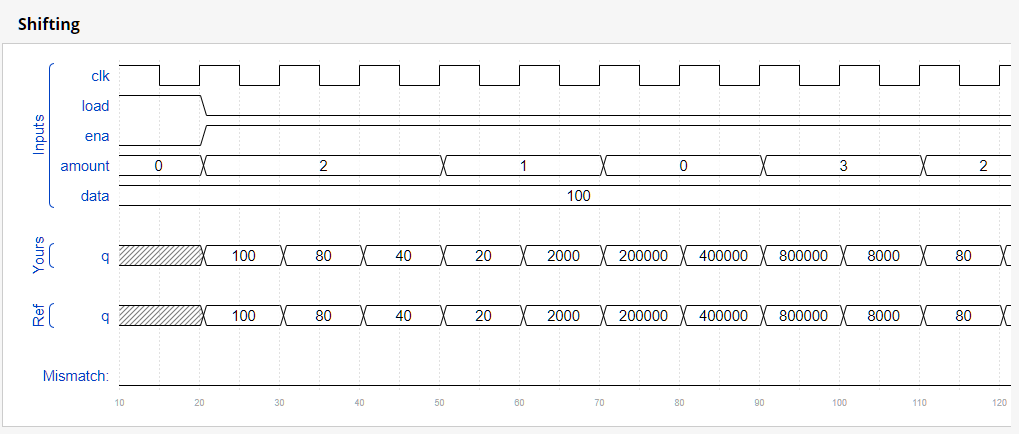

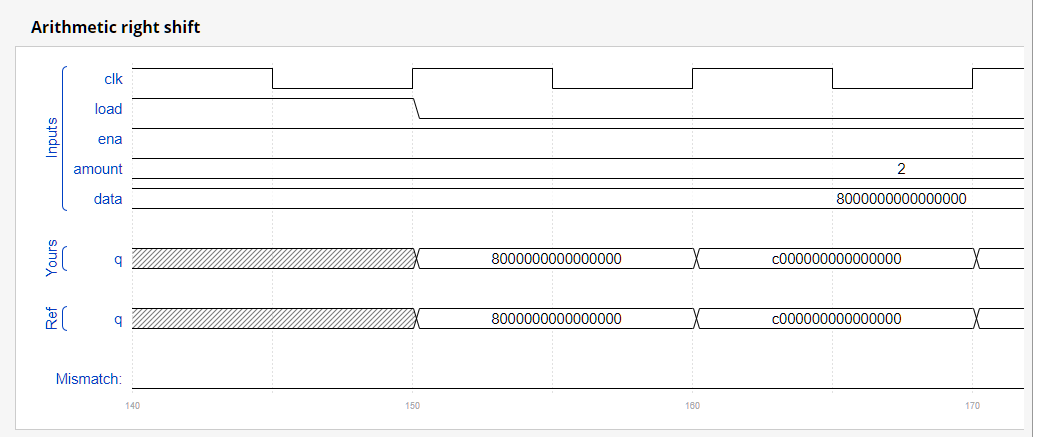

仿真图:

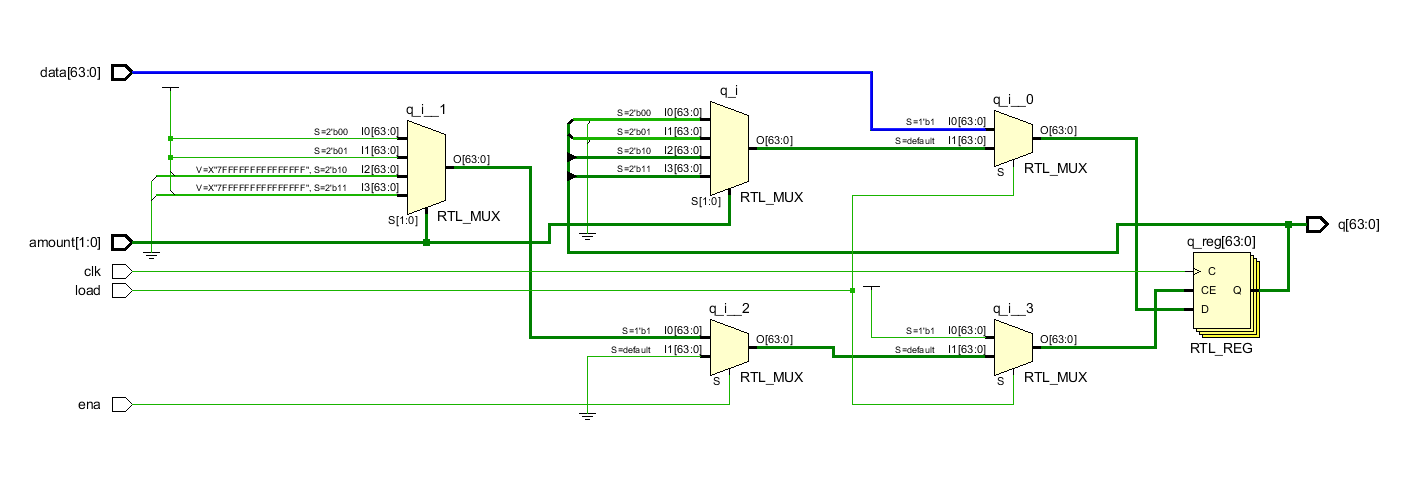

原理图:

HDLbits——Shift18的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- SSM项目集成Redis

1. 加入依赖 <!--redis--> <dependency> <groupId>redis.clients</groupId> <artif ...

- web上传插件Uploadify

Uploadify简单说来,是基于Jquery的一款文件上传插件.它的功能特色总结如下: 支持单文件或多文件上传,可控制并发上传的文件数 在服务器端支持各种语言与之配合使用,诸如PHP,.NET,Ja ...

- Windows10使用VMware安装centos

系统环境: Windows 10 安装步骤: 1.下载centos http://mirrors.aliyun.com/centos/ 2.使用VMware安装centos 3.配置网络 $ cd / ...

- oracle 2个数组列,剔除数组重复的数据。

一.下面这样不规则的,数据如何剔除掉.循环筛选replace替换掉. 序号 正常时间 剔除时间 1 2022-12-19,2022-12-20,2022-12-21,2022-12-22,202 ...

- SAP BW/4HANA学习笔记2

2.Data Modeling BW/4HANA Data Modeling简介 Data Quality:数据质量问题: silos(桶仓):大量重复冗余的主数据,独立计算统计: 数据silos缺点 ...

- .net core解决时间格式转换问题或日期取当前时间

一.时间格式转换 1.新建一个格式化类DatetimeJsonConverter,继承自JsonConverter,然后重写里面的方法 public class DatetimeJsonConvert ...

- SSL certificate problem: unable to get local issuer certificate 错误解决

终端报了如下错误git SSL certificate problem: unable to get local issuer certificate 这个问题是由于没有配置信任的服务器HTTPS验证 ...

- Windows2016安装.NetFramework 3.5

Windows2016安装.NetFramework 3.5 Windows2016服务器默认安装的是 .Net 4.6.2版本,但是有时候我们经常会需要用到.Net 3.5版本.以下介绍的是在线和离 ...

- arm架构安装mysql5.7

添加mysql用户组和mysql用户,用于隔离mysql进程 groupadd -r mysql && useradd -r -g mysql -s /sbin/nologin -M ...

- PY0271验证码的创建

生成的 随机背景色的 效果 from PIL import Image,ImageDraw,ImageFont,ImageFilterimport random# 设置随机的背景颜色.def rndC ...