ADC for programmable logic uses one capacitor

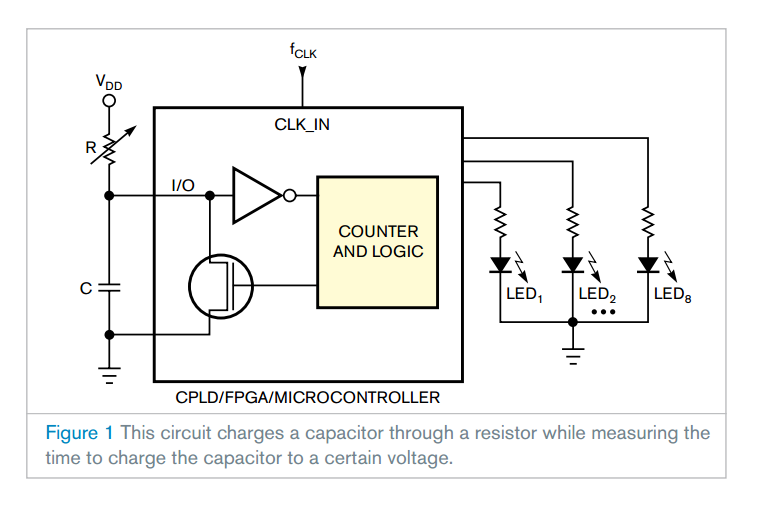

Many electronic devices require user input for setting the application properties. Typical input devices include pushbuttons, potentiometers, and touchscreens. To minimize overall project cost, you may have to select low-range microcontrollers, FPGAs (field-programmable gate arrays), or PLDs (programmable-logic devices). These devices don’t provide a wide range of peripherals and often lack analog-to-digital-conversion capability, which can prove annoying when trying to acquire user input. This Design Idea describes a method for adding a low-end ADC to a single programmable-logic I/O pin. The circuit charges a capacitor through a resistor while measuring the time to charge the capacitor to a certain voltage.

Before each measurement, the capacitor discharges to 0V. A single I/O pin can perform both the discharging and the timing. For an FPGA or a PLD, you can perform a discharge by setting the I/O as an output pin and forcing a zero at that pin. You can charge the capacitor by setting the I/O as an input pin, which gives it a high impedance. The capacitor charges through the potentiometer (Figure 1).

Meanwhile, a counter starts, and the CPLD monitors the input voltage. As soon as the capacitor voltage reaches the threshold, the counter stops at a value that is a measure of the charging time. The charging time or counter value relates to the clock frequency, the value of the resistor, the value of the capacitor, and the input threshold voltage:

If you assume that the capacitor value, the input threshold voltage, and the clock frequency remain fairly constant over the operating range, the charging time is linearly dependent on the value of the resistor. If you replace the resistor with a potentiometer, a counter value depends on the potentiometer position. The application uses a Xilinx XC9500 XL CPLD (Figure 2).

The I/O, which VHDL (very-high-speed-IC hardware-description language) declares as a tristate buffer, first shorts the capacitor. Hardware limits the output short-circuit current of the I/O pins to ±10 mA, so the capacitor’s shorting should last long enough to guarantee a full discharge. You can calculate the minimum shorting time using the capacitor value, short-circuit current, and discharge voltage, assuming that the threshold voltage must discharge from the capacitor:

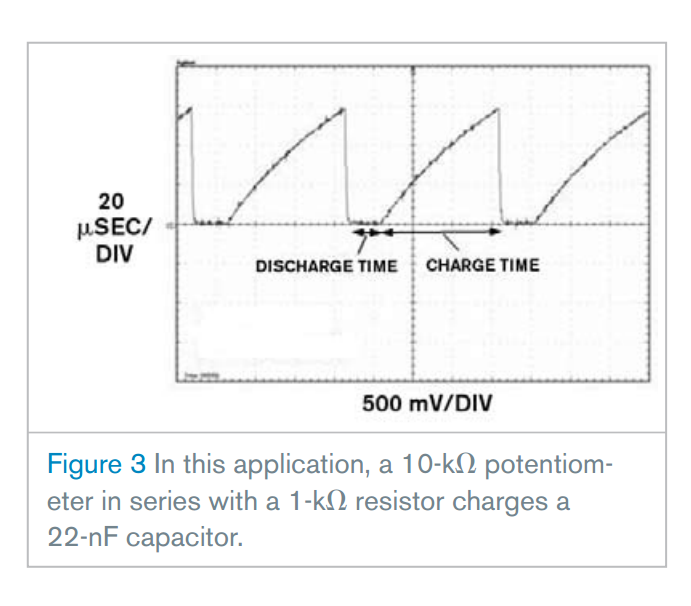

The discharge delay can be realized with a small counter. After the discharge time, the I/O pin acts as an input, which causes the capacitor to charge through a pullup potentiometer. Meanwhile, the internal counter starts. When the capacitor voltage reaches the input threshold voltage, the counter stops. Eight LEDs show the 8-bit value. In this application, a 10-kΩ potentiometer in series with a 1-kΩ resistor charges a 22-nF capacitor. The input clock of the PLD is 1.8432 MHz. The input threshold is 1.5V at a supply of 3.3V. This arrangement allows a measurement range between a counter value of 25 and 270, equivalent to a resolution of almost 8 bits.

Figure 3 shows the capacitor charging/discharging waveform.

Every IC’s I/O pin has a certain bias sink or source current, causing a voltage drop over the charging resistor. This situation limits the charge voltage to VDD–RCHARGE×IBIAS. In other words, if the charging resistance is too large, the capacitor doesn’t charge above the input-pin threshold voltage, stopping the circuit’s operation. Similar applications for microcontrollers or PLDs (references 1 through 5) include adding multiple inputs to a single I/O pin and using a different pullup-resistor value for each input. By discriminating the charging times for each resistor, the PLD can decide which resistor or combination of resistors the user has actuated.

Another application for microcontrollers is temperature measurement. By replacing the pullup resistor with a PTC (positive-temperature-coefficient) or an NTC (negative-temperature-coefficient) resistor, you can derive the temperature from the charging time after calibration. You can also use these devices to make true analog-to-digital measurements. By replacing the pullup resistor with a voltage-controlled current source, an input-voltage change causes a linear change in the charging time, providing a real analog-to-digital conversion.

| References |

|

ADC for programmable logic uses one capacitor的更多相关文章

- FPGA LVDS I/O as an Analog Programmable Comparator

http://www.eetimes.com/author.asp?section_id=36&doc_id=1320289 Seeing the new ADC IP being bandi ...

- DAC Essentials

http://e2e.ti.com/blogs_/b/analogwire/archive/tags/DAC%2bEssentials DAC Essentials: A new blog serie ...

- JTAG 引脚自动识别 JTAG Finder, JTAG Pinout Tool, JTAG Pin Finder, JTAG pinout detector, JTAGULATOR, Easy-JTAG, JTAG Enumeration

JTAG Finder Figuring out the JTAG Pinouts on a Device is usually the most time-consuming and frustra ...

- 中国计算机学会CCF推荐国际学术会议

中国计算机学会推荐国际学术会议 (计算机系统与高性能计算) 一.A类 序号 会议简称 会议全称 出版社 网址 1 ASPLOS Architectural Support for Programmin ...

- 关于CPLD与FPGA的对比分析

1.PLD/FPGA/CPLD PLD(Programmable Logic Device):可编程逻辑器件,数字集成电路半成品,芯片上按照一定的排列方式集成了大量的门和触发器等基本逻辑元件,使用者按 ...

- OrCAD Capture使用记录

1.安装 ①修改host_ID为主机名称(如果填不对,安装过程会提示你再填一次):其后跟的是机子的MAC地址,用ipconfig /all 可以查看. ②下一行的FLEMlm,后面跟的是文件cdslm ...

- 浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真

浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真 工作内容: Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业 ...

- CCF推荐国际学术会议

类别如下计算机系统与高性能计算,计算机网络,网络与信息安全,软件工程,系统软件与程序设计语言,数据库.数据挖掘与内容检索,计算机科学理论,计算机图形学与多媒体,人工智能与模式识别,人机交互与普适计算, ...

- 10 notorious computer virus

The history of computer virus is the same as computer history. With more and more powerful computers ...

随机推荐

- openjudge-NOI 2.6-1775 采药

题目链接:http://noi.openjudge.cn/ch0206/1775/ 题解: 很经典的01背包问题,设时间为t,价值为v 一维压缩,状态转移方程fj=max(fj,fj-ti+vi) # ...

- 教你如何修改FireFox打开新标签页(NewTab Page)的行列数

FireFox的打开新建标签页(即NewTab Page)默认只能显示3x3个网站缩略图,这9个自定义的网站,非常方便快捷,什么hao123的弱爆了,本人从未用过此类导航网站,曾经用过的也只是abou ...

- POJ 2349 Arctic Network(最小生成树+求第k大边)

题目链接:http://poj.org/problem?id=2349 题目大意:有n个前哨,和s个卫星通讯装置,任何两个装了卫星通讯装置的前哨都可以通过卫星进行通信,而不管他们的位置. 否则,只有两 ...

- hdu 1849(巴什博弈)

Rabbit and Grass Time Limit: 1000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) ...

- csu 1769(数学)

1769: 想打架吗?算我一个!所有人,都过来!(3) Time Limit: 2 Sec Memory Limit: 128 MBSubmit: 262 Solved: 76[Submit][S ...

- CSU 1412 Line and Circles

原题链接:http://acm.csu.edu.cn/OnlineJudge/problem.php?id=1412 题目要求判断是否有一条直线可以穿过所有的圆. 做法:把所有圆心做一次凸包,然后判断 ...

- appium---【Mac】Appium-Doctor提示WARN:“ ios_webkit_debug_proxy cannot be found”解决方案

“ ios_webkit_debug_proxy cannot be found”报错截图如下: 解决方案: 打开terminal终端,分别输入执行结束,再次运行appium-doctor即可看到运行 ...

- CentOS7.6打开的程序窗口居中

每次在CentOS7中打开新的窗口都会靠左上角显示,所以每次打开一个窗口都要多做一步操作,将窗口移到屏幕中间来,强迫症的我觉得太麻烦了,所以… 安装ccsm yum -y install compi ...

- grep 同时排除多个关键字

不说废话, 例如需要排除 abc.txt 中的 mmm nnn grep -v 'mmm\|nnn' abc.txt 再举个例子,需要确定mac 的本机ip地址, 显然直接可以输入 ifcon ...

- linux中使用rm命令将文件移到回收站的方法

今天在终端下,看到我的用户目录下有个-的文件夹(maven生成),相要删除收回点空间,习惯性的用命令 rm -rf ~ ,一回车,猛然想起的时候已经来不及了,世界一下子清静了,想死的心都有了! 没错, ...