FPGA小白学习之路(6)串口波特率问题的处理

串口波特率问题的处理

此博文一共包含三个方面的内容:(1)异步串口通信的数据格式;(2)为何串口通信中接收端采样时钟频率是传输的波特率的16倍;(3)串口波特率等概念。

1、异步串口通信的数据格式

串口的通信可以通过链接了解:https://wenku.baidu.com/view/7b459e47453610661ed9f4d4.html###

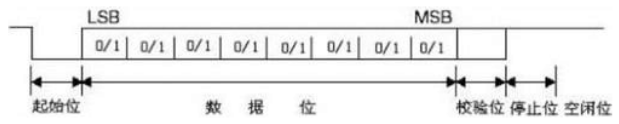

异步串口通信的数据格式如图1所示:

图1 异步串口通信的数据格式

由于在空闲状态时,传送线为逻辑“1”状态,而数据的传送总是以一个起始位“0”开始,所以当接收器检测到一个从“1”向“0”的跳变时,便视为可能的起始位(要排除干扰引起的跳变);起始位被确认后,就知道发送器已开始发送,接收器就可以按这个数据通信格式接收后续的数据了;当检测到停止位“1”后就表明一帧字符数据已发送完毕。

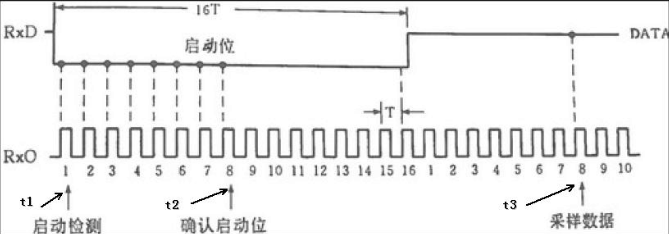

关于接收器的设计最主要的一点是如何提高采样的准确率,最好是保证采样点处于被采样数据的时间中间点。所以,在接收采样时要用比数据波特率高n倍(n≥1)速率的时钟对数据进行采样。在本程序中用16倍波特率时钟进行采样。结合图2所示,我们讲解一下如何让采样时刻处于被采样数据的时间中间点:

图2 串口数据采样

在t1时刻若检测到低电平,就开始对这个低电平进行连续的检测;

当检测了8个时钟周期后,到达t2,此刻,若前面的8个周期都是低电平,则认为检测到了起始脉冲。否则就认为是干扰,重新检测。

在检测到起始位后,再计数16个采样时钟周期就到达了第一个数据位的时间中间点t3,在此刻采样数据并进行保存。

然后再经过16个周期,就是第二个数据位的时间中间点,在此时刻进行采样;然后,再经过16个周期,就是第三个数据位的时间中间点, 在此时刻进行采样…..一直这样采样,直到把所有的数据位采样完毕。

2、为何串口通信中接收端采样时钟频率是传输的波特率的16倍

增强抗干扰是原因之一

标准UART可以选16倍采样,也可以选64倍采样,个人觉得应该是方便分频设计.

标准UART的RXD前端有一个"1到0跳变检测器",当其连续接受到8个RXD上的低电平时,该检测器就认为RXD线出现了起始位,进入接受数据状态。在接收状态,接收控制器对数据位7,8,9三个脉冲采样,并遵从三中取二的原则确定最终值。采用这一方法的根本目的还是为了增强抗干扰,提高数据传送的可靠性,采样信号总是在每个接受位的中间位置,可以避开数据位两端的边沿失真,也可以防止接受时钟频率和发送时钟频率不完全同步引起的误差。

3、串口波特率等概念

1:比特率:9600bps

就是每秒中传输9600bit,也就是相当于每一秒中划分成了9600等份。

如此,那么每1bit的时间就是1/9600秒=104.16666666666666666666666666667us。约0.1ms。既然是9600等份,即每1bit紧接着下一个比特,不存在额外的间隔。也不管是啥起始bit,数据bit,奇偶bit,停止bit。

2:帧格式,帧间隔。

在电脑里,也就是超级终端等的端口设置。电脑的默认端口设置,也就是默认帧格式是:8个数据bit,1个停止bit,(起始1bit 是必须的)默认无奇偶,无流控。

则实际就是10bit为1帧。一秒中可以发送9600/10=960个帧,也就是960字符,因为一帧里只有1个字符,1字符就是帧里面的8个数据bit

3:串口通讯

串口当然可以连续,没有时间间隔地发送帧,默认情形下电脑在9600bps下可以发送960帧。

但在实际工作中,在异步通讯下,一般需要一个交互过程,所以,电脑发送一个帧,或者若干帧,还需要等待从设备的应答,并不是一直发送的。有问有答地实现编程者的目标。

4:波特率时钟

实际上是比特率时钟,每1bit所要花费的时间周期。而波特率(实际是比特率)发生器生成的分频时钟实际是对每1bit进行采样的时钟,它是波特率时钟的16倍。

波特率发生器实质是设计一个分频器,用于产生和RS 232通信同步的时钟。在系统中用一个计数器来完成这个功能,分频系数N决定了波特率的数值。该计数器一般工作在一个频率较高的系统时钟下,当计数到 N/2时将输出置为高电平,再计数到N/2的数值后将输出置为低电平,如此反复即可得到占空比50%的波特率时钟,具体的波特率依赖于所使用的系统时钟频率和N的大小。如系统时钟频率是40 MHz,要求波特率是9 600bps,则16倍波特率时钟的周期约等于260个系统时钟周期,则计数器取260/2=130时,当计数溢出时输出电平取反就可以得到16倍约定波特率的时钟。

也可以这么理解:40mhz晶振,最小计数脉冲是25ns, 16倍波特率的频率就是16*9600,其时钟周期就是1/(16*9600)=6.5us 也就是以40mhz晶振作为输入的话,计数器需要计数=6500/25=260 个计数。

9600波特率也可理解为一种波特时钟频率,即1秒钟计数9600个,如果是16倍波特率时钟,即直接相乘就可以了。就是1秒计数9600*16=153600 。

1/(9600*16) 除以(1/40000000)也就是以时钟周期除了最小时钟周期得到的就是计数的个数。简化而言就是 40000000/(9600*16)=260,也就是频率直接相除就得到要分频计数器计数的个数。

串口通信必须要设定波特率,本设计采用的波特率为9 600 bit/s。产生波特率的时钟频率是越高越好,这样才可产生较高且精确的波特率。设计选用50M主频率要产生9600bit/s波特率,每传送一位数据需要5208.33个时钟周期。取一个最接近的数是5208,则波特率为9600.61,其误差约为0.006%,误码率很低可以确保通信正常。

5:分频系数

计数器很容易实现分频。可用lpm-counter实现。

比如分频系数是2,那么,直接用q0作为输出即可。如果分频系数是4,那么q0,q1作为有效比特。

总而言之,要n整数分频,即计数n后清零重计数。至于50%占空比则另外考虑。奇数分频似不易实现50%占空比。

FPGA小白学习之路(6)串口波特率问题的处理的更多相关文章

- FPGA小白学习之路(5)clk为什么要用posedge,而不用negedge(转)

clk为什么要用posedge,而不用negedge 转自:http://www.cnblogs.com/dangxia/archive/2012/03/07/2383744.html Verilog ...

- FPGA小白学习之路(2)error:buffers of the same direction cannot be placed in series

锁相环PLL默认输入前端有个IBUFG单元,在输出端有个BUFG单元,而两个BUFG(IBUFG)不能相连,所以会报这样的错: ERROR:NgdBuild:770 - IBUFG 'u_pll0/c ...

- FPGA小白学习之路(4)PLL中的locked信号解析(转)

ALTPLL中的areset,locked的使用 转自:http://www.360doc.com/content/13/0509/20/9072830_284220258.shtml 今天对PLL中 ...

- FPGA小白学习之路(1) System Verilog的概念以及与verilog的对比(转)

转自CSDN:http://blog.csdn.net/gtatcs/article/details/8970489 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证 ...

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

- USB小白学习之路(7) FPGA Communication with PC by CY7C68013,TD_init()解析

注:这个TD_Init()只对EP6进行了配置,将其配置成为Bluk_In端口,而没有对EP2进行配置.这篇文章直接把寄存器的图片贴上来了,看起来比较杂.感兴趣的可以看下一篇文章,是转自CSDN,对E ...

- zigbee学习之路(十):串口(接收)

一.前言 上次我们学习了串口的发送,今天我们要学习串口的接收,要实现的功能是接收电脑发来的数据,控制LED 灯闪烁,而且将收到的数据发回给电脑显示出来.而且要采用不占用cpu资源的中断. 二原理与分析 ...

- zigbee学习之路(九):串口(发送)

一.前言 今天,我们来学习和实验串口模块方面的,串口通信是我们常用的通信手段,通过串口交互,我们可以很容易的和pc机进行数据的交换和发送,所以我们今天就来学习一下.这个实验所进行的功能是一开始CC25 ...

随机推荐

- 【转】Linux服务器命令行模式安装Matlab2014a

转自http://www.aichengxu.com/diannao/39100.htm 0.下载安装包 下载Matlab2014a for Linux安装包的ISO镜像文件 将下载好的iso文件挂 ...

- Docker相关学习地址

菜鸟教程:http://www.runoob.com/docker/docker-image-usage.html 官方文档:https://docs.docker.com/

- 树分治(挑战p360)

poj1741 题:http://poj.org/problem?id=1741 #include<iostream> #include<algorithm> #include ...

- ef codefirst VS里修改数据表结构后更新到数据库

2.根据已建立table的数据库建立ADO.NET数据模型在修改表后进入 工具->nuget包管理器->程序包管理器控制台 输入 enable-migrations 后vs会添加一个 ...

- 年度Java技术盘点,懂这些技术的程序员2019发展大好

与一年前一样,Java仍然是最流行的编程语言.据TIOBE的数据显示,几十年来,Java比其他语言更常名列榜首,Java因为它拥有可移植性.可扩展性和庞大的用户社区,所以许多知名互联网公司使用Java ...

- 吴裕雄--天生自然 PHP开发学习:在CenterOS 7 系统安装配置PHP 7

执行命令"yum install httpd"进行安装,然后在选择处,我们输入y,等待软件安装完毕.安装完成后,Apache配置文件路径是:/etc/httpd/conf/http ...

- [Python] 使用Python 3 下载麦子学院视频

本文基于Python 3,下载麦子学院的视频课程. 本项目只是针对某个具体课程的链接,去寻找该课程所有课时的视频链接并进行下载. 整个项目是非常简单的. 主要涉及的Python: 网络相关:reque ...

- Java IO: 序列化与ObjectInputStream、ObjectOutputStream

作者:Jakob Jenkov 译者: 李璟(jlee381344197@gmail.com) 本小节会简要概括Java IO中的序列化以及涉及到的流,主要包括ObjectInputStream和O ...

- Linux安装完后的调优(linux 6)

1:关闭 SELinux 方法一: #sed -i 's/SELINUX=enforcing/SELINUX=disabled/' /etc/selinux/config #替换文本参数 ...

- 吴裕雄--天生自然python学习笔记:网页解析

抓取万水书苑网页中所有<a>标签中的超链接井显示. import requests from bs4 import BeautifulSoup url = 'http://www.wsbo ...