ARM Cortex M3系列GPIO口介绍(工作方式探讨)

一、Cortex M3的GPIO口特性

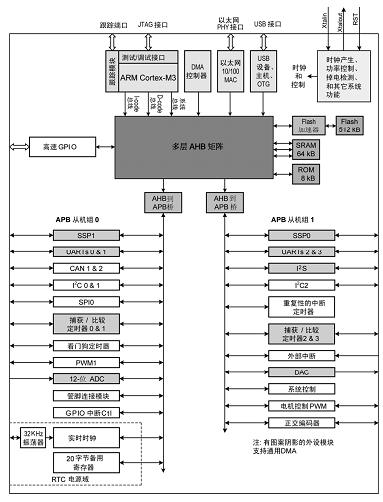

在介绍GPIO口功能前,有必要先说明一下M3的结构框图,这样能够更好理解总线结构和GPIO所处的位置。

M3数字I/O功能:

高速GPIO口,其寄存器被移到外设AHB总线,可以字节,半字和字寻址。

位电平置位和清零寄存器允许单指令置位和清零一个端口的任意位。

所有GPIO口寄存器支持M3位带操作。

整个端口值可以用一条指令写入。

GPIO口寄存器可由GPDMA控制器进行访问,可以进行DMA数据操作,使之与DMA请求同步。

单个I/O口方向可以控制。

所有I/O口在复位后默认作为上拉输入。(Why?因为微控制器连接了很多设备,如果复位后作为输出,则由于控制器电平状态不定,可能会导致外围设备产生动作,从而产生不利影响,故复位后一半都作为输入状态。)

M3可产生中断的数字端口:

PORT0 和 PORT2 端口的每个引脚都可以提供中断功能;

每个端口上的中断可被编程为上升沿、下降沿或边沿产生中断;

边沿检测是异步的,因此可以在没有时钟的情况下(例如掉电模式)操作。使用这种特性,就无需电平触发中断;

可掉电唤醒;

寄存器为软件提供挂起的上升沿中断、挂起的下降沿中断和整个挂起的 GPIO中断;

GPIO0 和 GPIO2 中断与外部中断 3 事件共用相同的 NVIC 通道。

二、GPIO口的寄存器描述

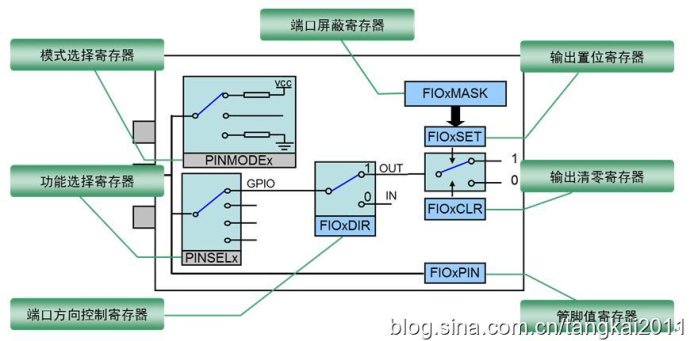

Cortex M3引脚的寄存器描述:

PINMODEx表示引脚模式选择寄存器,在使用前要配置好。

|

PINMODEx

|

功能

|

复位后的值

|

|

00

|

引脚使能上拉电阻

|

00

|

|

01

|

中继模式

|

|

|

10

|

引脚无片内上拉或下拉电阻

|

|

|

11

|

引脚使能下拉电阻

|

中继模式说明:当引脚处于逻辑高电平,中继模式能使能上拉电阻;当引脚处于逻辑低电平时,中继模式会使能下拉电阻,这样当引脚配置为输入且没有外部驱动时,能够保持上一个已知状态。

PINSELx:功能选择寄存器。用来设定PORT引脚的功能,当PINSELx各位为0时,才用作GPIO端口。

FIOxDIR:GPIO口方向寄存器,单独控制每个端口管脚的方向,可作为字节(8位),半字(16位)和字长(32位)的数据进行访问。

FIOxMASK:屏蔽寄存器。任何写、读的操作只在该寄存器对应位为“0“时才有效。

FIOxPIN:管脚值寄存器。只要管脚不配置为ADC,其他所有方式都可以从该位读出端口当前的实际状态。注:如果读FIOPIN寄存器,那么不管物理引脚的状态如何,在 FIOMASK寄存器中被“1”屏蔽的位将始终读出0。

FIOxSET:输出引脚的状态。写 1 使相应的端口引脚产生高电平。写 0 没有影响。读该寄存器,返回端口输出寄存器的当前内容。只可以更改 FIOMASK 中为 0 的位,即非屏蔽位。

FIOxCLR:控制输出引脚的状态。写 1 使相应的端口引脚产生低电平。写 0 没有影响。只可以更改 FIOMASK 中为 0 的位,即非屏蔽位。

2.1 GPIO端口方向寄存器FIOxDIR(FIO0DIR??FIO4DIR- 0x2009 C000??0x2009 C080)

当引脚被配置为 GPIO功能时,该寄存器可用来控制引脚的方向。务必根据引脚功能来设置每个引脚的方向。

注:GPIO引脚 P0.29和P0.30 与USB D+/-引脚共用,并且具有相同的方向。如果FP0DIR位29或位30在FIO0DIR寄存器中被配置为零,则P0.29 和P0.30都为输入。如果FP0DIR位29和位30被配置为1,则P0.29和P0.30都为输出。

|

位

|

符号

|

值

|

描述

|

复位值

|

|

31:0(字长数据)

|

FP0DIR

FP1DIR

FP2DIR

FP3DIR

FP4DIR

|

0

1

|

控制的引脚为输入引脚

控制的引脚为输出引脚

|

0

|

字和半字的操作基本类似,只是可以通过8位寄存器或者16位的寄存器分别控制方向而已,这里不再解释,请参看《深入浅出Cortex-M3 LPC1700》.

2.2 GPIO端口输出设置寄存器FIOxSET(FIO0SET??FIO7SET - 0x2009 C018??0x2009 C098)

当引脚在输出模式中被配置为 GPIO 时,该寄存器在端口引脚产生高电平输出。向该寄存器的某些位写入“1”时,对应的引脚产生高电平。写入“0”无效。如果需要引脚输出低电平或第二种功能,那么写 1 到 FIOxSET 的相应位无效。 读FIOxSET 寄存器返回该寄存器的值,该值由前一次对 FIOxSET 和 FIOxCLR(或前面提到的 FIOxPIN)的写操作确定,它不反映任何外部环境对 I/O引脚的影响。 通过 FIOxSET 寄存器访问的端口引脚受到 FIOxMASK 寄存器相应位的限制。

|

位

|

符号

|

值

|

描述

|

复位值

|

|

31:0(字长数据)

|

FP0SET

FP1SET

FP2SET

FP3SET

FP4SET

|

0

1

|

控制的引脚输出不改变

控制的引脚输出被设为高电平

|

0

|

2.3 GPIO端口输出清零寄存器FIOxCLR(FIO0CLR??FIO07CLR - 0x2009 C01C??0x2009 C09C)

当引脚在输出模式中被配置为 GPIO 时,该寄存器在端口引脚产生低电平输出。向某些位写入“1”会使相应的引脚产生低电平,同时清零 FIOxSET 寄存器的相应位。写入“0”无效。如果引脚被配置为输入或其它功能,那么写 FIOxCLR 对引脚没有影响。 通过FIOxCLR寄存器访问的端口引脚受到FIOxMASK寄存器相应位的限制.

|

位

|

符号

|

值

|

描述

|

复位值

|

|

31:0(字长数据)

|

FP0CLR

FP1CLR

FP2CLR

FP3CLR

FP4CLR

|

0

1

|

控制的引脚输出不改变

控制的引脚输出被设为低电平

|

0

|

2.4 GPIO端口引脚值寄存器FIOxPIN(FIO0PIN??FIO7PIN- 0x2009 C014??0x2009 C094)

该寄存器提供了端口引脚的值,可配置这些值来执行仅为数字的功能。该寄存器将给出引脚的当前逻辑值,而不管引脚是否配置为输入或输出,或作为 GPIO或作为其它可选的数字功能。

例如,特殊的端口引脚可能具有 GPIO输入、GPIO 输出、UART 接收和 PWM 输出等可选功能。无论该引脚配置成何种功能,都可以从相应的 FIOxPIN 寄存器中读出其当前的逻辑状态。 如果引脚配置为模拟功能,当选择了模拟配置时,引脚状态不能被读出。将引脚选择用作A/D输入会断开与引脚数字部分的连接。在这种情况下,从 FIOxPIN 寄存器中读出的引脚值无效。

写 FIOxPIN 寄存器时, FIOxPIN 寄存器的值会保存到端口输出寄存器,而无需使用 FIOxSET和 FIOxCLR寄存器来获得整个写入值。由于这种特性影响整个端口,因此在应用中时要小心。 通过 FIOxPIN 寄存器访问的端口引脚受到 FIOxMASK 寄存器相应位的限制。 只有在屏蔽寄存器中用0 屏蔽的引脚与高速 GPIO 端口引脚值寄存器的当前内容相互关联。

|

位

|

符号

|

值

|

描述

|

复位值

|

|

31:0(字长数据)

|

FP0VAL

FP1VAL

FP2VAL

FP3VAL

FP4VAL

|

0

1

|

控制的引脚输出设为低电平

控制的引脚输出设为高电平

|

0

|

2.5 高速GPIO端口屏蔽寄存器FIOxMASK (FIO0MASK??FIO7MASK - 0x2009 C010??0x2009 C090)

该寄存器用来屏蔽某些端口引脚,被屏蔽的引脚将无法通过 FIOxPIN、 FIOxSET 或 FIOxCLR寄存器写访问。当读FIOxPIN 寄存器时,屏蔽寄存器还将过滤相应端口的内容。

通过读或写访问,该寄存器中为“0”的位使能相应物理引脚的访问。如果该寄存器中的位为“1”,则相应位将不会通过写访问改变,并且读操作时将不会在更新的 FIOxPIN 寄存器中反映出来。

|

位

|

符号

|

值

|

描述

|

复位值

|

|

31:0(字长数据)

|

FP0VAL

FP1VAL

FP2VAL

FP3VAL

FP4VAL

|

0

1

|

控制的引脚输出设为低电平

控制的引脚输出设为高电平 |

0

|

对于常见的ARM处理器,它们的GPIO口基本上可以配置为输入模式、输出模式、开漏或推挽模式,对于新唐的M0来说,所有I/O都处于准双端模式;对于NXP的M3处理器来说,GPIO可以配置为上拉、下拉、开漏或者中继模式。

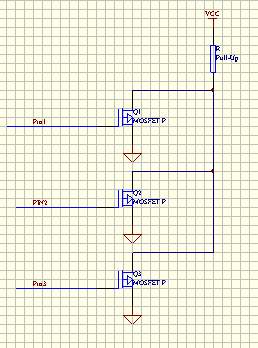

1. 利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up,MOSFET到GND。IC内部仅需很小的栅极驱动电流。如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。形成 “与逻辑” 关系。如图,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平(因此对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑)。

1 输出结构类似 OC门,输出低电平时,内部NMOS导通,驱动能力较强(800uA);输出高电平靠内部上拉电阻,驱动能力弱(60uA)。

2 永远有内部电阻上拉,高电平输出电流能力很弱,所以即使IO口长时间短路到地也不会损坏IO口(同理,IO口低电平输出能力较强,作低电平输出时不能长时间短路到VCC)

3 作输入时,因为OC门有"线与"特性,必须把IO口设为高电平(所以按键多为共地接法)

4 作输出时,输出低电平可以推动LED(也是很弱的),输出高电平通常需要外接缓冲电路(所以LED多为共阳接法)

5 软件模拟 OC结构的总线反而比较方便-----例如 IIC总线

* OC门:三极管的叫集电极开路,场效应管的叫漏极开路,简称开漏输出。具备"线与"能力,有0得0。

* 为什么设计成输出时高电平弱,低电平强----是考虑了当年流行的TTL器件输入

简单的说:

“准双向IO口”在读前必须先用写指令置"1",才能读入;写则无须此步.

“真正的双向IO口”可直接读写.

“三态IO口”有高,低电平,高阻状态,高阻本人理解:相当此脚与内部电路断开.

ARM Cortex M3系列GPIO口介绍(工作方式探讨)的更多相关文章

- 灵动微电子ARM Cortex M0 MM32F0010 GPIO 的配置驱动LED灯

灵动微电子ARM Cortex M0 MM32F0010 GPIO的配置 目录: 1.前言 2.学习方法简要说明 3.要点提示 4.注意事项 5.MM32F0010系统时钟的配置 6.MM32F001 ...

- Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the pro ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

- ARM Cortex M3(V7-M架构)硬件启动程序 一

Cortex-m3启动代码分析笔记 启动代码文件名是STM32F10X.S,它的作用先总结下,然后再分析. 启动代码作用一般是: 1)堆和栈的初始化: 2)中断向量表定义: 3)地址重映射及中断向量表 ...

- ARM Cortex M3(V7-M架构)硬件启动程序 二

解析 STM32 的启动过程 解析STM32的启动过程 当前的嵌入式应用程序开发过程里,并且C语言成为了绝大部分场合的最佳选择.如此一来main函数似乎成为了理所当然的起点——因为C程序往往从main ...

- 《嵌入式软件设计基础——基于ARM Cortex—M3》读书笔记

此书有点深,记录点自己能够看懂的. 1.内存管理一章:讲到变量的类型.生存周期.内存分配. auto static register 局部变量,全局变量 malloc free 内存碎片,消除内存池的 ...

- STM32入门系列-GPIO概念介绍

GPIO(general purpose intput output)是通用输入输出端口的简称,可以通过软件来控制其输入和输出.STM32 芯片的 GPIO 引脚与外部设备连接起来,从而实现与外部通讯 ...

- ARM 架构、ARM7、ARM9、STM32、Cortex M3 M4 、51、AVR 之间有什么区别和联系?(转载自知乎)

ARM架构: 由英国ARM公司设计的一系列32位的RISC微处理器架构总称,现有ARMv1~ARMv8种类. ARM7: 一类采用ARMv3或ARMv4架构的,使用冯诺依曼结构的内核. ...

- ARM linux电源管理——Cortex A系列CPU(32位)睡眠和唤醒的底层汇编实现

ARM linux电源管理——Cortex A系列CPU(32位)睡眠和唤醒的底层汇编实现 承接 http://www.wowotech.net/pm_subsystem/suspend_and_re ...

随机推荐

- Amoeba实现mysql主从读写分离

Amoeba实现mysql主从读写分离 这段在网上看了下关于amoeba的文章,总体感觉好像要比mysql-proxy好的多,也参考了不少的资料,此文章可能与其他文章作者会有雷同的地方,请谅解,但是此 ...

- 他们都没告诉你适配 Android N 需要注意什么

还记得 6.0 对 Apache Http 库的废除导致的应用崩溃吗?还记得 6.0 中 MAC id 始终返回为空导致的唯一 id 混合生成算法大幅失效吗? 1. Android 中 Java 的实 ...

- Java——(九)IO流

一.流的分类 1.输入流和输出流 按照流的流向来分,可以分为输入流和输出流 输入流:只能从中读取数据,而不能向其写入数据. 输出流:只能向其写入数据,而不能从中读取数据. 此处的输入.输出涉及一个方向 ...

- 第九章------HAL

HAL是建立在Linux驱动之上的的程序库,他是一个应用层,它的作用保护内部私有.有一种是位于Android层次的系统运行库层,Linux中只保留与寄存器相互的代码,通过HAL进行数据的传递. 为An ...

- UVA - 11572 Unique Snowflakes

/* STLsort离散化==T 手工sort离散化==T map在线==T map离线处理c==A 240ms */ #include<cstdio> #include<map&g ...

- javascript中,你真的会用console吗?

使用console进行性能测试和计算代码运行时间 对于前端开发人员,在开发过程中经常需要监控某些表达式或变量的值,如果使用用debugger会显得过于笨重,最常用的方法是会将值输出到控制台上方便调试. ...

- HTML5常用标签

section 板块,用于划分页面的不同区域或者划分文章里不同的节 ↓ header 页面头部或者板块section头部 ↓ footer 页面底部或者section底部 ↓ nav 导航(包含 ...

- Java方法-数组

[Java数组] 1. 用sort()方法对Java数组进行排序,及如何使用 binarySearch() 方法来查找数组中的元素 binarySearch() 返回值: 如果它包含在数组中,则返回搜 ...

- MongoDB 重启之后无法连接问题

困扰了一段时间的问题终于知道原因了,每次重启MongoDB服务器就会导致无法启动服务. 通过观察发现,每一次重启完了之后,MongoDB 会进行内存数据加载,而原来服务器内存配置过低,因此导致内存加载 ...

- (转)asp.net分页存储过程

Asp.Net分页存储过程 SQL分页语句 一.比较万能的分页: sql代码: 1 2 3 select top 每页显示的记录数 * from topic where id not in (sel ...