SDRAM初始化

DDR配置过程比较复杂,基本上是按照DDR控制器的时序要求来做的,其中很多参数要结合DDR芯片本身的参数来定,还有些参数是时序参数,要去详细计算。所以DDR配置非常繁琐、细致、专业。所以我们对DDR初始化的态度就是:学会这种思路和方法,结合文档和代码能看懂,会算一些常见的参数即可。

.global sdram_asm_init sdram_asm_init:

ldr r0, =0xf1e00000

ldr r1, =0x0

str r1, [r0, #0x0] /* DMC0 Drive Strength (Setting 2X) */ ldr r0, =ELFIN_GPIO_BASE ldr r1, =0x0000AAAA

str r1, [r0, #MP1_0DRV_SR_OFFSET] // 寄存器中对应0b10,就是2X ldr r1, =0x0000AAAA

str r1, [r0, #MP1_1DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_2DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_3DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_4DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_5DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_6DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_7DRV_SR_OFFSET] ldr r1, =0x00002AAA

str r1, [r0, #MP1_8DRV_SR_OFFSET] /* DMC1 Drive Strength (Setting 2X) */ ldr r0, =ELFIN_GPIO_BASE ldr r1, =0x0000AAAA

str r1, [r0, #MP2_0DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_1DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_2DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_3DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_4DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_5DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_6DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_7DRV_SR_OFFSET] ldr r1, =0x00002AAA

str r1, [r0, #MP2_8DRV_SR_OFFSET] /* DMC0 initialization at single Type*/

ldr r0, =APB_DMC_0_BASE ldr r1, =0x00101000 @PhyControl0 DLL parameter setting, manual 0x00101000

str r1, [r0, #DMC_PHYCONTROL0] ldr r1, =0x00000086 @PhyControl1 DLL parameter setting, LPDDR/LPDDR2 Case

str r1, [r0, #DMC_PHYCONTROL1] ldr r1, =0x00101002 @PhyControl0 DLL on

str r1, [r0, #DMC_PHYCONTROL0] ldr r1, =0x00101003 @PhyControl0 DLL start

str r1, [r0, #DMC_PHYCONTROL0] find_lock_val:

ldr r1, [r0, #DMC_PHYSTATUS] @Load Phystatus register value

and r2, r1, #0x7

cmp r2, #0x7 @Loop until DLL is locked

bne find_lock_val and r1, #0x3fc0

mov r2, r1, LSL #

orr r2, r2, #0x100000

orr r2 ,r2, #0x1000 orr r1, r2, #0x3 @Force Value locking

str r1, [r0, #DMC_PHYCONTROL0] #if /* Memory margin test .. */

orr r1, r2, #0x1 @DLL off

str r1, [r0, #DMC_PHYCONTROL0]

#endif

/* setting DDR2 */

ldr r1, =0x0FFF2010 @ConControl auto refresh off

str r1, [r0, #DMC_CONCONTROL] ldr r1, =DMC0_MEMCONTROL @MemControl BL=, chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL] ldr r1, =DMC0_MEMCONFIG_0 @MemConfig0 256MB config, banks,Mapping Method[:]:linear, :linterleaved, :Mixed

str r1, [r0, #DMC_MEMCONFIG0] ldr r1, =DMC0_MEMCONFIG_1 @MemConfig1

str r1, [r0, #DMC_MEMCONFIG1] ldr r1, =0xFF000000 @PrechConfig

str r1, [r0, #DMC_PRECHCONFIG] ldr r1, =DMC0_TIMINGA_REF @TimingAref .8us*133MHz=(0x40E), 100MHz=(0x30C), 20MHz=(0x9C), 10MHz=(0x4E)

str r1, [r0, #DMC_TIMINGAREF] ldr r1, =DMC0_TIMING_ROW @TimingRow for @200MHz

str r1, [r0, #DMC_TIMINGROW] ldr r1, =DMC0_TIMING_DATA @TimingData CL=

str r1, [r0, #DMC_TIMINGDATA] ldr r1, =DMC0_TIMING_PWR @TimingPower

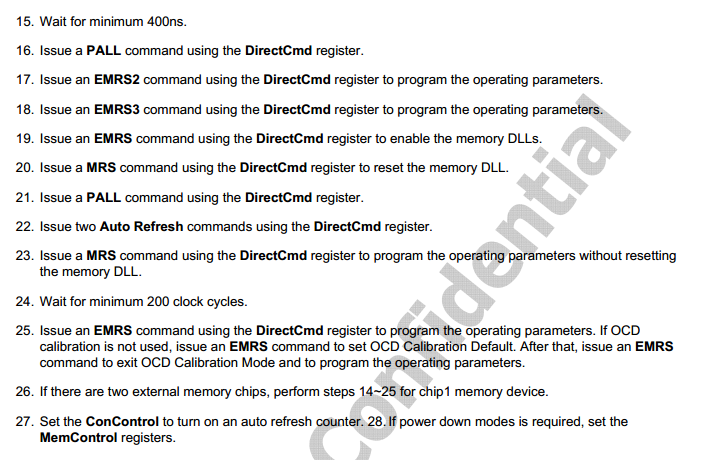

str r1, [r0, #DMC_TIMINGPOWER] ldr r1, =0x07000000 @DirectCmd chip0 Deselect

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00020000 @DirectCmd chip0 EMRS2

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00030000 @DirectCmd chip0 EMRS3

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00000542 @DirectCmd chip0 MRS (MEM DLL reset) CL=, BL=

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00000442 @DirectCmd chip0 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010780 @DirectCmd chip0 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x07100000 @DirectCmd chip1 Deselect

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00120000 @DirectCmd chip1 EMRS2

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00130000 @DirectCmd chip1 EMRS3

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00100542 @DirectCmd chip1 MRS (MEM DLL reset) CL=, BL=

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00100442 @DirectCmd chip1 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110780 @DirectCmd chip1 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x0FF02030 @ConControl auto refresh on

str r1, [r0, #DMC_CONCONTROL] ldr r1, =0xFFFF00FF @PwrdnConfig

str r1, [r0, #DMC_PWRDNCONFIG] ldr r1, =0x00202400 @MemControl BL=, chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL] // 上面是DRAM0初始化步骤

SDRAM初始化的更多相关文章

- SDRAM的初始化与刷新操作---看时序图写代码

SDRAM的初始化与刷新操作---看时序图写代码 1.SDRAM的常见操作 2.初始化就是配置SDRAM 3.SDRAM初始化时序 时序解释如下: 4.刷新操作

- ARM裸板开发:04_MMU 链接地址与运行地址不一致时,(SDRAM)初始化程序地址无关码问题的分析

ARM裸板开发过程,程序的链接地址设置为为0x30000000,而前期的启动代码以及相关硬件的初始化代码需要在内部iRAM(steppingstone,起始地址0x0)的4K中运行.链接地址与运行地址 ...

- SDRAM学习(二)之初始化

目录 1.SDRAM初始化的内容(结合英文数据手册) 2.SDRAM初始化的时序 3.代码的编写 4.modesim的仿真 SDRAM初始化的内容 SDRAMs must be powered up ...

- SDRAM和dcfifo的联合

SDRAM和dcfifo的联合 设计原理 在"SDRAM突发读写页"实验中,留下了一个问题,就是从SDRAM读取数据的速度要与SDRAM的驱动时钟同步,这就造成了读出的数据的速率过 ...

- SDRAM读写一字(下)

SDRAM读写一字 SDRAM控制模块 上电后进行初始化状态,初始化完成后进入空闲状态,在此进行判断如下判断: 如果自刷新时间到,则进行自刷新操作,操作完成后重新进入空闲状态: 如果读使能有效则进行读 ...

- SDRAM读写一字(上)

SDRAM读写一字 系统设计 SDRAM指令 指令 常量名 CKE CSn RAS CASn WEn 备注 空操作 NOP 1 0 1 1 1 行激活 ACTIVE 1 0 0 1 1 读操作 ...

- Smart210学习记录-------内存初始化

买了Smart210的板子,开始学习中,,,,, 今天看了重定位DRAM ,然而内存需要初始化,早上信心满满的我到现在崩溃的我....也不知遭受了什么样的蹂躏 ,,还是记下一点学到的知识吧.. 数据手 ...

- Tiny6410之重定位代码到SDRAM

在上一章中,将代码重定位到了SRAM中,但是这样的做法作用不大.正确的做法的是将代码重定位到更大的主存中,即DRAM.Tiny6410的DRAM控制寄存器最多只能支持两个同一类型的芯片.每个芯片最多可 ...

- 第2阶段——编写uboot之硬件初始化和制作链接脚本lds(1)

目标: 1.关看门狗 2.设置时钟 3.初始化SDRAM (初始化寄存器以及清除bss段) 4.重定位 (将nand/nor中代码COPY到链接地址上,需要初始化nandflash,读flash) 5 ...

随机推荐

- Skype for Business Server 方案

方案说明: 高可用性的配置屏蔽了单点故障,使得当一个服务器节点失效时,另外的可用的节点能够进行服务的接管.可伸缩性的配置可以保证当即时沟通平台的使用用户增加时,该平台应该具有良好的可伸缩性,能非常方便 ...

- LeetCode 144 ——二叉树的前序遍历

1. 题目 2. 解答 2.1. 递归法 定义一个存放树中数据的向量 data,从根节点开始,如果节点不为空,那么 将当前节点的数值加入到 data 中 递归得到其左子树的数据向量 temp,将 te ...

- 七:Web Application Proxy

yarn自带了web接口,默认是和RM一起的(8088端口).但是为了减少从web接口受到的攻击,可以把Web接口单独放在别的机器上. 设置下web代理就行了 Configurations Confi ...

- POJ 1655 Balancing Act(求树的重心)

Description Consider a tree T with N (1 <= N <= 20,000) nodes numbered 1...N. Deleting any nod ...

- C++ STL victor

一.介绍 vector是表示可变大小数组的序列容器. 就像数组一样,vector也采用的连续存储空间来存储元素.也就是意味着可以采用下标对vector的元素进行访问,和数组一样高效.但是又不像数组,它 ...

- TCP系列29—窗口管理&流控—3、Nagle算法

一.Nagle算法概述 之前我们介绍过,有一些交互式应用会传递大量的小包(称呼为tinygrams),这些小包的负载可能只有几个bytes,但是TCP和IP的基本头就有40bytes,如果大量传递这种 ...

- 一个项目的Makefile编写及调试

父Makefile 在src目录下包含很多文件夹,那么需要遍历所有的目录执行Makefile,那么给一个在src目录下的Makefile. # 需要排除的目录 exclude_dirs := incl ...

- Centos安装TFTP/NFS/PXE服务器网络引导安装系统

客户端网卡要求支持以PXE启动,配置都在服务端进行,通过PXE网络启动安装系统流程: 客户端以PXE启动发送DHCP请求: 服务器DHCP应答,包括客户端的IP地址,引导文件所在TFTP服务器: 客户 ...

- 错误 10 非静态的字段、方法或属性“Test10.Program.a”要求对象引用

using System; using System.Collections.Generic; using System.Linq; using System.Text; namespace Test ...

- perf使用的问题,再看perf record,perf record 设置的采样频率,采样频率是如何体现在

当perf stat -e branches 是统计 再看perf record,perf record是为了是记录时间发生的时候的调用栈, 在我的测试代码中总共有200,000,000条branch ...