FPGA的嵌入式乘法器

1. FPGA主要应用在并行处理资源的应用,视频与图像处理,无线通信的中频调制解调器。

嵌入式乘法器可以配置成一个 18 × 18 乘法器,或者配置成两个 9 × 9 乘法器。对于那些大于18 × 18 的乘法运算 ,Quartus® II 软件会将多个嵌入式乘法器模块级联在一起。虽然没有乘法器数据位宽的限制,但数据位宽越大,乘法运算就会越慢。除了 Cyclone IV 器件中的嵌入式乘法器,通过将 M9K 存储器模块用作查找表 (LUT) 可以实现软乘法器。疑问是4输入查找表的,就是一个表,4个输入固定,那么输出 就是固定的。那么这个表是怎么写进去的。

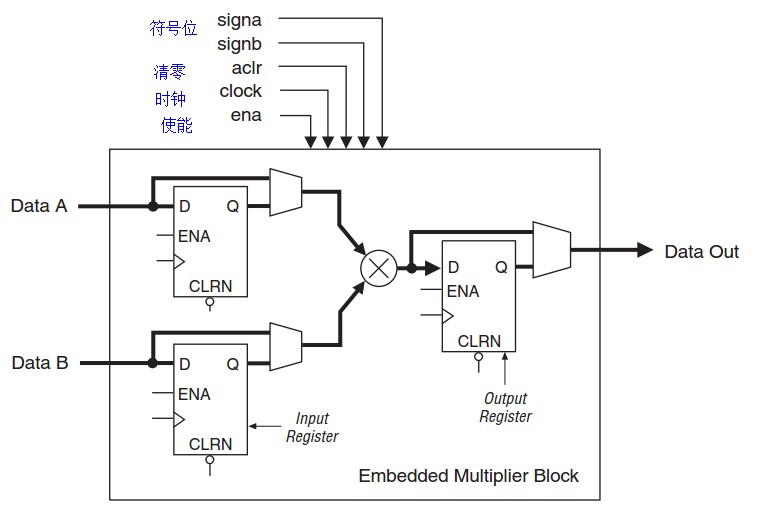

2. 每个嵌入式乘法器均由以下几个单元组成: 乘法器级,输入与输出寄存器,输入与输出接口。

根据乘法器的操作模式,您可以将每个乘法器输入信号连接到输入寄存器,或直接以 9 bit 或 18 bit 的形式连接到内部乘法器。您可以单独地设置乘法器的每个输入是否使用输入寄存器。例如, 将乘法器Data A信号连接到输入寄存器,并且将Data B信号直接连接到内部乘法器。

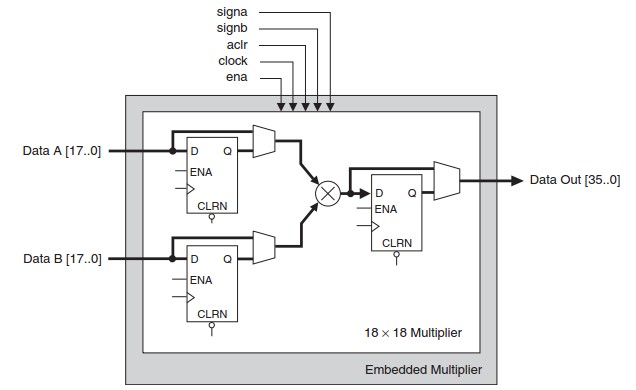

嵌入式乘法器模块的乘法器级支持 9 × 9 或者 18 × 18 乘法器,并支持这些配置之间的其它乘法器。根据乘法器的数据宽度或者操作模式,单一嵌入式乘法器能够同时执行一个或者两个乘法运算。

乘法器的每一个操作数都是一个唯一的有符号或者无符号数。signa与signb信号控制乘法器的输入,并决定值是有符号的还是无符号的。如果signa信号为高电平,则Data A操作数是一个有符号数值。反之,Data A操作数便是一个无符号数值。

3. 根据不同的应用需要,有两种的乘法器工作模式的一种:一个 18 × 18 乘法器,最多两个 9 × 9 独立的乘法器。通过使用 Cyclone IV 器件的嵌入式乘法器,可以实现乘法加法器和乘法累加器功能,这一功能的乘法器部分由嵌入式乘法器来实现,而加法器或者累加器功能则在逻辑单元 (LE) 中实现。

4. 一个 18 × 18 乘法器

5. 最多两个 9 × 9 独立的乘法器

FPGA的嵌入式乘法器的更多相关文章

- 笔记之Cyclone IV第一卷第四章Cyclone IV器件中的嵌入式乘法器

嵌入式乘法器可以配置成一个 18 × 18 乘法器,或者配置成两个 9 × 9 乘法器.对于那些大于18 × 18 的乘法运算 ,Quartus II 软件会将多个嵌入式乘法器模块级联在一起.虽然没有 ...

- FPGA与嵌入式一点见解

FPGA:即现场可编程门阵列,它是在PAL.GAL.CPLD等可编程器件的基础上进一步发展的产物.它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可 ...

- FPGA的嵌入式RAM

FPGA中的嵌入式RAM分为两种:专用的BRAM和分布是RAM(用LUT实现的).这两种RAM又可以配置成单端口和双端口的RAM和ROM.双端口RAM又可以根据读写地址是否在同一块分为Double P ...

- 基于FPGA的线阵CCD图像测量系统研究——笔记

本文是对基于FPGA的线阵CCD图像测量系统研究(作者:高尚)的阅读笔记 第一章绪论 1. 读读看 读了前面的摘要依然没有看懂作者要做什么.接着往下读....终于看到了一个字眼“基于机器视觉的图像测量 ...

- 笔记之Cyclone IV 第一卷第一章FPGA 器件系列概述

因为本人用的黑金四代开发板,中央芯片采用ALTERA的cycloneIV E,所以就此器件阅读altera官网资料,并做相应的笔记,以便于以后查阅 Cyclone IV 器件系列具有以下特性:■ 低成 ...

- 我的 FPGA 学习历程(07)—— BCD 编码:移位加 3 算法

2-10 进制码,也称为 BCD 码,它的编码方式则是通过一个 4 位二进制来表示一个 10 进制数,部分十进制对应的 BCD 码如下 十进制数 | BCD 码 13 --> 0001_0011 ...

- 我的 FPGA 学习历程(05)—— 使用 Modelsim 仿真工具

在第 3 篇中讲到了如何使用图形进行仿真激励输入,图形输入法尽管简单易学,但如若要求复杂的仿真输入激励.较长的仿真时间或是要求打印输出信息乃至输出文件日志则显得不够用了. 本篇以上一篇的 3-8 译码 ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- FPGA中的“门”

逻辑门 在ASIC的世界里,衡量器件容量的常用标准是等效门.这是因为不同的厂商在单元库里提供了不同的功能模块,而每个功能模块的实现都要求不同数量的晶体管.这样在两个器件之间比较容量和复杂度就很困难. ...

随机推荐

- Ubuntu 12.04 安装Chrome步骤

一.添加PPA 从Google Linux Repository(http://www.google.com/linuxrepositories/)下载安装Key,或把下面的代码复制进终端,回车,需要 ...

- IT人们给个建议

开篇声明:我本身是中学老师,师范类大学计算机专业毕业,现在马上研究生学位就要拿上了,平时在学校搞网络维护什么的,事少,业余时间充足,也不想拘泥于做老师拿点工资,觉得白学计算机了,所以也搞些业余开发,如 ...

- 匿名union

#include <stdio.h> enum node_type{ t_int,t_double}; struct node{ enum node_type type; ...

- Docker官方文档翻译1

转载请标明出处: https://blog.csdn.net/forezp/article/details/80098675 本文出自方志朋的博客 本系列教程翻译于docker文档,文档地址:http ...

- stl之std::remove_copy

template <class InputIterator, class OutputIterator, class T> OutputIterator remove_copy (Inpu ...

- 插入排序_C语言_数组

插入排序_C语言_数组 #include <stdio.h> void insertSort(int *); int main(int argc, const char * argv[]) ...

- 示例浅谈PHP与手机APP开发,即API接口开发

示例浅谈PHP与手机APP开发,即API接口开发 API(Application Programming Interface,应用程序接口)架构,已经成为目前互联网产品开发中常见的软件架构模式,并且诞 ...

- Sass 基础(六)

join() 函数 join()函数是将两个列表连接合并成一个列表. >>join(10px 20px, 30px 40px) (10px 20px 20px 40px) >> ...

- 伪造Http请求IP地址

注意:伪造Http请求IP地址一般为非推荐使用手段 一般使用:简单投票网站重复投票,黑别人网站 在项目开发中(web项目),我负责的系统(简称PC),需要调其它系统接口,并且该系统需要获取客户端(浏览 ...

- 5820. 【NOIP提高A组模拟2018.8.16】 非法输入(模拟,字符串)

5820. [NOIP提高A组模拟2018.8.16] 非法输入 (File IO): input:aplusb.in output:aplusb.out Time Limits: 1000 ms ...