JETSON TK1 ~ 控制GPIO

首先建立个存放gpio代码的文件夹,CD到该文件夹。

git clone git://github.com/derekmolloy/boneDeviceTree/

解压后会出现几个文件

GPIO文件夹内的SimpleGPIO.cpp和SimpleGPIO.h复制到eclipse工作空间的src文件夹下。

包含相关头文件后编写代码:

//============================================================================

// Name : CPPT1.cpp

// Author : Kopu

// Version :

// Copyright : Oh,Shit!

// Description : Hello World in C++, Ansi-style

//============================================================================

#include "stdio.h"

#include "stdlib.h"

#include <iostream>

#include "SimpleGPIO.h"

using namespace std; const int GPIO_PU6_P58 = ;

const int GPIO_PH1_P50 = ; unsigned int IO_Data=; void delay_ms(unsigned int num)

{

unsigned int i,j;

for(i=num;i>;i--)

for(j=;j>;j--);

}

int main(void)

{

gpio_export(GPIO_PH1_P50);

gpio_export(GPIO_PU6_P58);

gpio_set_dir(GPIO_PH1_P50, INPUT_PIN);

gpio_set_dir(GPIO_PU6_P58, OUTPUT_PIN);

while()

{

gpio_get_value(GPIO_PH1_P50,&IO_Data);

if(IO_Data)printf("1\n");

else printf("0\n");

gpio_set_value(GPIO_PU6_P58, HIGH);

delay_ms();

gpio_set_value(GPIO_PU6_P58, LOW);

delay_ms();

}

return ;

}

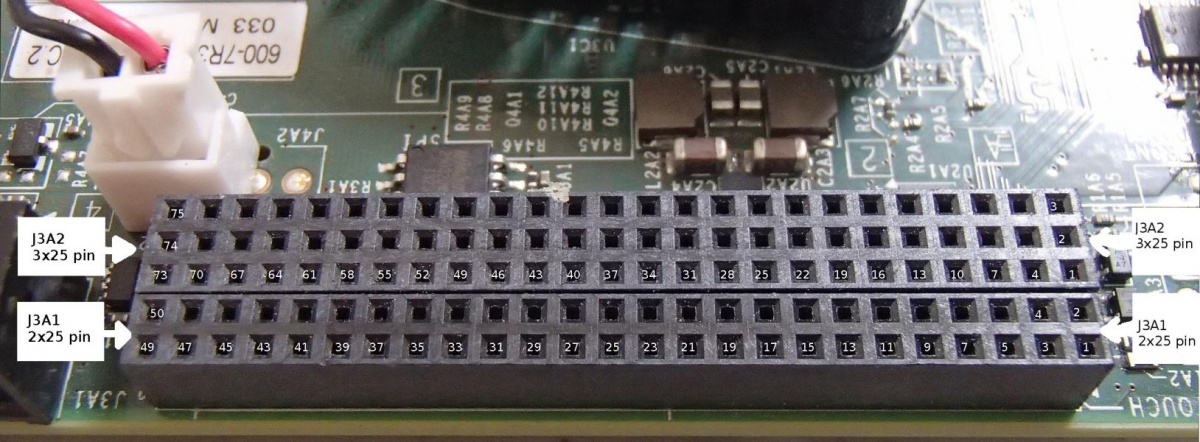

关于上面的gpio对应TK1上的引脚:

| Port | sysfs filename | Physical pin | Notes |

| GPIO_PH1 | gpio57 | Pin 50 on J3A1 | |

| GPIO_PU0 | gpio160 | Pin 40 on J3A2 | |

| GPIO_PU1 | gpio161 | Pin 43 on J3A2 | |

| GPIO_PU2 | gpio162 | Pin 46 on J3A2 | (Disabled by default) |

| GPIO_PU3 | gpio163 | Pin 49 on J3A2 | |

| GPIO_PU4 | gpio164 | Pin 52 on J3A2 | |

| GPIO_PU5 | gpio165 | Pin 55 on J3A2 | |

| GPIO_PU6 | gpio166 | Pin 58 on J3A2 |

| J3A1 | |||||||

| Pin | Signal name | Tegra K1 ball | Usage/description | Type/dir default | Associated voltage rail | Tegra pad type | Connector row |

| 1 | +5V_SYS | n/a | Main 5V from system | Power | - | - | 1 |

| 2 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 3 | +1.8V_VDDIO | n/a | Main 1.8V supply from PMU switcher 5 | Power | - | - | 1 |

| 4 | TS_SPI_SCK | ULPI_NXT | SPI clock for Touchscreen controller (if SPI used) | Input | +1.8V_VDDIO | ST | 2 |

| 5 | TS_SPI_MOSI | ULPI_CLK | SPI MOSI for Touchscreen controller (if SPI used) | Input | +1.8V_VDDIO | ST | 1 |

| 6 | TS_SPI_CS_L | ULPI_STP | SPI chip select for Touchscreen controller (if SPI) | Input | +1.8V_VDDIO | ST | 2 |

| 7 | TS_SPI_MISO | ULPI_DIR | SPI MISO for Touchscreen controller (if SPI used) | Output | +1.8V_VDDIO | ST | 1 |

| 8 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 9 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 10 | +3.3V_RUN_TOUCH | n/a | AMS PMIC LDO9 | Power | - | - | 2 |

| 11 | TS_SHDN_L | GPIO_PK1 | Shutdown control for Touchscreen controller | Input | +1.8V_VDDIO | CZ | 1 |

| 12 | TS_CLK | CLK2_OUT | Clock for Touchscreen controller | Input | +1.8V_VDDIO | ST | 2 |

| 13 | TS_RESET_L | GPIO_PK4 | Reset for Touchscreen controller | Input | +1.8V_VDDIO | CZ | 1 |

| 14 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 15 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 16 | +3.3V_SYS | n/a | Main 3.3V supply | Power | - | - | 2 |

| 17 | GPIO_PK2 | GPIO_PK2 | Available GPIO | Output | +1.8V_VDDIO | CZ | 1 |

| 18 | GEN2_I2C_SCL_3.3V | GEN2_I2C_SCL | 3.3V I2C IF (Pulled up to +3.3V_LP0) | Input, Open Drain | +3.3V_LP0 | DD | 2 |

| 19 | +1.8V_VDDIO | n/a | Main 1.8V supply from PMU switcher 5 | Power | - | - | 1 |

| 20 | GEN2_I2C_SDA_3.3V | GEN2_I2C_SDA | 3.3V I2C IF (Pulled up to +3.3V_LP0) | Bidir, Open Drain | DD | 2 | |

| 21 | GEN1_I2C_SCL | GEN1_I2C_SCL | 1.8V I2C (Pulled up to +1.8V_VDDIO) | Input, Open Drain | +1.8V_VDDIO | DD | 1 |

| 22 | +3.3V_RUN | n/a | +3.3V rail that is off in LP0 | Power | - | - | 2 |

| 23 | GEN1_I2C_SDA | GEN1_I2C_SDA | 1.8V I2C (Pulled up to +1.8V_VDDIO) | Bidir, Open Drain | +1.8V_VDDIO | DD | 1 |

| 24 | EN_AVDD_LCD | n/a | Enable for Embedded display from PMU GPIO4 | Input | - | - | 2 |

| 25 | +VDD_MUX | n/a | Main 12V from Jack | Power | 1 | ||

| 26 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 27 | EN_VDD_BL | DAP3_DOUT | Backlight supply enable | Input | +1.8V_VDDIO | ST | 1 |

| 28 | DP_AUX_P | DP_AUX_P | eDP AUX control interface (+) | Bidir | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 29 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 30 | DP_AUX_N | DP_AUX_N | eDP AUX control interface (-) | Bidir | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 31 | LVDS_TXD0_P | LVDS_TXD0_P | LVDS Data lane 0 (+) or eDP Data lane 2 (+) | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 32 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 33 | LVDS_TXD0_N | LVDS_TXD0_N | LVDS Data lane 0 (-) or eDP Data lane 2 (+) | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 34 | LVDS_TXD1_P | LVDS_TXD1_P | LVDS Data lane 1 (+) or eDP Data lane 1 (+) | Input | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 35 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 36 | LVDS_TXD1_N | LVDS_TXD1_N | LVDS Data lane 1 (-) or eDP Data lane 1 (-) | Input | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 37 | LVDS_TXD3_P | LVDS_TXD3_P | LVDS Data lane 3 (+) - Not used for eDP | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 38 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 39 | LVDS_TXD3_N | LVDS_TXD3_N | LVDS Data lane 3 (-) - Not used for eDP | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 40 | LVDS_TXD2_P | LVDS_TXD2_P | LVDS Data lane 2 (+) or eDP Data lane 0 (+) | Input | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 41 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 42 | LVDS_TXD2_N | LVDS_TXD2_N | LVDS Data lane 2 (-) or eDP Data lane 0 (-) | Input | +1.05V_RUN_AVDD | LVDS/DP | 2 |

| 43 | LVDS_TXD4_N | LVDS_TXD4_N | LVDS Clock lane (+) or eDP Data lane 3 (+) | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 44 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 45 | LVDS_TXD4_P | LVDS_TXD4_P | LVDS Clock lane (-) or eDP Data lane 3 (-) | Input | +1.05V_RUN_AVDD | LVDS/DP | 1 |

| 46 | EPP_HPD | DP_HPD | eDP display Hot Plug Detect input | Output | +3.3V_LP0 | ST | 2 |

| 47 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 48 | LCD_BL_EN | GPIO_PH2 | Backlight enable | Input | +1.8V_VDDIO | CZ | 2 |

| 49 | LCD_TE | KB_ROW6 | Tearing Effect from embedded display (if supported) | Output | +1.8V_VDDIO | ST | 1 |

| 50 | LCD_BL_PWM | GPIO_PH1 | Backlight PWM | Input | +1.8V_VDDIO | CZ | 2 |

三排的插座:

| J3A2 | |||||||

| Pin | Signal name | Tegra K1 ball | Usage/description | Type/dir default | Associated voltage rail | Tegra pad type | Connector row |

| 1 | +5V_SYS | n/a | Main 5v from system | Power | - | - | 1 |

| 2 | CAM2_PWDN | GPIO_PBB6 | Power Down for Camera 2 | input | +1.8V_RUN_CAM | ST | 2 |

| 3 | +1.05V_RUN_CAM_REAR | n/a | AMS PMIC LDO7 for Camera 1 | Power | - | - | 3 |

| 4 | CAM2_MCLK | GPIO_PBB0 | Master Reference Clock for Camera 2 | input | +1.8V_RUN_CAM | ST | 1 |

| 5 | CAM_RST_L | GPIO_PBB3 | Reset for Camera(s) | input | +1.8V_RUN_CAM | ST | 2 |

| 6 | +2.8V_RUN_CAM | n/a | AMS PMIC LDO4 for Camera(s) | Power | - | - | 3 |

| 7 | CAM2_GPIO | GPIO_PCC2 | GPIO for Camera 2 | Bidir | +1.8V_RUN_CAM | ST | 1 |

| 8 | CAM_I2C_SDA | CAM_I2C_SDA | I2C Data for Camera(s) | Bidir, Open Drain | +1.8V_RUN_CAM | DD | 2 |

| 9 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 10 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 11 | CAM_I2C_SCL | CAM_I2C_SCL | I2C Clock for Camera(s) | Input, Open Drain | +1.8V_RUN_CAM | SS | 2 |

| 12 | CSI_A_CLK_P | CSI_A_CLK_P | CSI Clock (+) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 13 | CSI_E_CLK_N | CSI_E_CLK_N | CSI Clock (-) for Camera 2 | Output | +1.2V_GEN_AVDD | CSI | 1 |

| 14 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 15 | CSI_A_CLK_N | CSI_A_CLK_N | CSI Clock (-) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 16 | CSI_E_CLK_P | CSI_E_CLK_P | CSI Clock (+) for Camera 2 | Output | +1.2V_GEN_AVDD | CSI | 1 |

| 17 | CSI_E_D0_N | CSI_E_D0_N | CSI Data Lane 0 (-) for Camera 2 | Output | +1.2V_GEN_AVDD | CSI | 2 |

| 18 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 19 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 20 | CSI_E_D0_P | CSI_E_D0_P | CSI Data Lane 0 (+) for Camera 2 | Output | +1.2V_GEN_AVDD | CSI | 2 |

| 21 | CSI_A_D1_N | CSI_A_D1_N | CSI Data Lane 1 (-) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 22 | +1.2V_RUN_CAM_FRONT | n/a | AMS PMIC LDO5 for Camera 2 | Power | - | - | 1 |

| 23 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 24 | CSI_A_D1_P | CSI_A_D1_P | CSI Data Lane 1 (+) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 25 | +2.8V_RUN_CAM_AF | n/a | AMS PMIC LDO10 for Camera 1 | Power | +1.2V_GEN_AVDD | CSI | 1 |

| 26 | +1.8v_VDDIO | n/a | AMS Switcher 5 | Power | - | - | 2 |

| 27 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 28 | +1.8V_GEN_AVDD | n/a | AMS PMIC LDO2, used to sync HSIC rails | Power | - | - | 1 |

| 29 | +1.8V_RUN_CAM | n/a | AMS PMIC LDO1 | Power | - | - | 2 |

| 30 | CSI_A_D0_N | CSI_A_D0_N | CSI Data Lane 0 (-) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 31 | HSIC1_STROBE | HSIC1_STROBE | HSIC Strobe | Bidir | +1.2V_GEN_AVDD | HSIC | 1 |

| 32 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 33 | CSI_A_D0_P | CSI_A_D0_P | CSI Data Lane 0 (+) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 34 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 35 | HSIC1_DATA | HSIC1_DATA | HSIC Data | Bidir | +1.2V_GEN_AVDD | HSIC | 2 |

| 36 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 37 | +1.8V_VDDIO | n/a | AMS Switcher 5 | Power | - | - | 1 |

| 38 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 39 | CSI_B_D1_N | CSI_B_D1_N | CSI Data Lane 3 (-) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 40 | GPIO_PU0 | GPIO_PU0 | GPIO PU0: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 41 | BR_UART_TXD | KB_ROW9 | For PM342 style Laguna FFD header | Input | +1.8V_VDDIO | - | 2 |

| 42 | CSI_B_D1_P | CSI_B_D1_P | CSI Data Lane 3 (+) for Camera 1 | Output | +1.2V_GEN_AVDD | - | 3 |

| 43 | GPIO_PU1 | GPIO_PU1 | GPIO PU1: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 44 | BR_UART1_RXD | KB_ROW10 | For PM342 style Laguna FFD header | Output | +1.8V_VDDIO | - | 2 |

| 45 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 46 | GPIO_PU2 | GPIO_PU2 | GPIO PU2: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 47 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 48 | CSI_B_D0_P | CSI_B_D0_P | CSI Data Lane 2 (+) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 49 | GPIO_PU3 | GPIO_PU3 | GPIO PU3: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 50 | PWR_I2C_SCL | PWR_I2C_SCL | Power I2C Clock: For Nvidia use only | Input, Open Drain | +1.8V_VDDIO | DD | 2 |

| 51 | CSI_B_D0_N | CSI_B_D0_N | CSI Data Lane 2 (-) for Camera 1 | Output | +1.2V_GEN_AVDD | CSI | 3 |

| 52 | GPIO_PU4 | GPIO_PU4 | GPIO PU4: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 53 | PWR_I2C_SDA | PWR_I2C_SDA | Power I2C Data: For Nvidia use only | Bidir, Open Drain | +1.8V_VDDIO | DD | 2 |

| 54 | GND | n/a | Tied to common GND | Ground | - | - | 3 |

| 55 | GPIO_PU5 | GPIO_PU5 | GPIO PU5: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 56 | GEN1_I2C_SCL | GEN1_I2C_SCL | GEN1 I2C Clock: 1.8V I2C IF available for general use | Input, Open Drain | +1.8V_VDDIO | DD | 2 |

| 57 | CAM1_GPIO | GPIO_PCC1 | GPIO for Camera 1 | Bidir | +1.8V_RUN_CAM | ST | 3 |

| 58 | GPIO_PU6 | GPIO_PU6 | GPIO PU6: Available for general use | Bidir | +1.8V_VDDIO | ST | 1 |

| 59 | GEN1_I2C_SDA | GEN1_I2C_SDA | GEN1 I2C Data: 1.8V I2C IF available for general use | Bidir, Open Drain | +1.8V_VDDIO | DD | 2 |

| 60 | CAM1_AF_PWDN | GPIO_PBB7 | Autofocus Powerdown for Camera 1 | Input | +1.8V_RUN_CAM | ST | 3 |

| 61 | ONKEY_L | KB_COL0 (indirect) | Power On (to PMU ONKEY & gated version to Tegra) | Bidir | +2.5V_AON_RTC | - | 1 |

| 62 | GND | n/a | Tied to common GND | Ground | - | - | 2 |

| 63 | CAM_FLASH | GPIO_PB4 | Flash enable to control camera flash driver | Input | +1.8V_RUN_CAM | ST | 3 |

| 64 | PMU_RESET_IN_L | n/a | System Reset signal | Bidir | +2.5V_AON_RTC | - | 1 |

| 65 | UART2_RXD | UART2_RXD | UART 2 Receive | Output | +1.8V_VDDIO | ST | 2 |

| 66 | CAM1_PWDN | GPIO_PBB5 | Powerdown for Camera 1 | Input | +1.8V_RUN_CAM | ST | 3 |

| 67 | FORCE_RECOVERY_L | GPIO_PI1 (indirect) | Force Recovery: To enter Forced Recovery mode | Bidir | +2.5V_AON_RTC | - | 1 |

| 68 | UART2_TXD | UART2_TXD | UART 2 Transmit | Input | +1.8V_VDDIO | ST | 2 |

| 69 | CAM1_MCLK | CAM_MCLK | Master Reference Clock for Camera 1 | Input | +1.8V_RUN_CAM | ST | 3 |

| 70 | CLK3_OUT | CLK3_OUT | Clock 3 Output: Available clock source from Tegra K1 | Input | +1.8V_RUN_CAM | ST | 1 |

| 71 | UART2_CTS_L | UART2_CTS_L | UART 2 Clear to Send | Output | +1.8V_VDDIO | ST | 2 |

| 72 | NC | n/a | Not used | - | - | - | 3 |

| 73 | GND | n/a | Tied to common GND | Ground | - | - | 1 |

| 74 | UART2_RTS_L | UART2_RTS_L | UART 2 Request to Send | Input | +1.8V_VDDIO | ST | 2 |

| 75 | NC | n/a | Not used | - | - | - | 3 |

关于GPIO和其他相关资源相关

1:http://elinux.org/Jetson/GPIO

2:http://elinux.org/Jetson/Tutorials/GPIO

3:http://elinux.org/Jetson/Tutorials/Vision-controlled_GPIO#Testing_GPIO_on_Jetson_TK1

JETSON TK1 ~ 控制GPIO的更多相关文章

- Android(Java)控制GPIO的方法及耗时分析

前面两篇分别介绍了通过脚本和C代码读写/sys/class/gpio以控制GPIO.实际项目调试时经常还需要在Java代码里控制GPIO,其实现与C代码类似,唯一不同是Android权限.本文重点介绍 ...

- Android(Linux)控制GPIO方法二

前文<Android(Linux)控制GPIO的方法及实时性分析>主要使用Linux shell命令控制GPIO,该方法可在调试过程中快速确定GPIO硬件是否有问题,即对应的GPIO是否受 ...

- Android(Linux)控制GPIO的方法及实时性分析

Linux下控制GPIO的方法有N种,详细请参考<RPi GPIO Code Samples>,文中用十多种语言演示了如何控制GPIO,非常全面详尽.因此,这里不再多做赘述,仅把调试过程中 ...

- 结合阿里云服务器,设置家中jetson tk1随时远程登陆

前提条件: 1.路由配置dmz主机为tk1的ip ,设置路由器中ssh 端口22的访问权限 2.有一台远程服务器,服务器安装了php可以运行php文件(我使用的是阿里云) 家中tk1配置: 脚本pyt ...

- Jetson TK1刷机+配置Mini PCI-e无线网卡

最近买了台4K电视,觉得可以当显示器用,但没主机,不知怎的想到了Jetson TK1,于是一冲动买了.因为没网线,而Jetson TK1没有无线网卡,所以也折腾了一番,记录一下,给万一也有像我一样没有 ...

- Jetson TK1 Restore 步骤

Jetson TK1 Restore 步骤 下载驱动包和文件系统包: 1:驱动包 2:文件系统 具体参见文档:http://download.csdn.net/detail/xiabodan/7 ...

- (原创) jetson tk1 初始化

1. 相关的网站: 1. Jetson TK1 support https://developer.nvidia.com/jetson-tk1-support 2.official Wiki fo ...

- RaspberryPi2B使用bcm2835c库控制GPIO

RaspberryPi2B使用bcm2835c库控制GPIO 网上有很多RaspberryPi控制GPIO的方法,有Python.WiringPi.bcm2835 C library 使用bcm283 ...

- EasyARM i.mx287学习笔记——通过modbus tcp控制GPIO

0 前言 本文使用freemodbus协议栈,在EasyARM i.mx287上实现了modbus tcp从机. 在该从机中定义了线圈寄存器.当中线圈寄存器地址较低的4位和EasyARM的P2 ...

随机推荐

- nginx 启动,重启,添加开机启动等相关命令

nginx -t 测试 配置文件是否正确,同时可以查看配置文件路径 nginx -c /usr/local/nginx/conf/nginx.conf 启动nginx ps -ef|grep ng ...

- nodejs session 设计

会话管理 { //保存会话 _data : {}, /** 会话基本操作 ***/ //查找会话 getSession : function(id){}, //创建会话 createSession : ...

- Spring IOC源代码具体解释之整体结构

Spring ICO具体解释之整体结构 IOC介绍 IOC, spring的核心.贯穿Spring始终.直观的来说.就是由spring来负责控制对象的生命周期和对象间的关系,将对象之间的关系抽象出来. ...

- xss跨站脚本攻击与防御读书笔记(原创)

XSS在客户端执行 可以任意执行js代码 0x01 xss 的利用方式 1. 钓鱼 案例:http://www.wooyun.org/bugs/wooyun-2014-076685 我是 ...

- eletron 播放rtmp flash 播放器问题

1 安装 flash https://www.flash.cn/ 2 man.js 配置 参考 https://newsn.net/say/electron-flash-win.html 3 播放器 ...

- Python Random随机数

Python产生随机数的功能在random模块中实现.实现了各种分布的伪随机数生成器 该模块能够生成0到1的浮点随机数,也能够在一个序列中进行随机选择.产生的随机数能够是均匀分布.高斯分布,对数正态分 ...

- 从头開始写项目Makefile(五):嵌套运行

[版权声明:转载请保留出处:blog.csdn.net/gentleliu.Mail:shallnew at 163 dot com] 在大一些的项目里面,全部源码不会仅仅放在同一个文件夹,一般各个功 ...

- js向后台传递对象

js: }; $.ajax({ url: "/.../...", type: "POST", async: false, data: JSON.stringif ...

- 【深入JAVA EE】Spring配置文件解析

在阅读的过程中有不论什么问题,欢迎一起交流 邮箱:1494713801@qq.com QQ:1494713801 一.Spring头信息 Spring配置文件的头部信息通常是固定不变的.但每个标 ...

- zoj 2949 - Coins of Luck

题目:有2中面条各n碗.每次抛硬币推断吃哪一种(到一种吃完为止).问抛硬币的数学期望. 分析:动态规划.概率dp.求出每种结束状态(即,有一种吃完)的概率,分别乘以步长即为期望. 大黄解法:状态位剩余 ...