全志T3+FPGA国产核心板——Pango Design Suite的FPGA程序加载固化

本文主要基于紫光同创Pango Design Suite(PDS)开发软件,演示FPGA程序的加载、固化,以及程序编译等方法。适用的开发环境为Windows 7/10 64bit。

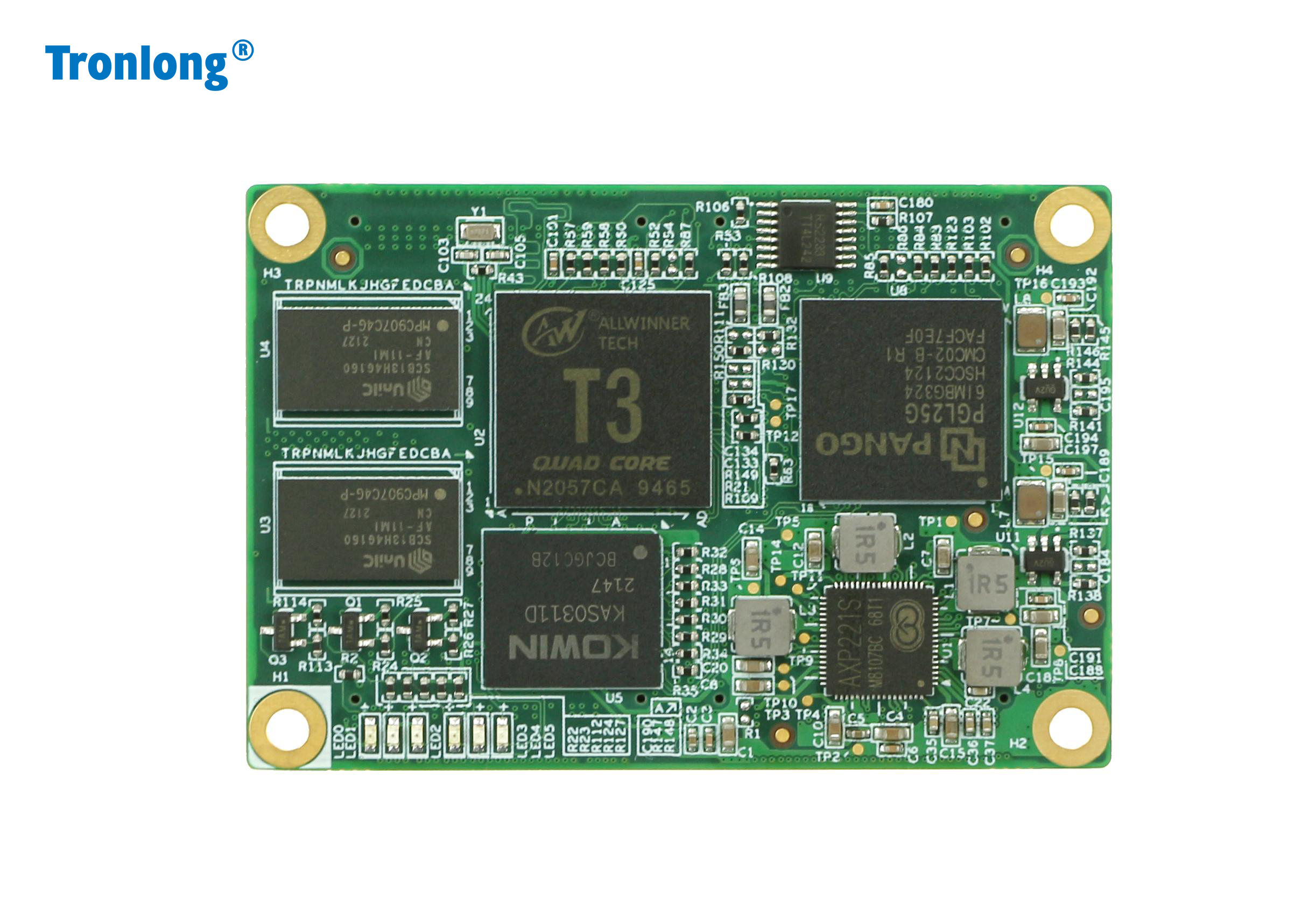

测试板卡为全志T3+Logos FPGA核心板,它是一款基于全志科技T3四核ARM Cortex-A7处理器 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核全国产工业核心板,ARM Cortex-A7处理单元主频高达1.2GHz。核心板CPU、FPGA、ROM、RAM、电源、晶振、连接器等所有器件均采用国产工业级方案,国产化率100%。

核心板内部T3与Logos通过SPI、CSI、I2C通信总线连接,并通过工业级B2B连接器引出LVDS DISPLAY、RGB DISPLAY、MIPI DSI、TVOUT、TVIN、CSI、GMAC、EMAC、USB、SATA、SDIO、UART、SPI、TWI等接口及FPGA IO引脚,支持双屏异显、Mali400 MP2 GPU、1080P@45fps H.264视频硬件编解码。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

FPGA程序位于产品资料Demo目录,请将对应的FPGA程序拷贝至Windows非中文路径下。下表为Demo目录的FPGA程序目录结构及主要文件说明。

表 1

|

目录 |

文件/目录 |

说明 |

|

|

bin |

xxx.sbit |

可执行程序(BitStramFile文件),用于在线加载 |

|

|

xxx.sfc |

可执行程序,用于固化至SPI FLASH |

||

|

project |

xxx_pgl25g/xxx_pgl50g |

constraints |

约束文件目录 |

|

hdl |

Verilog源码文件目录 |

||

|

xxx.pds |

Pango Design Suite工程文件 |

||

按照本文档操作前,请先参考软件安装相关文档安装Pango Design Suite,并将评估板通过配套的FPGA下载器正常连接至PC机。

程序加载

本小节以led_flash案例为例,演示程序加载方法。

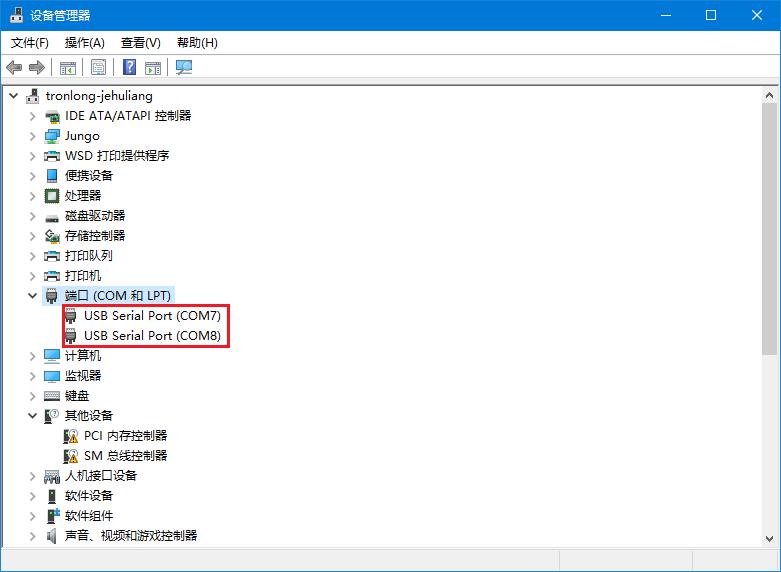

- 打开Windows的设备管理器,查看并确认FPGA下载器已正常连接至PC机。

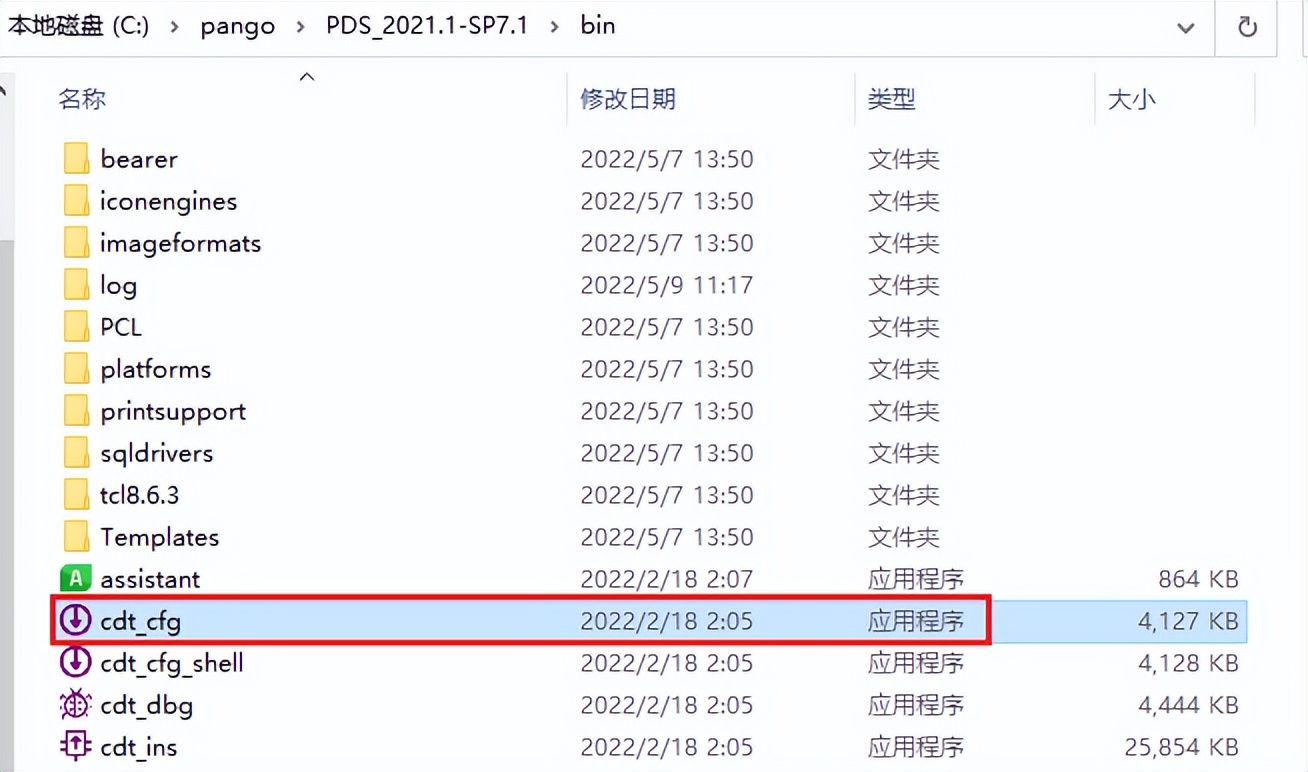

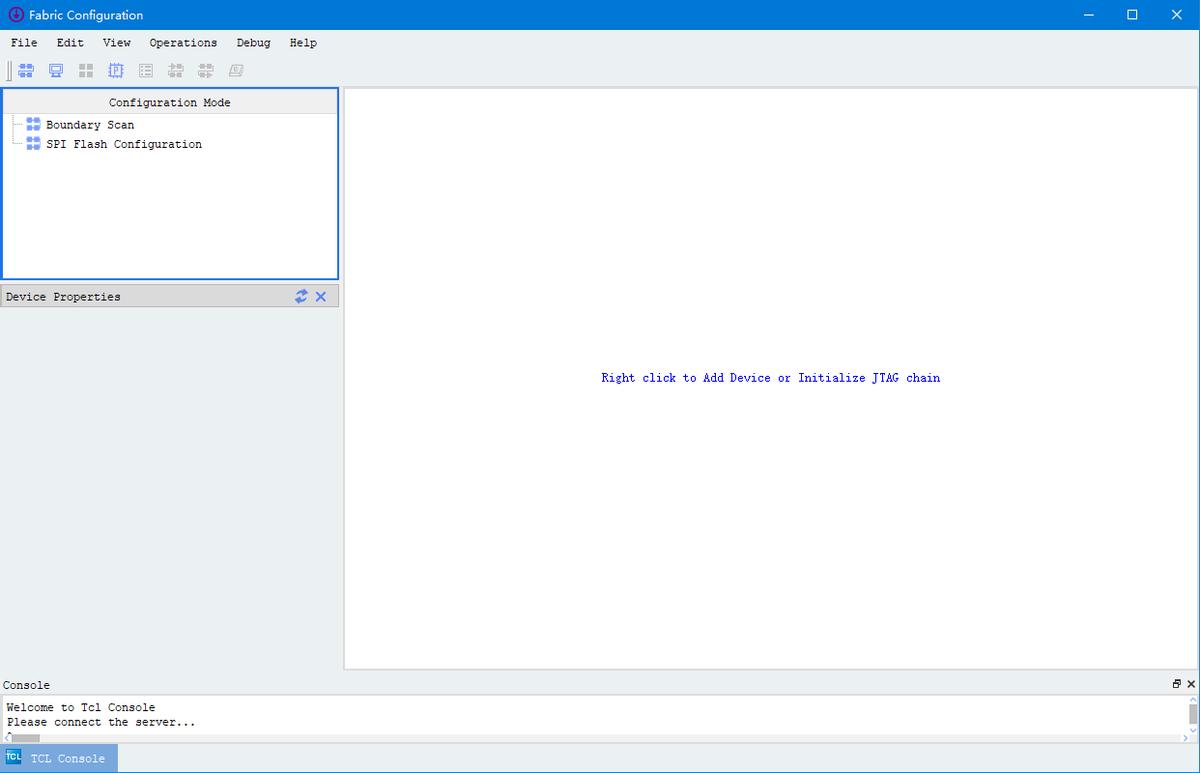

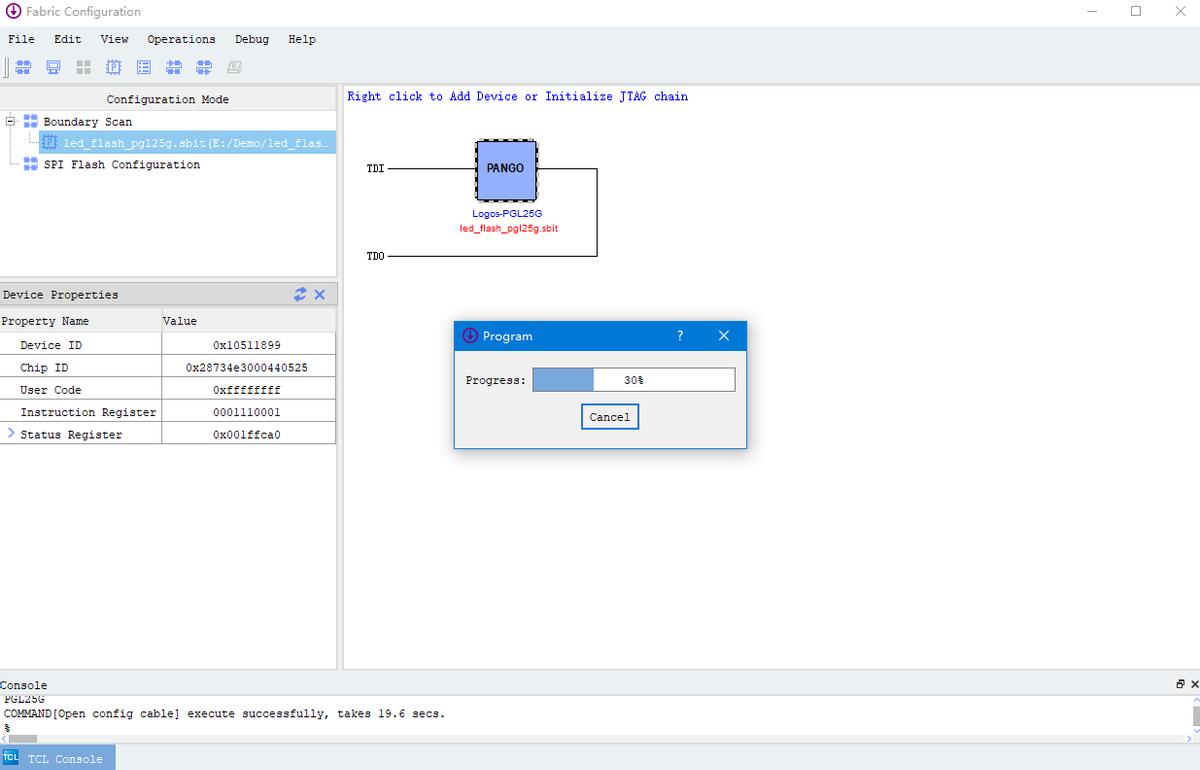

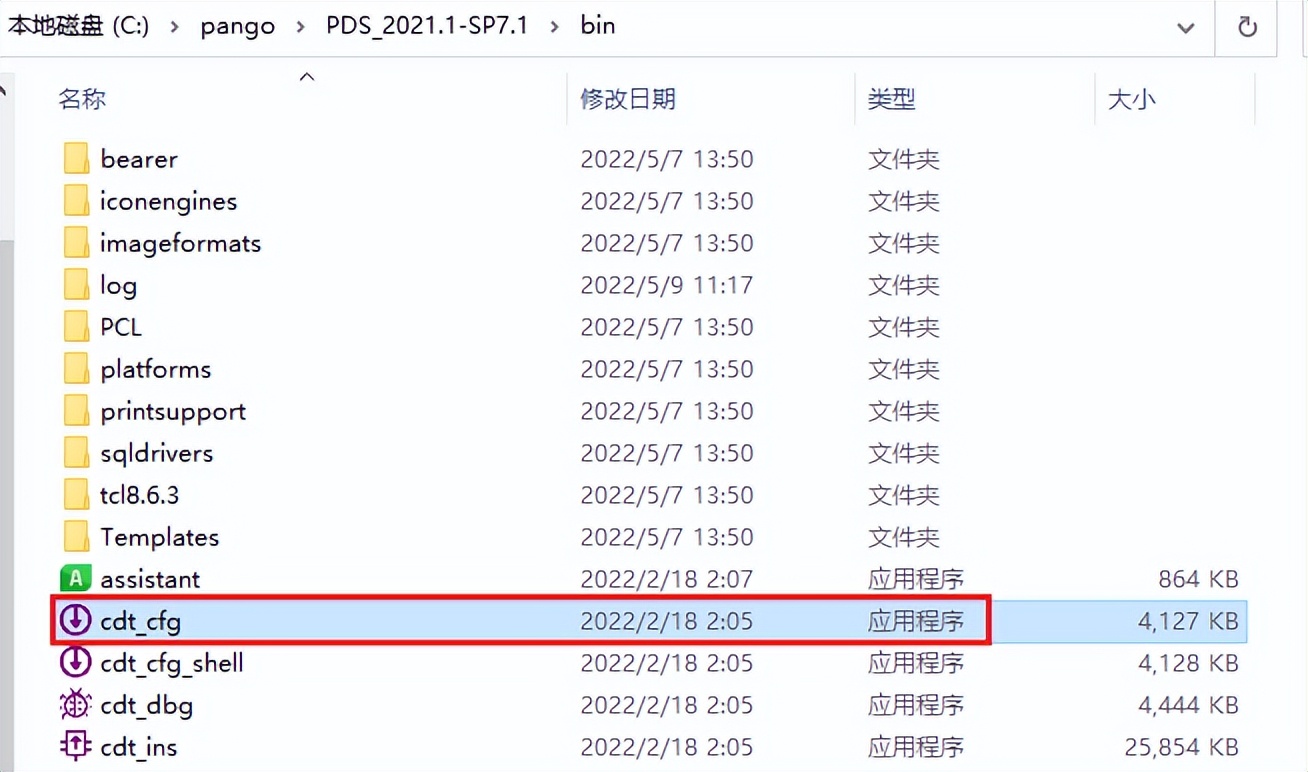

双击Pango Design Suite安装目录下"C:\pango\PDS_2021.1-SP7.1\bin\cdt_cfg.exe",打开Fabric Configuration界面。

图 2

图 2 图 3

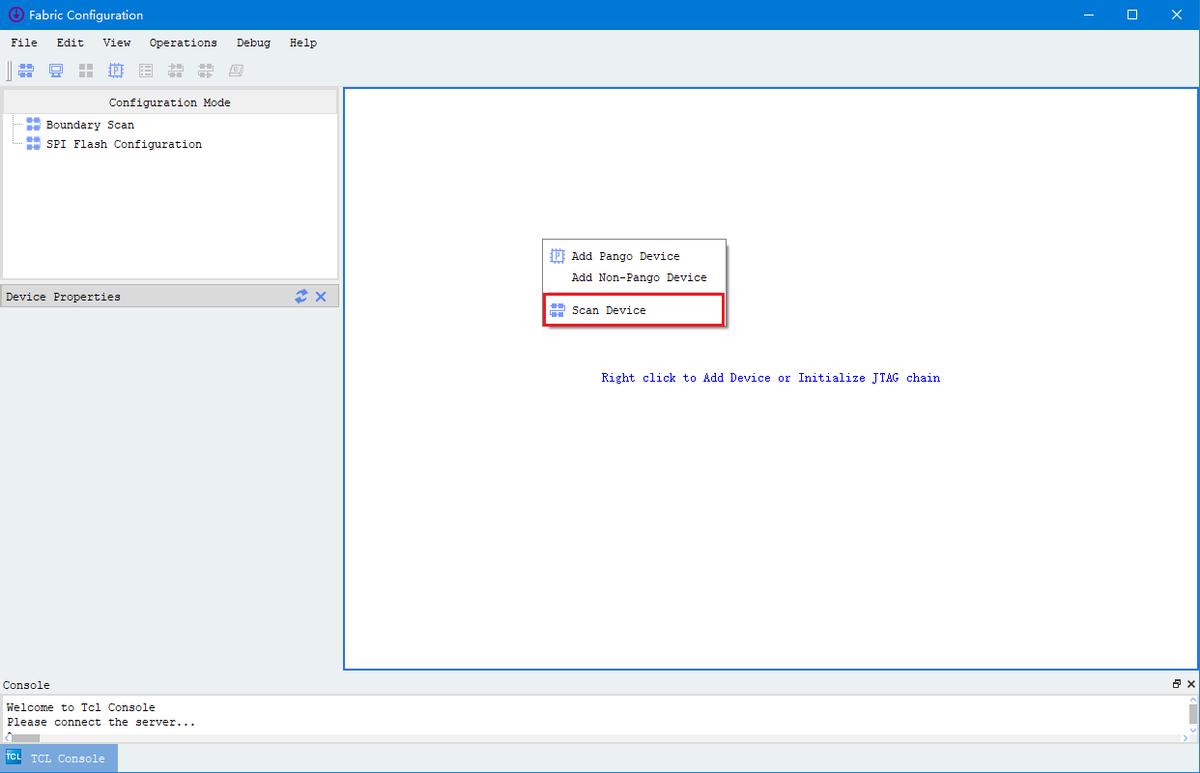

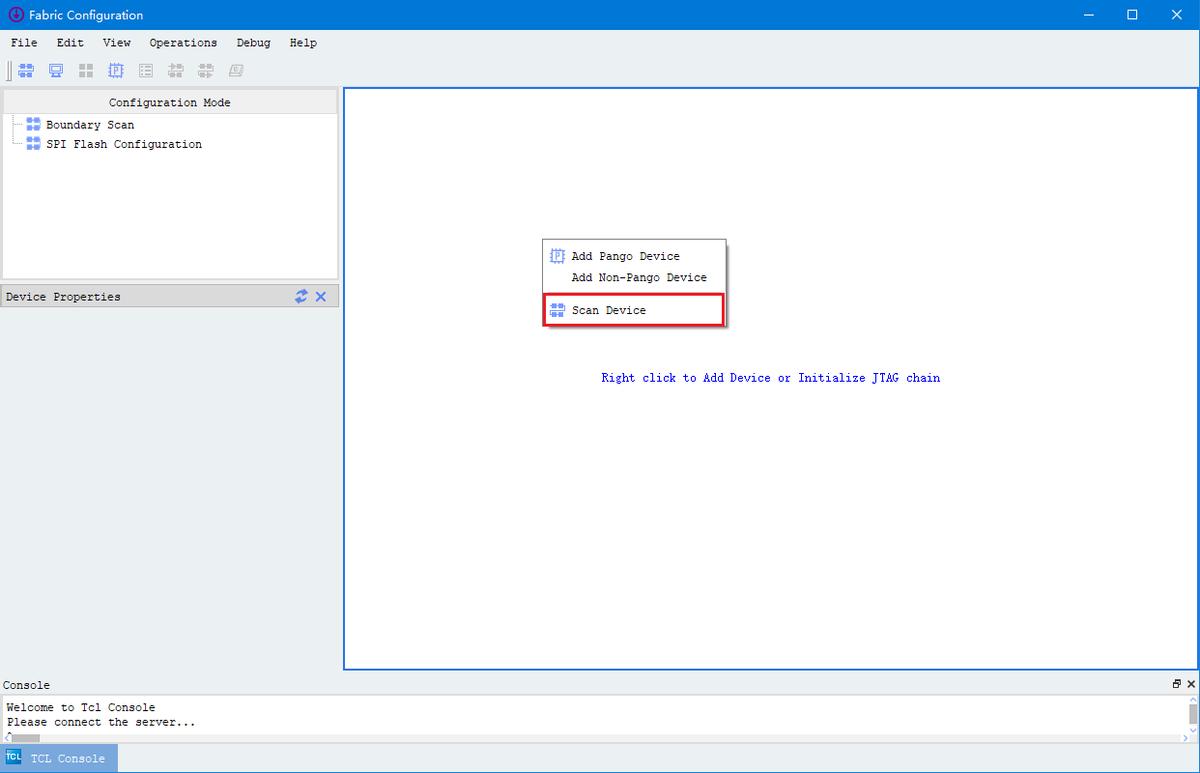

图 3将评估板上电,鼠标右键点击Fabric Configuration界面空白处,选择"Scan Device"选项,通过FPGA下载器扫描并连接FPGA设备。

图 4

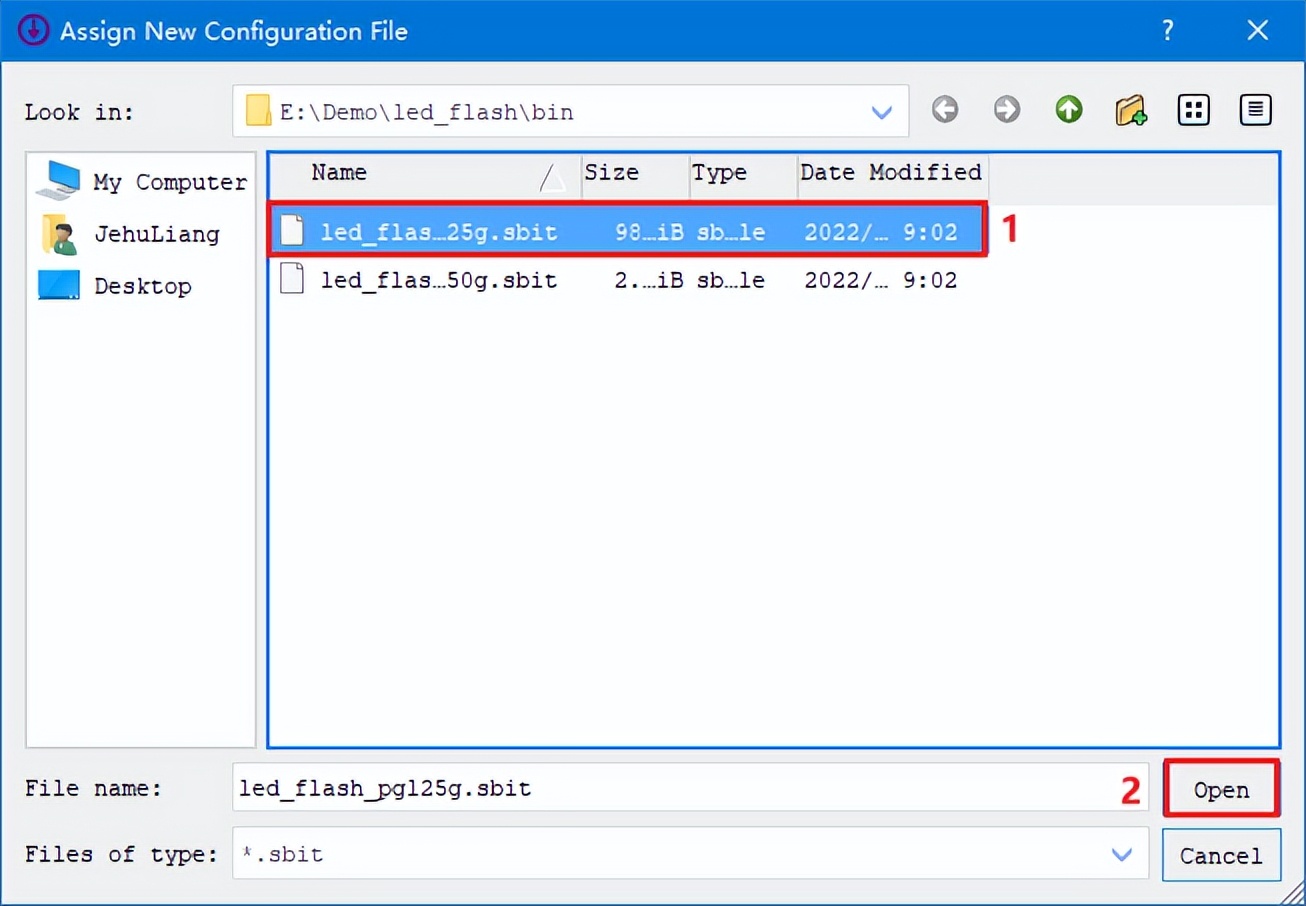

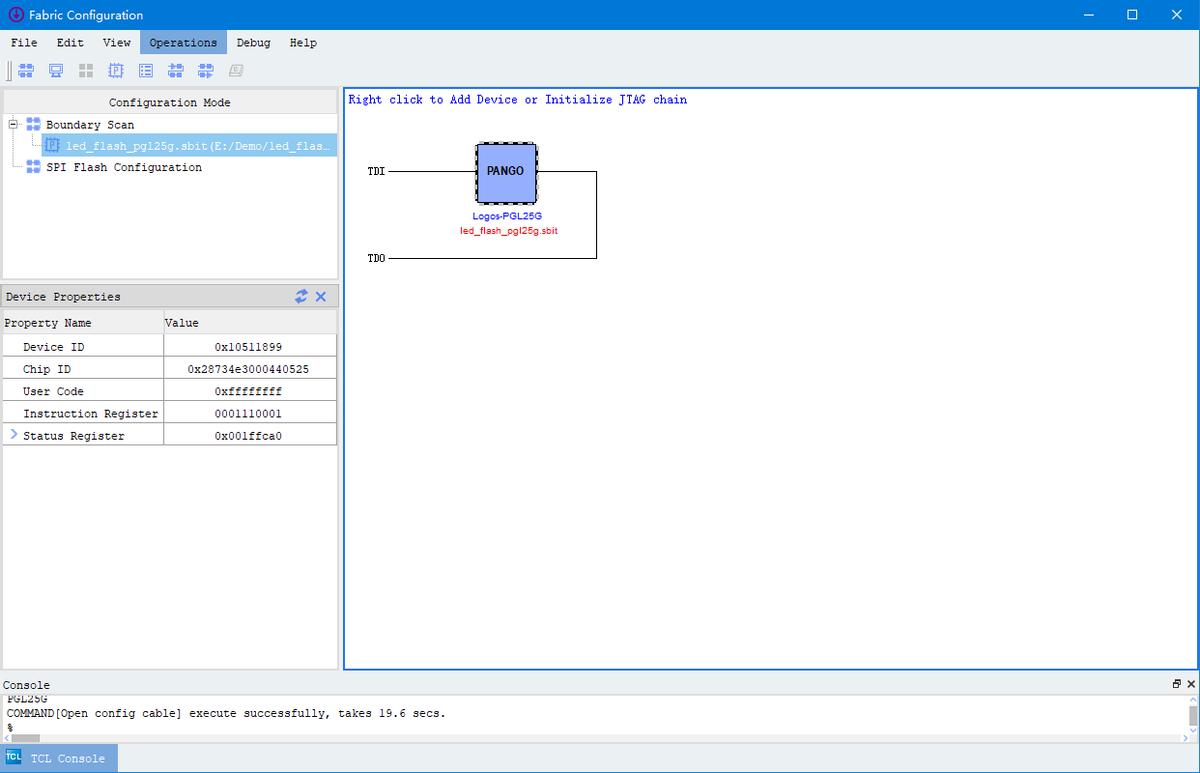

图 4连接成功后,将出现FPGA芯片图标,并自动弹出FPGA程序选择窗口,请选择对应的xxx.sbit文件进行加载。

图 5

图 5 图 6

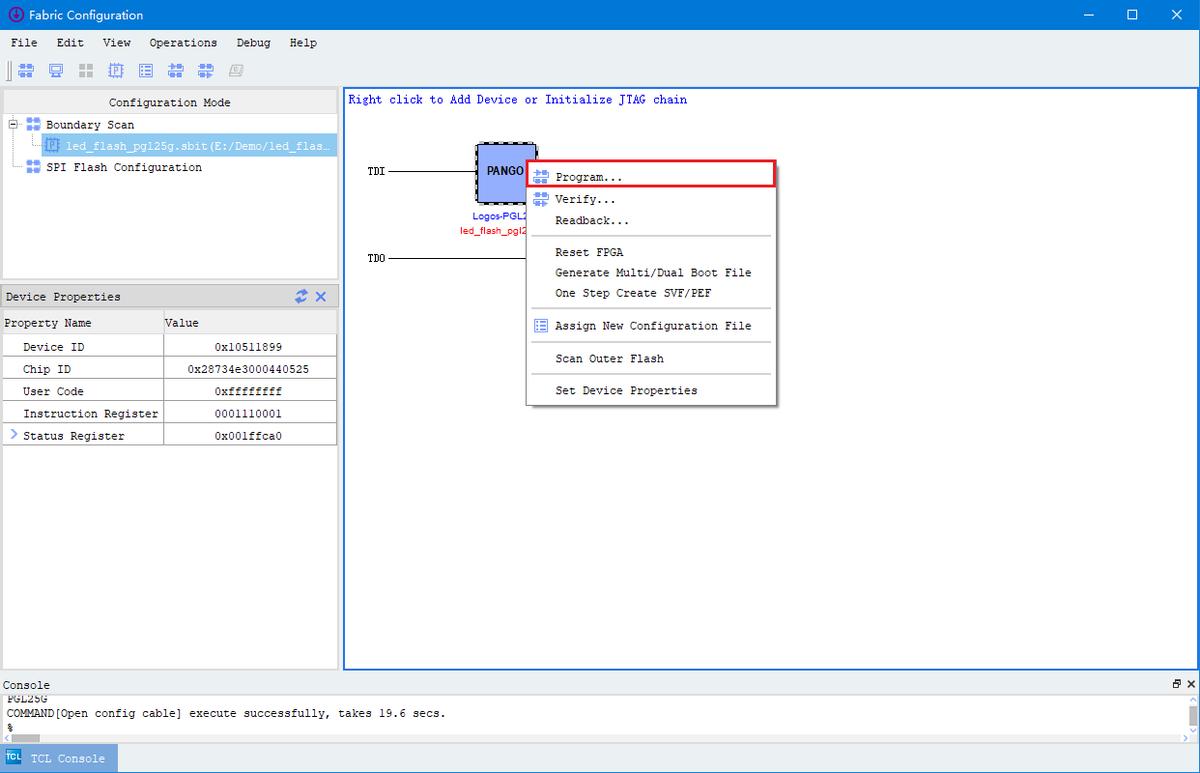

图 6鼠标右键点击FPGA芯片图标,选择"Program…",将目标程序加载至FPGA运行。

图 7

图 7 图 8

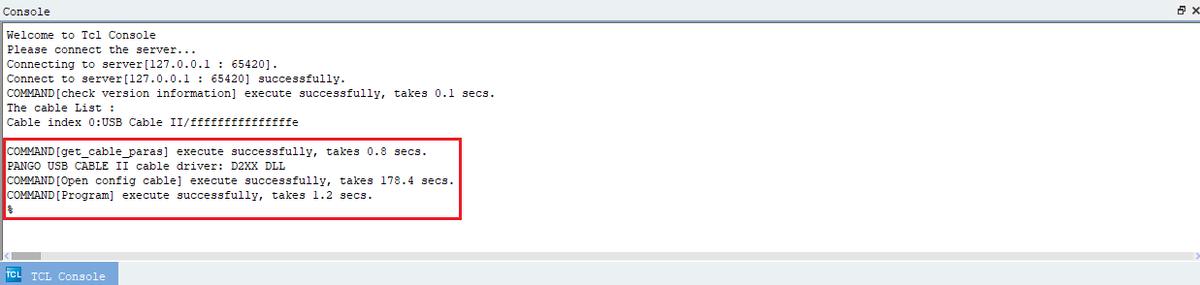

图 8程序成功加载后,Console控制台将会打印显示"COMMAND[Program] execute successfully"信息。同时可观察到评估底板LED按照一定的时间间隔循环亮灭,说明程序在线加载与运行正常。

图 9

图 9程序固化

本小节以led_flash案例为例,演示程序固化方法。

双击Pango Design Suite安装目录下"C:\pango\PDS_2021.1-SP7.1\bin\cdt_cfg.exe",打开Fabric Configuration界面。

图 10

图 10将评估板上电,鼠标右键点击Fabric Configuration界面空白处,选择"Scan Device"选项,通过FPGA下载器扫描并连接FPGA设备。

图 11

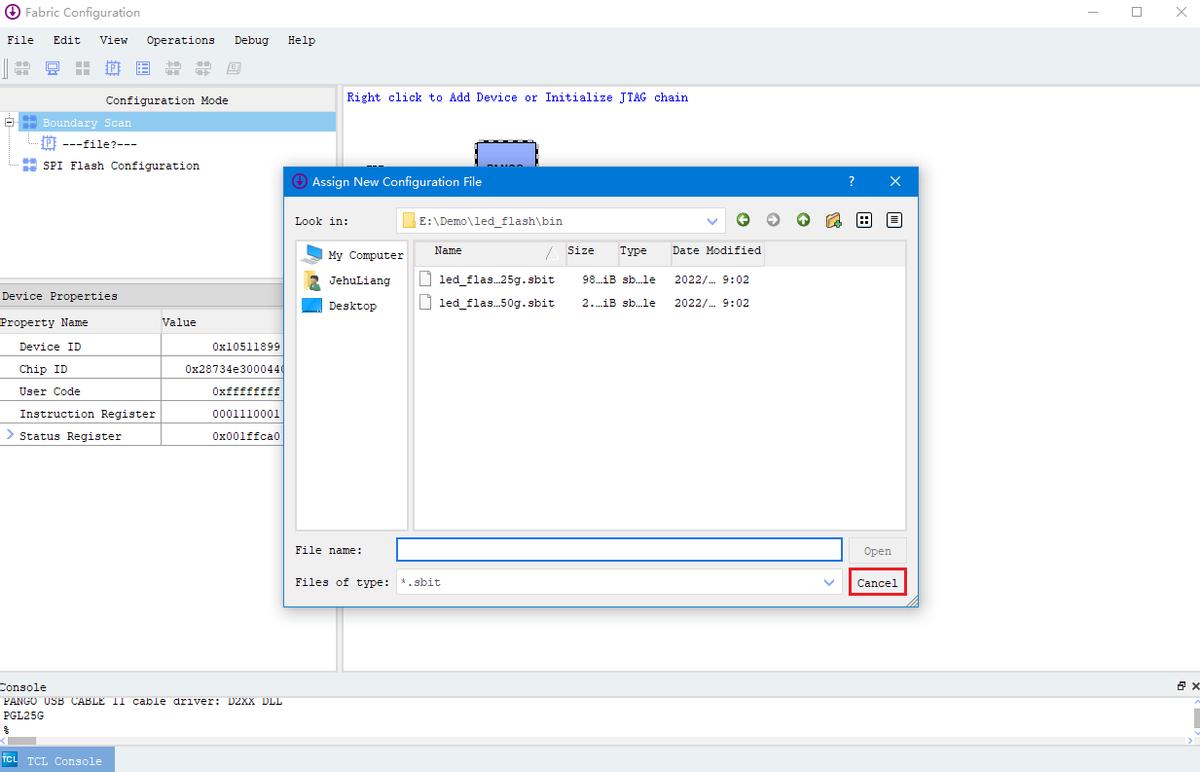

图 11连接成功后,将出现FPGA芯片图标,并自动弹出FPGA程序选择窗口,点击Cancel,不加载xxx.sbit文件。

图 12

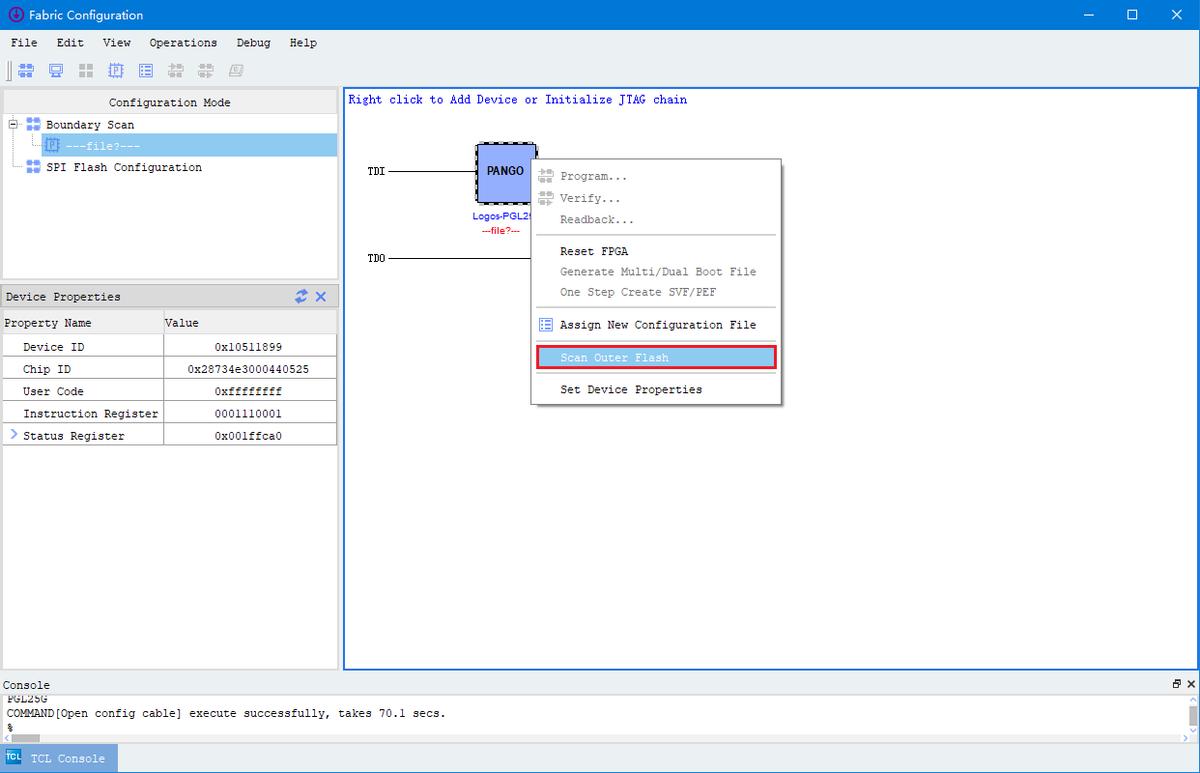

图 12鼠标右键点击FPGA芯片图标,选择"Scan Outer Flash"扫描并识别SPI FLASH芯片。

图 13

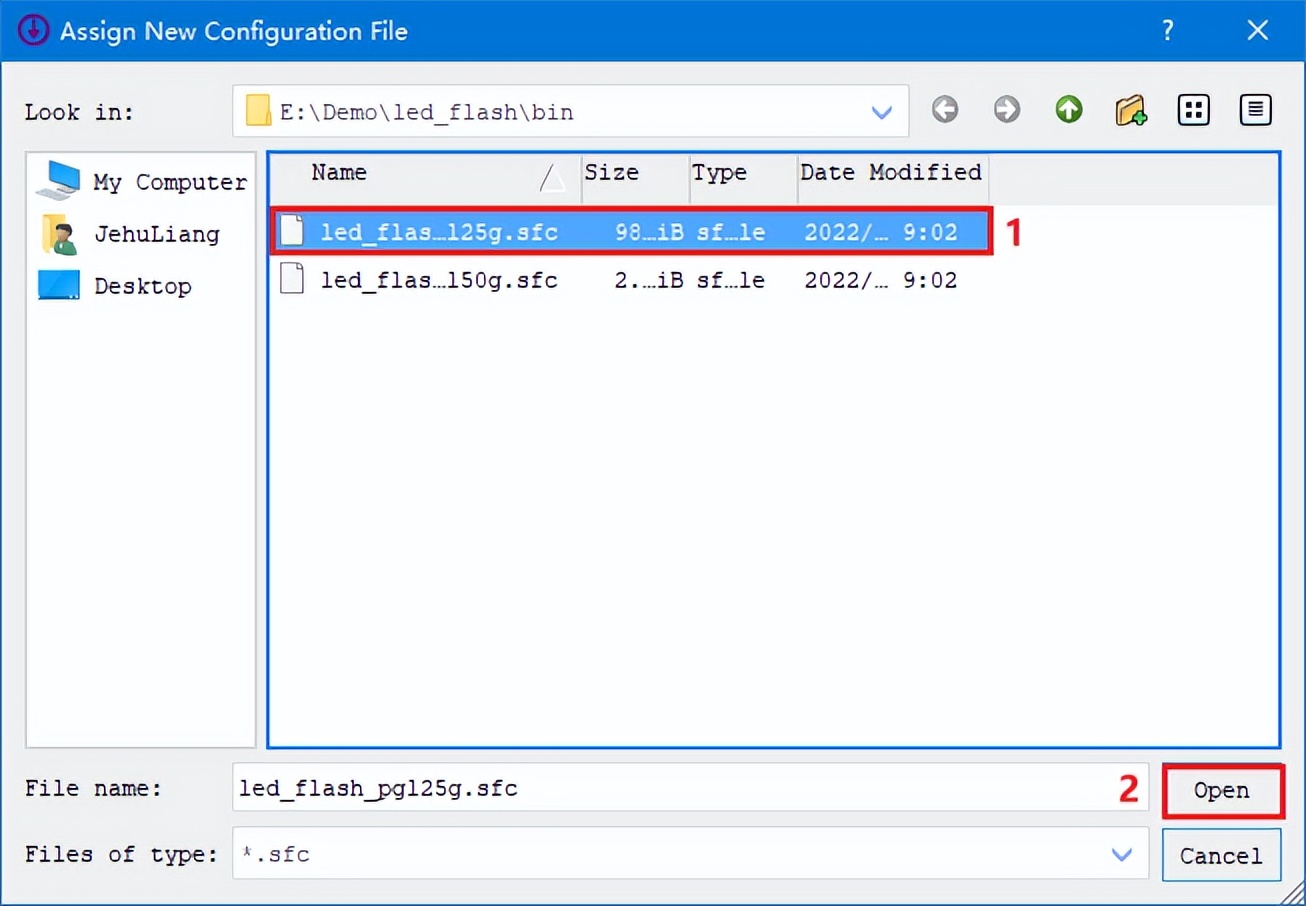

图 13扫描成功后,将自动弹出文件选择窗口,选择需固化的xxx.sfc文件。

图 14

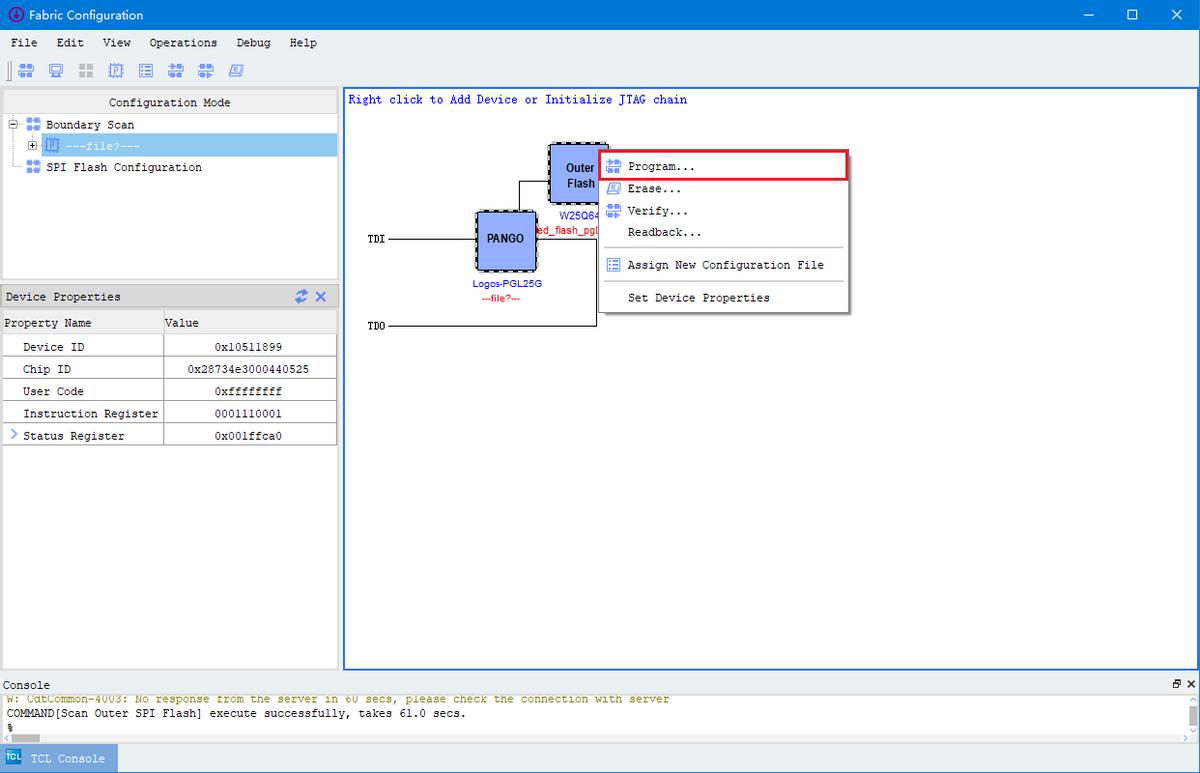

图 14鼠标右键点击"Outer Flash"芯片图标,选择"Program…"进行程序固化。

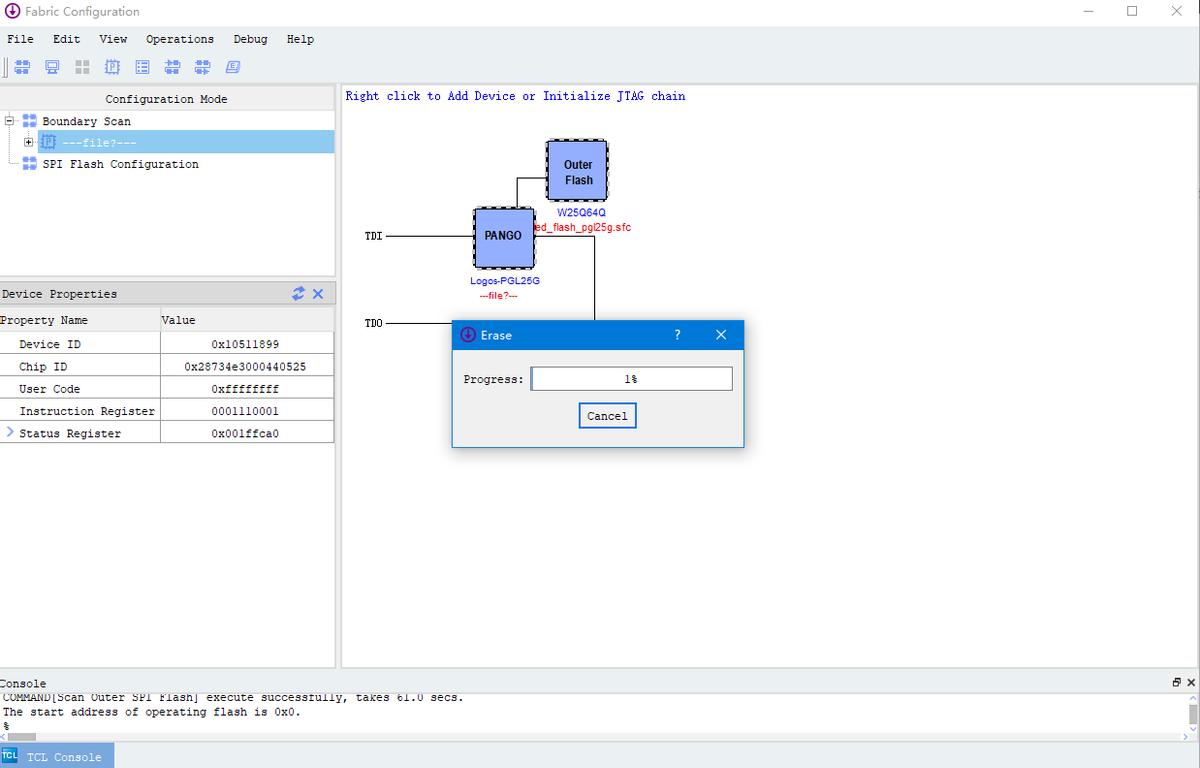

图 15

图 15 图 16

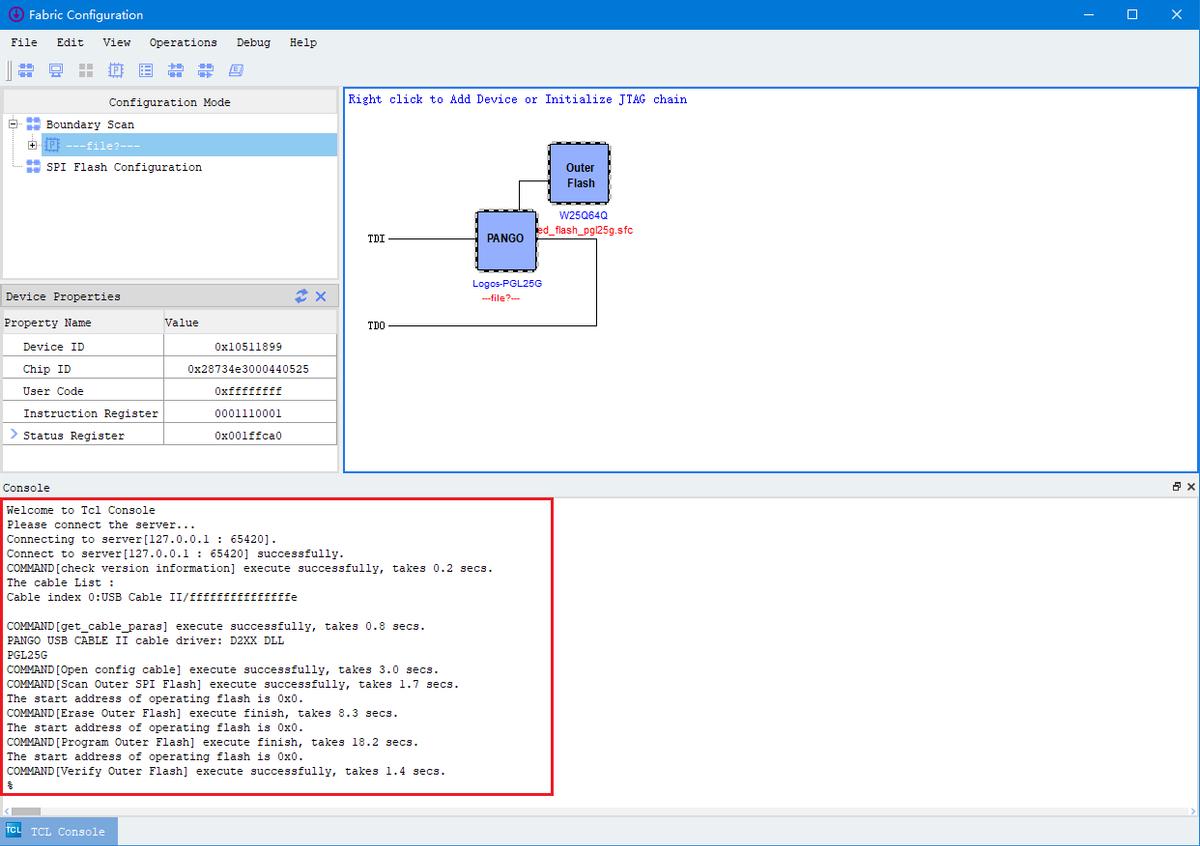

图 16程序固化完成后,Console控制台将会打印显示如下信息。

图 17

图 17将评估板断开FPGA下载器并重新上电,即可观察到评估底板LED按照一定的时间间隔循环亮灭,说明程序固化成功、运行正常。

工程导入与程序编译

如需导入工程以及重新编译程序,请按如下步骤进行操作。如无需导入工程或重新编译程序,请忽略本章节内容。

本小节以led_flash案例为例,演示基于Pango Design Suite导入、编译FPGA工程的步骤。

工程导入

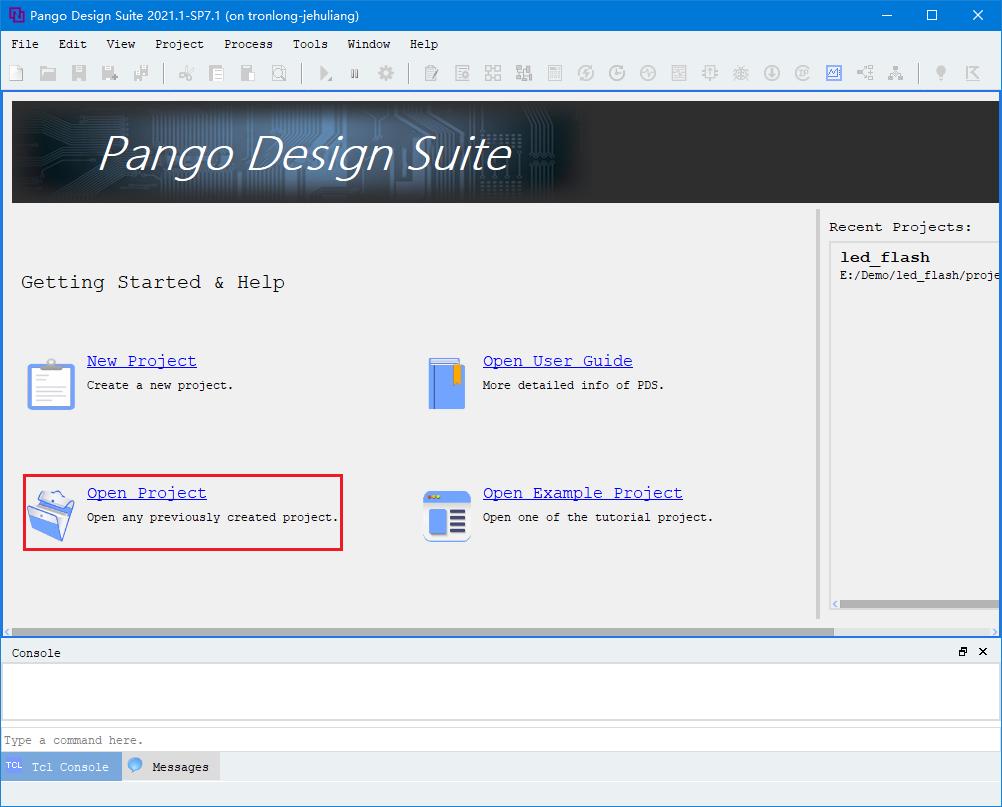

- 请双击桌面Pango Design Suite图标,打开软件。

图 18

图 18在弹出的界面中点击"Open Project"。

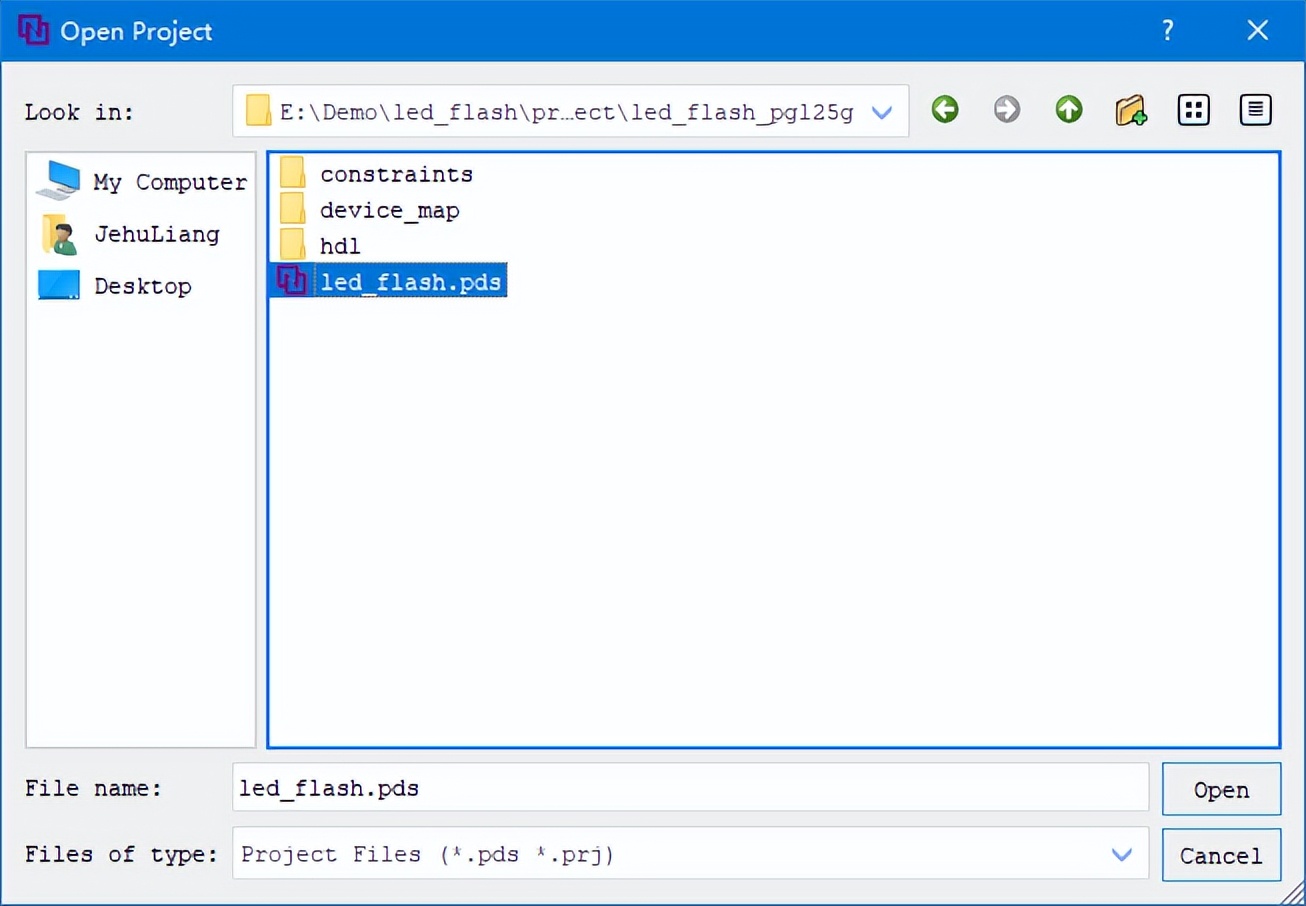

图 19

图 19在弹出的界面中选择FPGA案例"project\led_flash_xxx\目录下的xxx.pds文件,并点击Open打开。

图 20

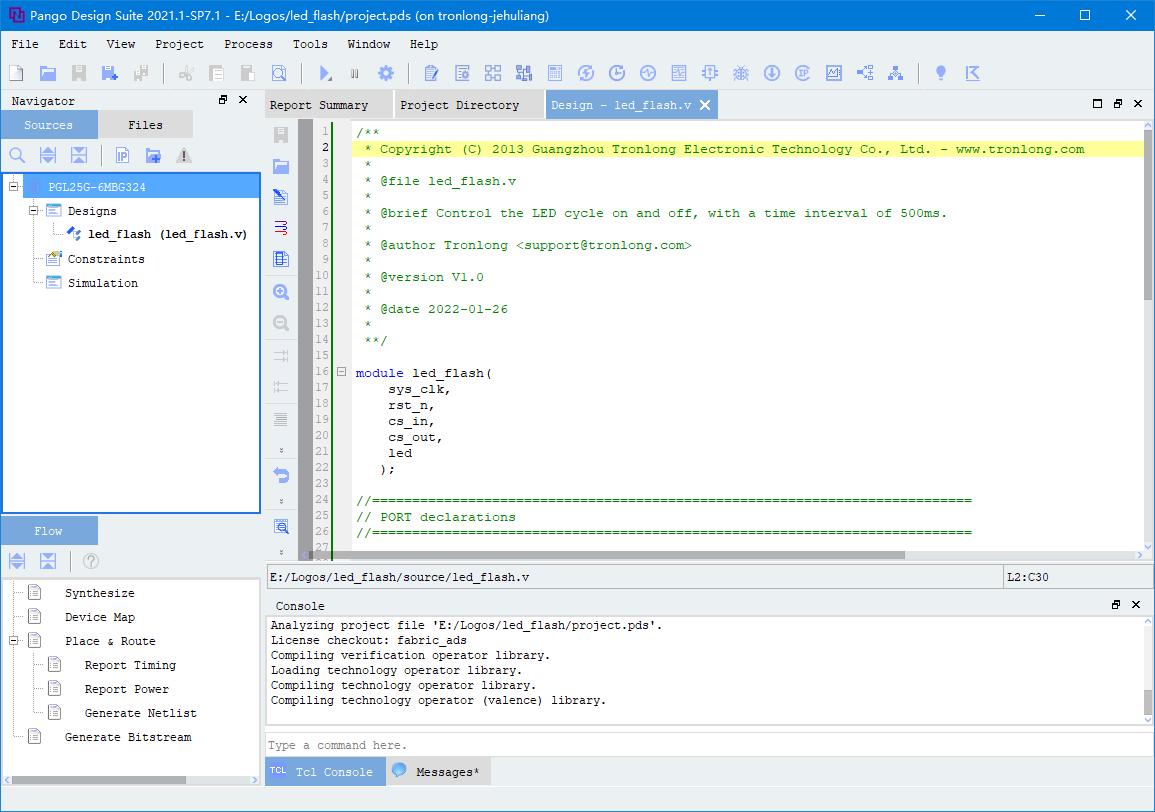

图 20弹出如下界面,工程导入完成。

图 21

图 21工程新建、移植

本小节主要说明工程新建以及对现有工程进行移植的简要步骤。若无需新建工程或对现有工程进行移植,请跳过本小节内容。

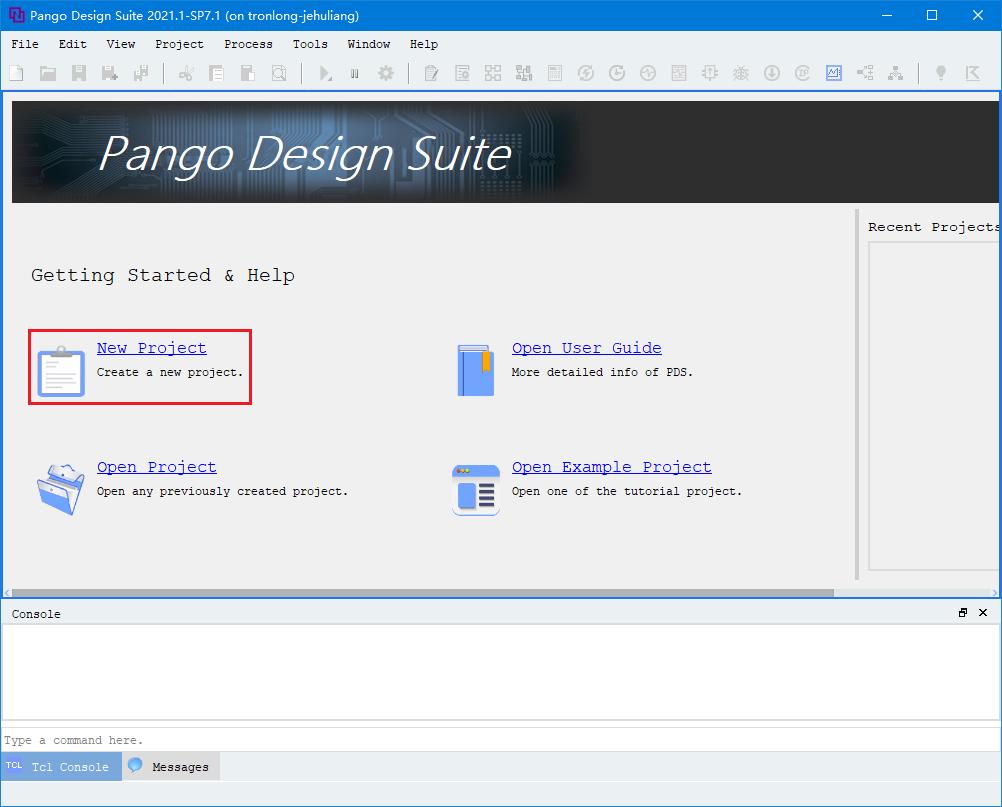

- 双击打开Pango Design Suite,在弹出的界面中点击"New Project"。

图 22

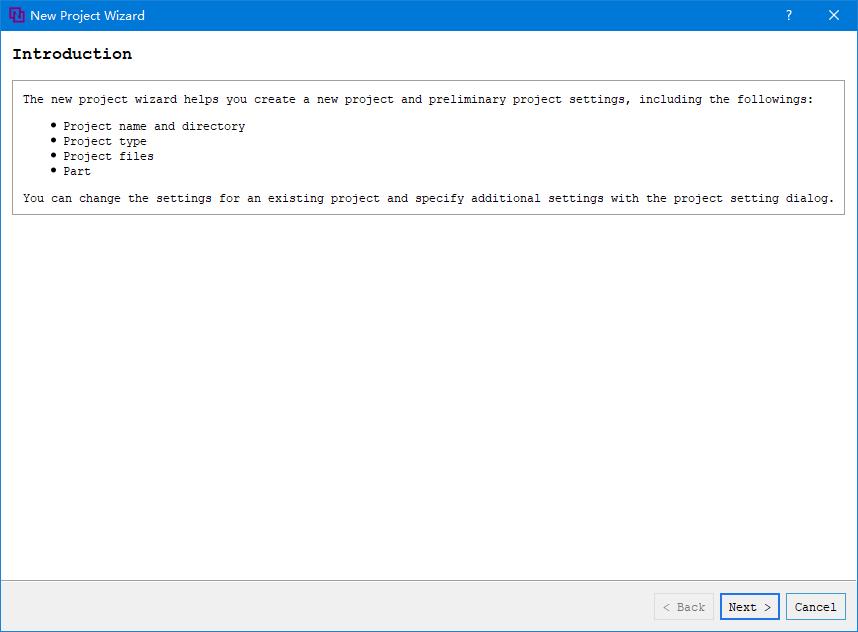

图 22- 在弹出的界面中,点击Next,跳转到下一个界面。

图 23

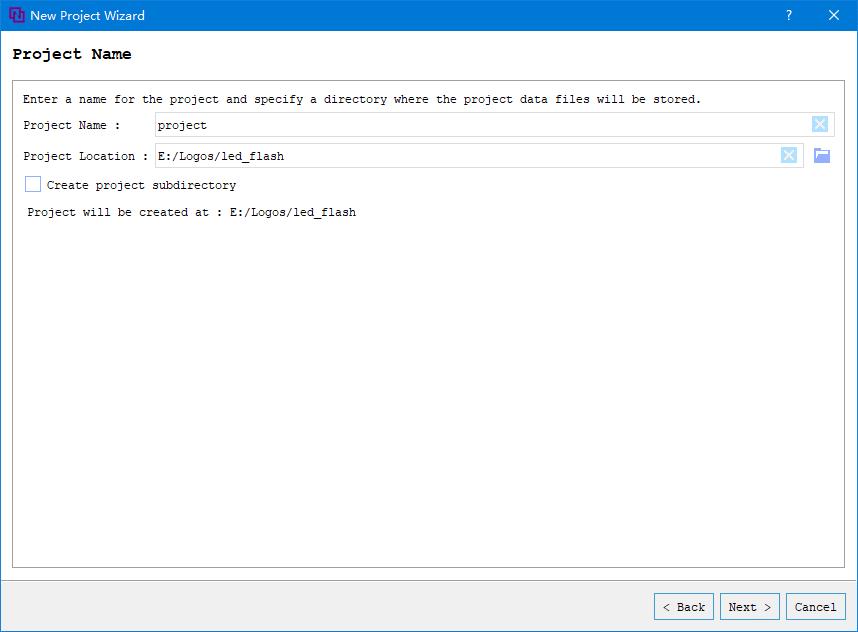

图 23- 输入工程名字,根据实际情况修改文件保存路径,并点击Next。

图 24

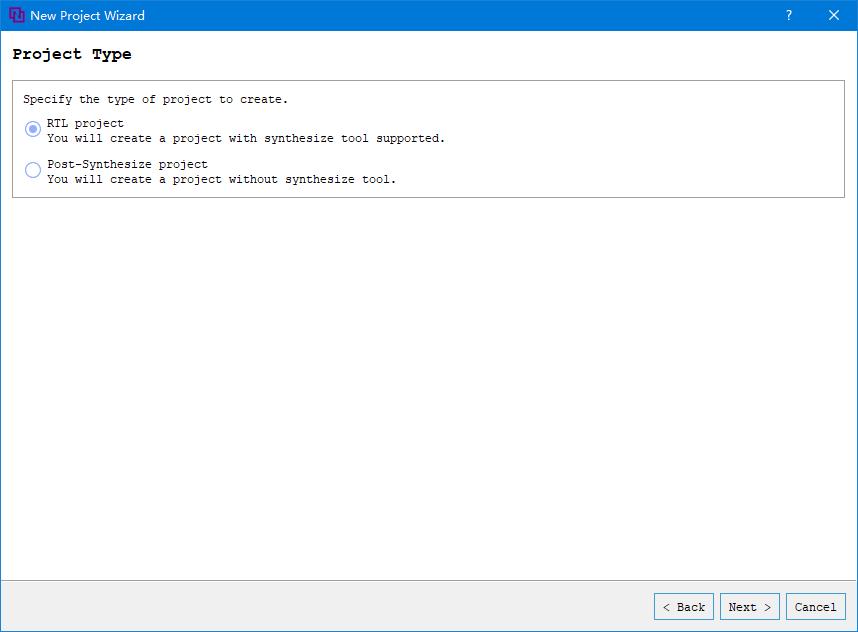

图 24- 在弹出的界面中勾选"RTL project",并点击Next。

图 25

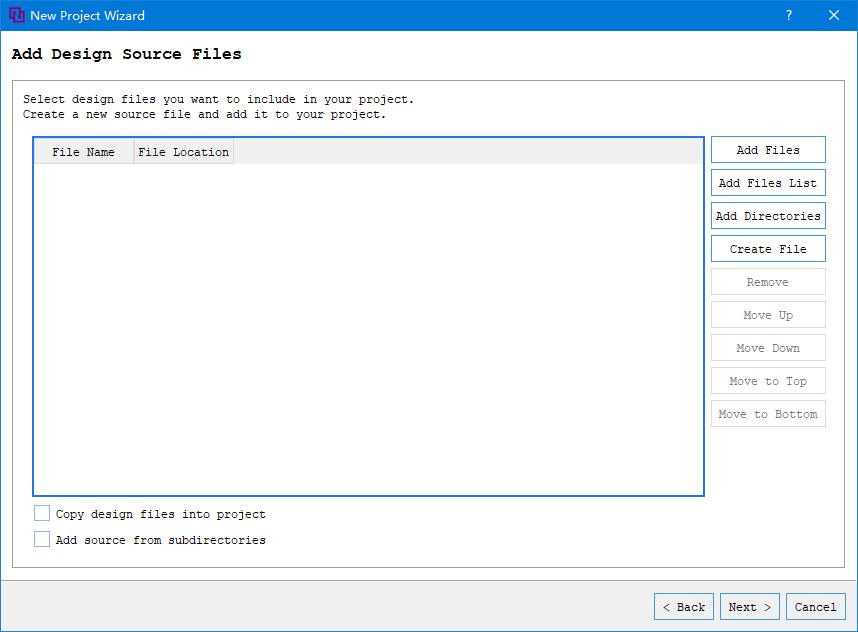

图 25- 弹出如下Add Design Source Files界面,直接点击Next跳过。

图 26

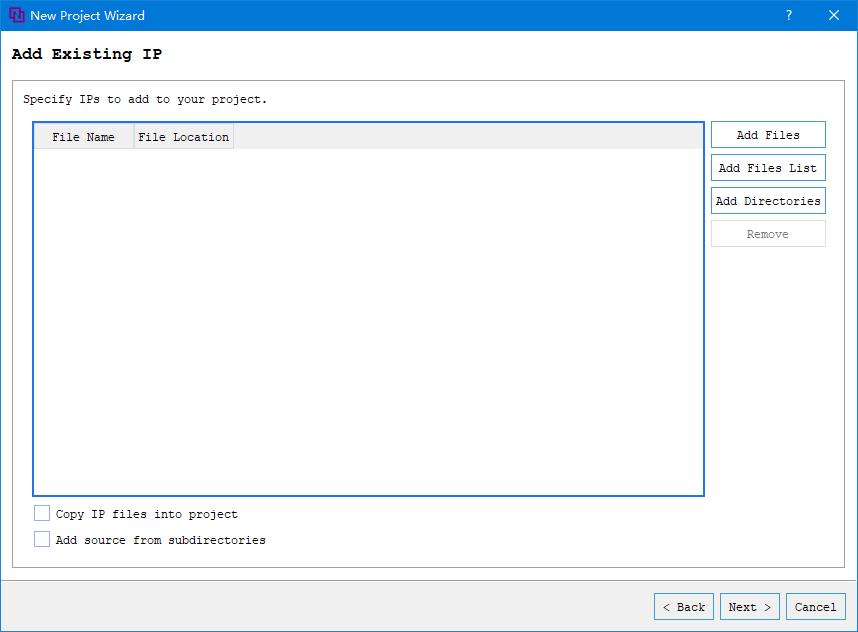

图 26- 弹出如下Add Existing IP界面,直接点击Next跳过。

图 27

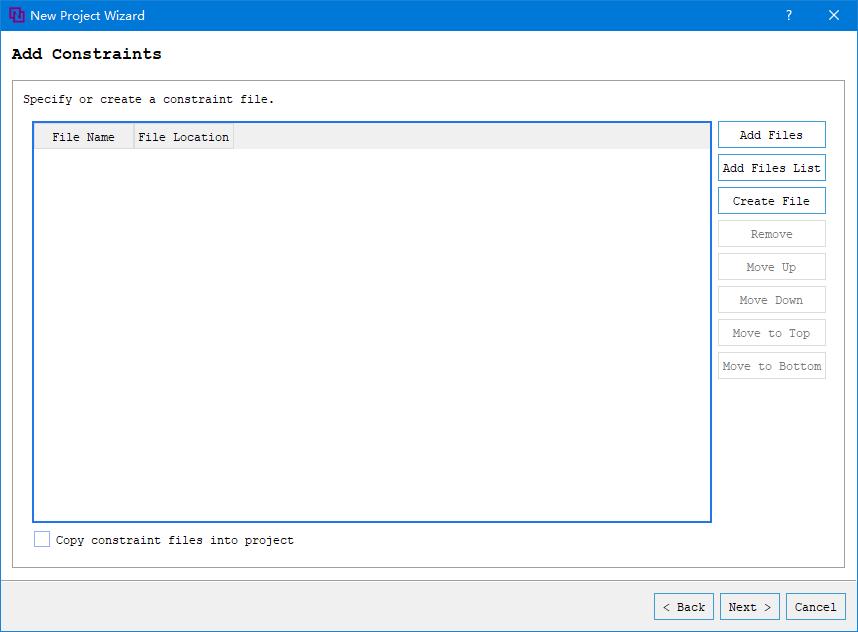

图 27弹出如下Add Constraints界面,直接点击Next跳过。

图 28

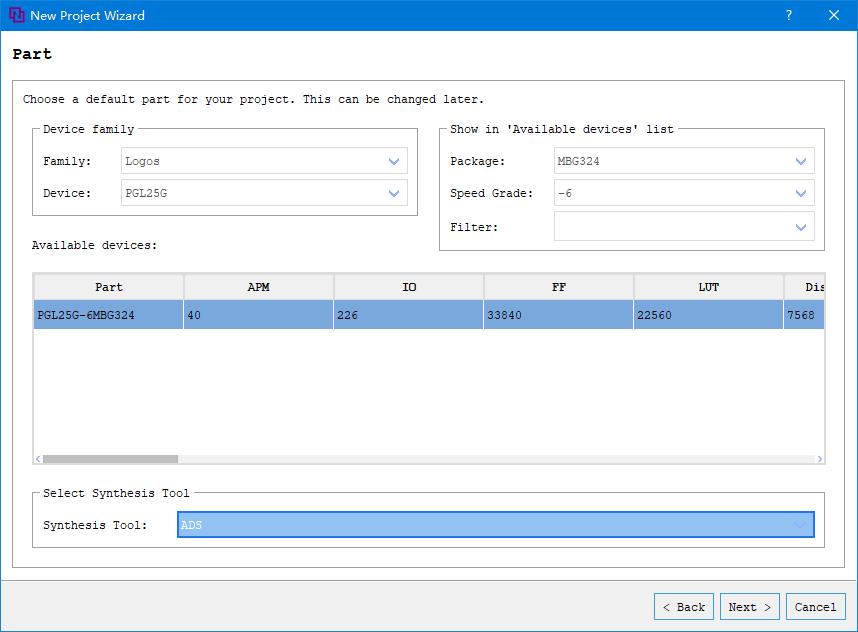

图 28在弹出的工程配置界面中设置FPGA芯片参数。Family:Logos,Device:PGL25G,Package:MBG324,Speed:-6,Synthesis Tool:ADS,设置完成后,请点击Next。

图 29

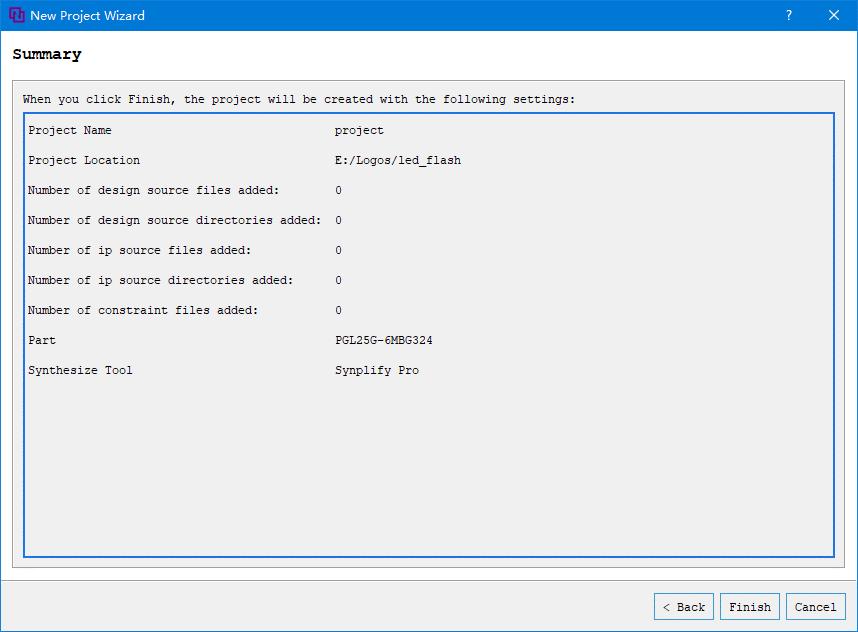

图 29在弹出的界面,点击Finish,即可完成工程新建。

图 30

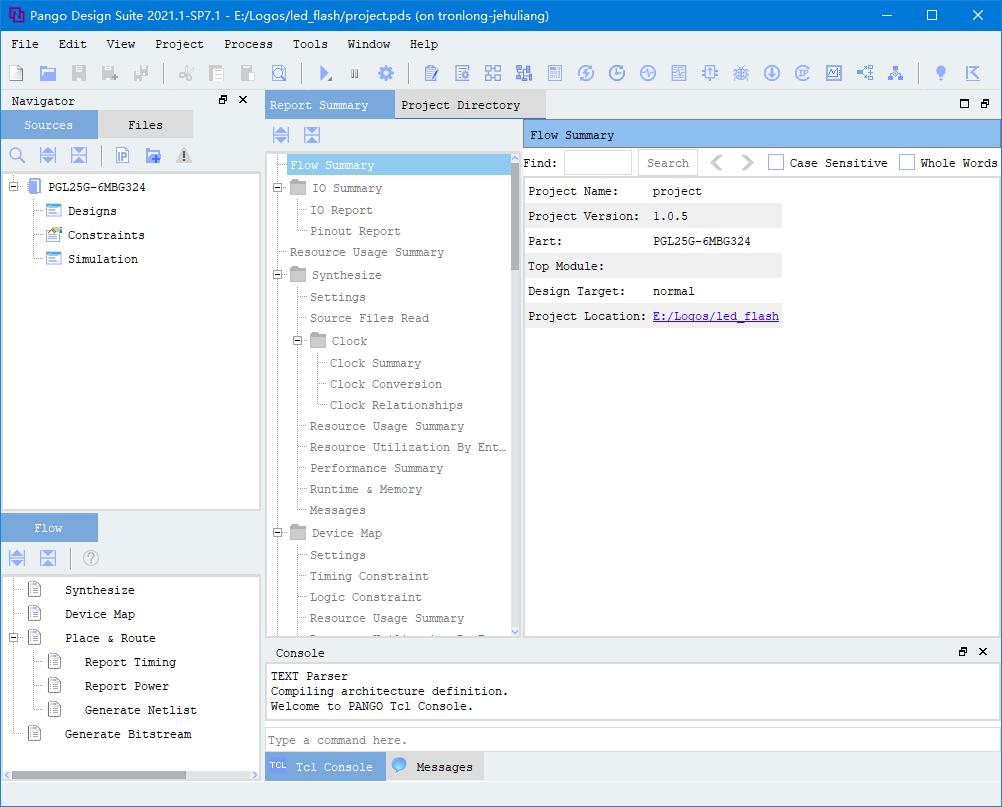

图 30 图 31

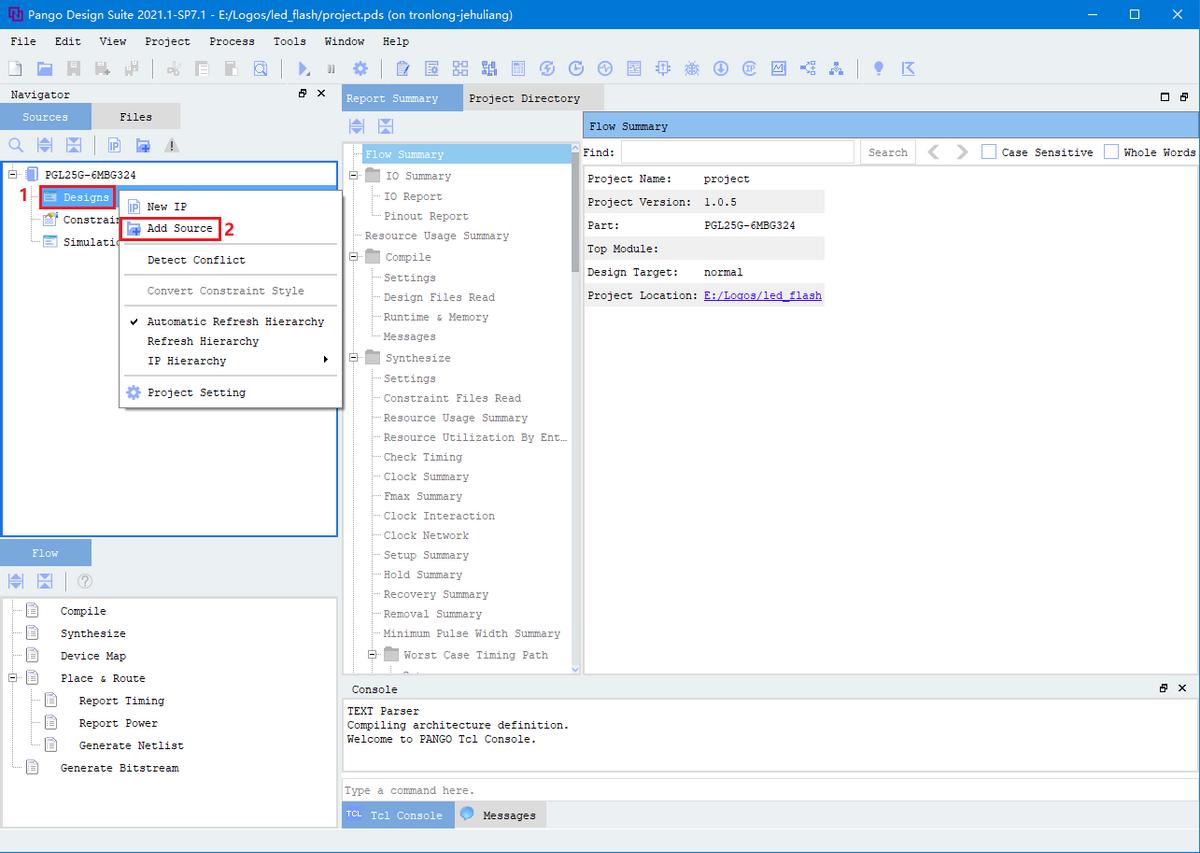

图 31在工程界面,右击工程Designs,点击"Add Source"新建模块文件。

图 32

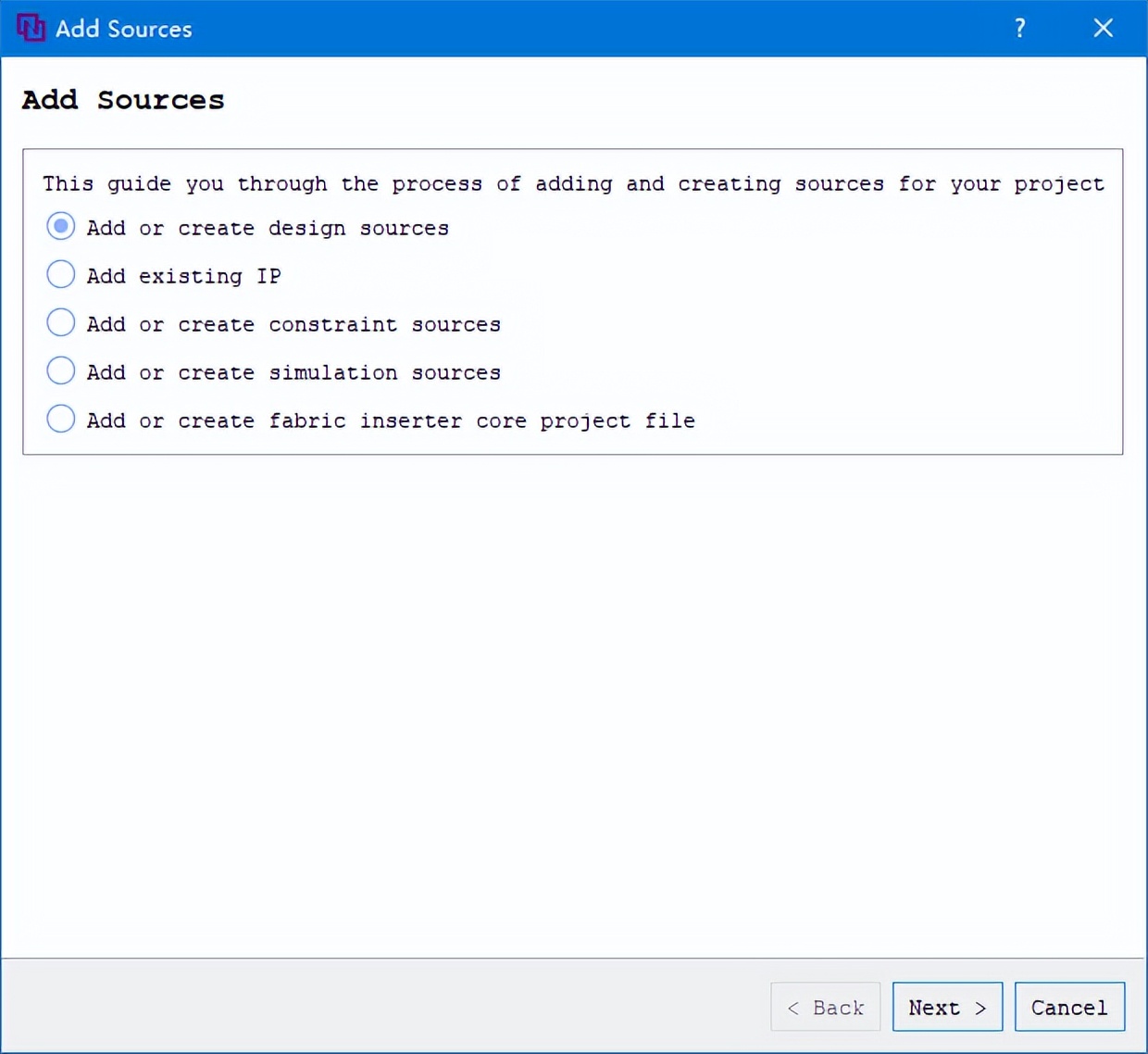

图 32在弹出如下界面,选择"Add or create design sources",并点击Next。

图 33

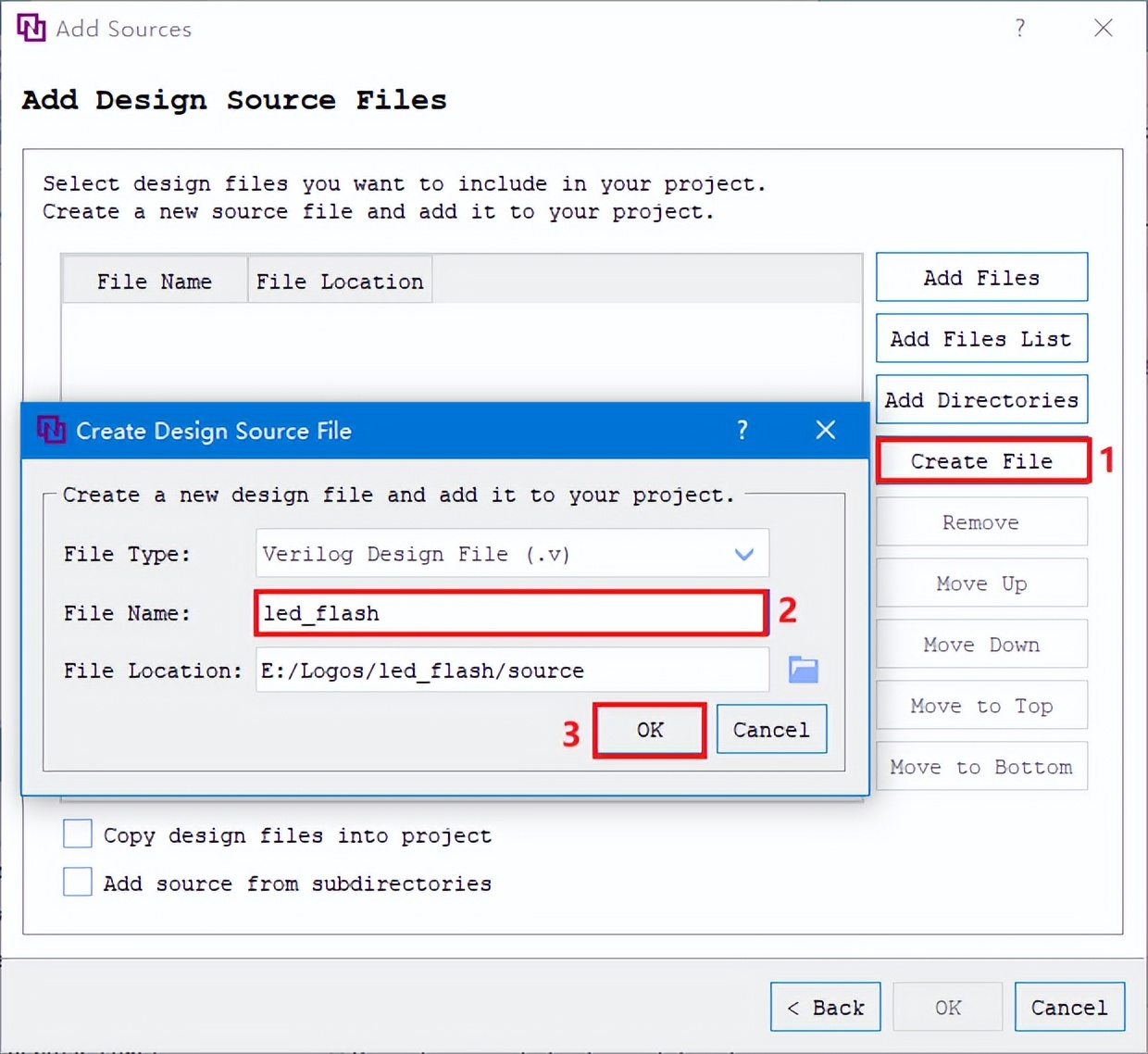

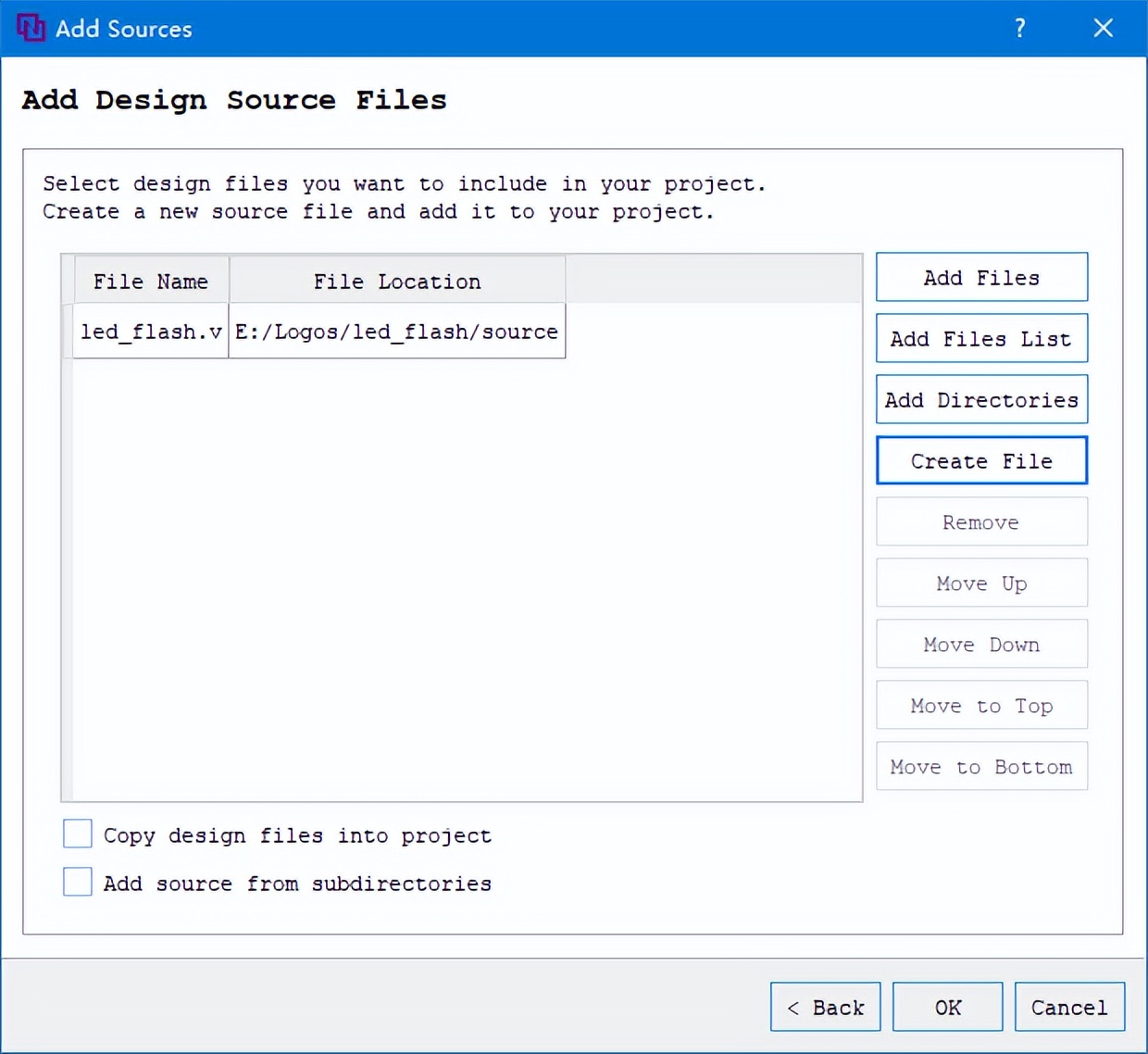

图 33在弹出的界面中,点击"Create File"选项,输入新建的模块文件名称,依次点击OK。

图 34

图 34 图 35

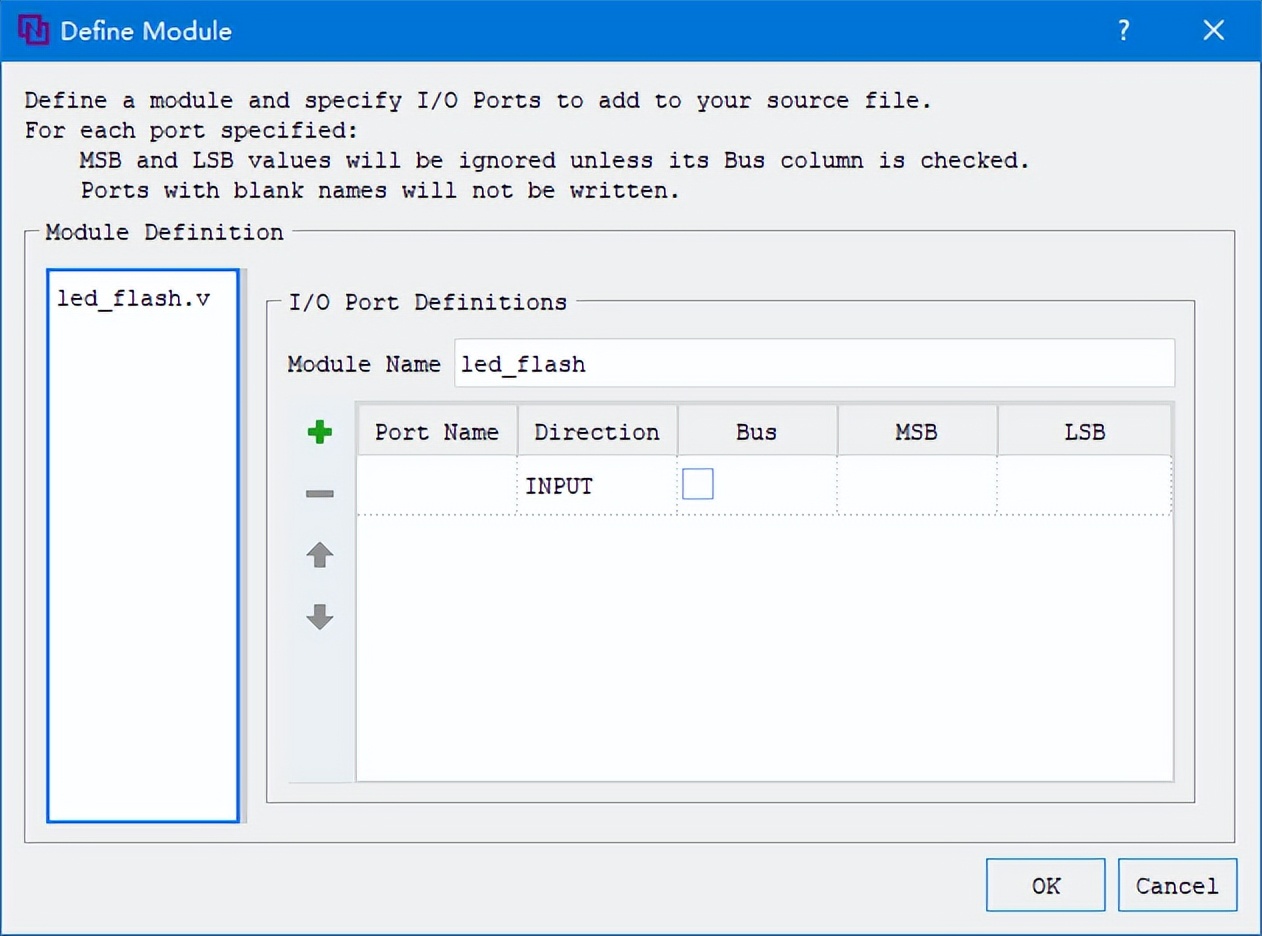

图 35在弹出的界面,可直接通过图形界面配置引脚约束。由于本次演示通过新建约束文件进行引脚约束,请直接点击OK跳过。

图 36

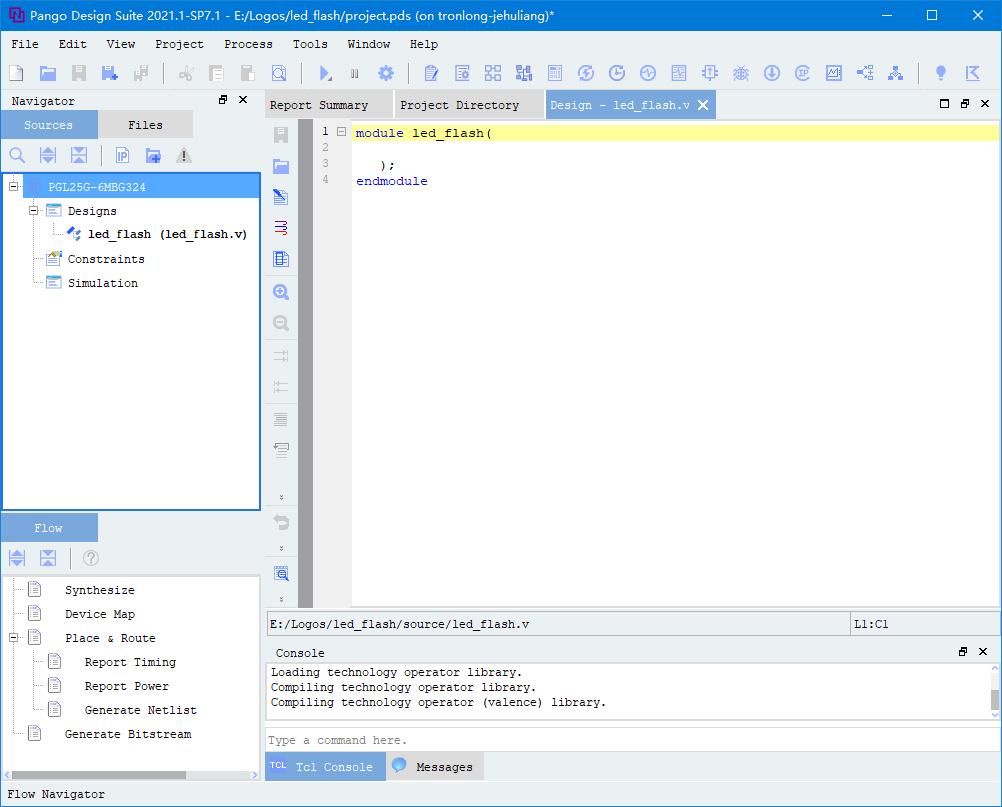

图 36完成模块文件新建后,此时将在工程界面右侧出现程序编辑窗口。

图 37

图 37打开案例"project\led_flash_xxx\hdl\led_test.v"文件,将所有代码拷贝至程序编辑界面或自行编写,并点击保存编辑。完成保存后,Console窗口无Errors和Warning则说明程序语法无错误。

图 38

图 38 图 39

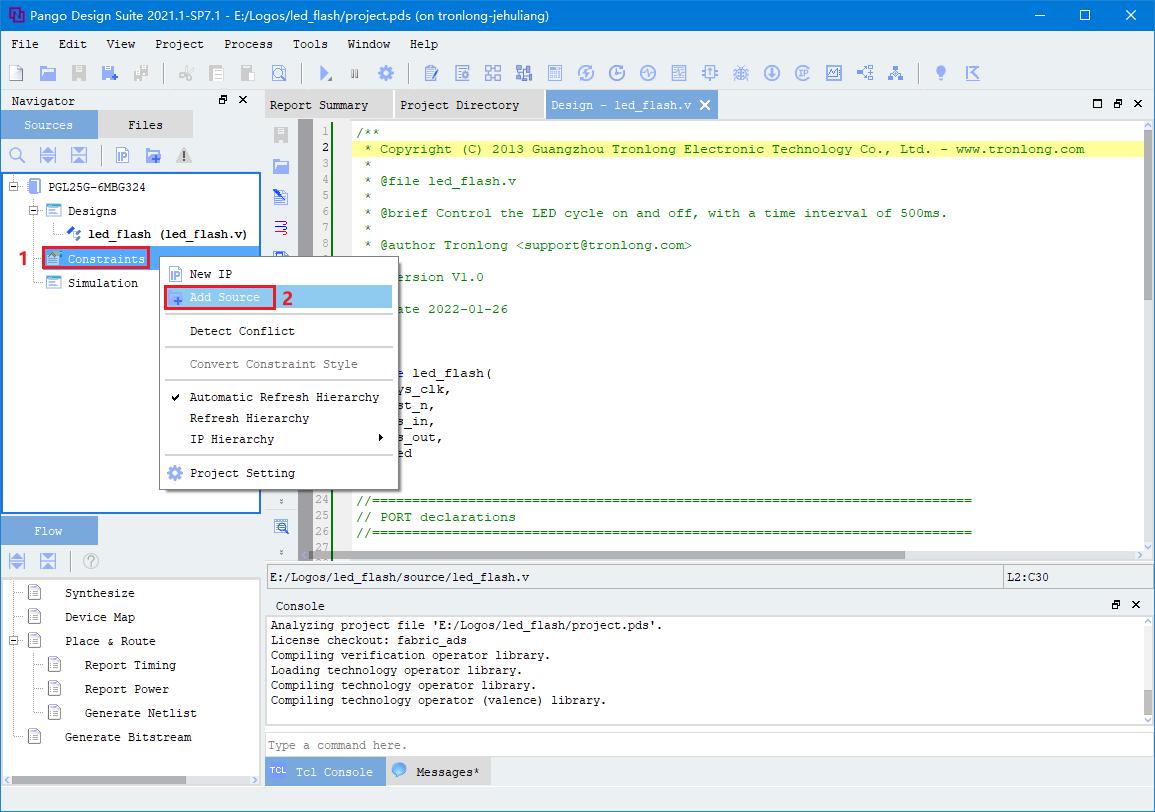

图 39在工程界面,右击"Constraints -> Add Source"进行引脚约束。

图 40

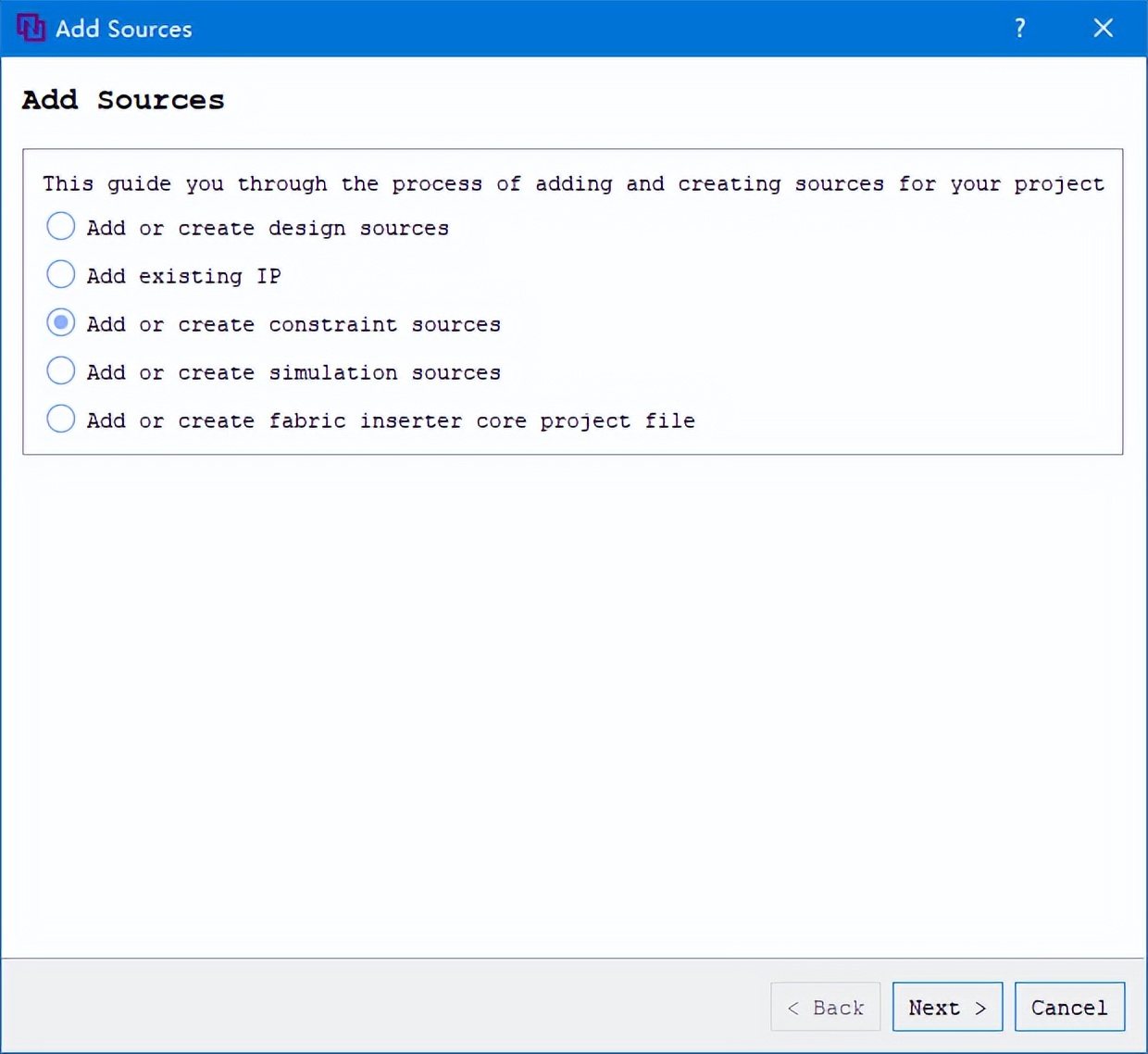

图 40在弹出界面,选择"Add or create constraint sources",并点击Next。

图 41

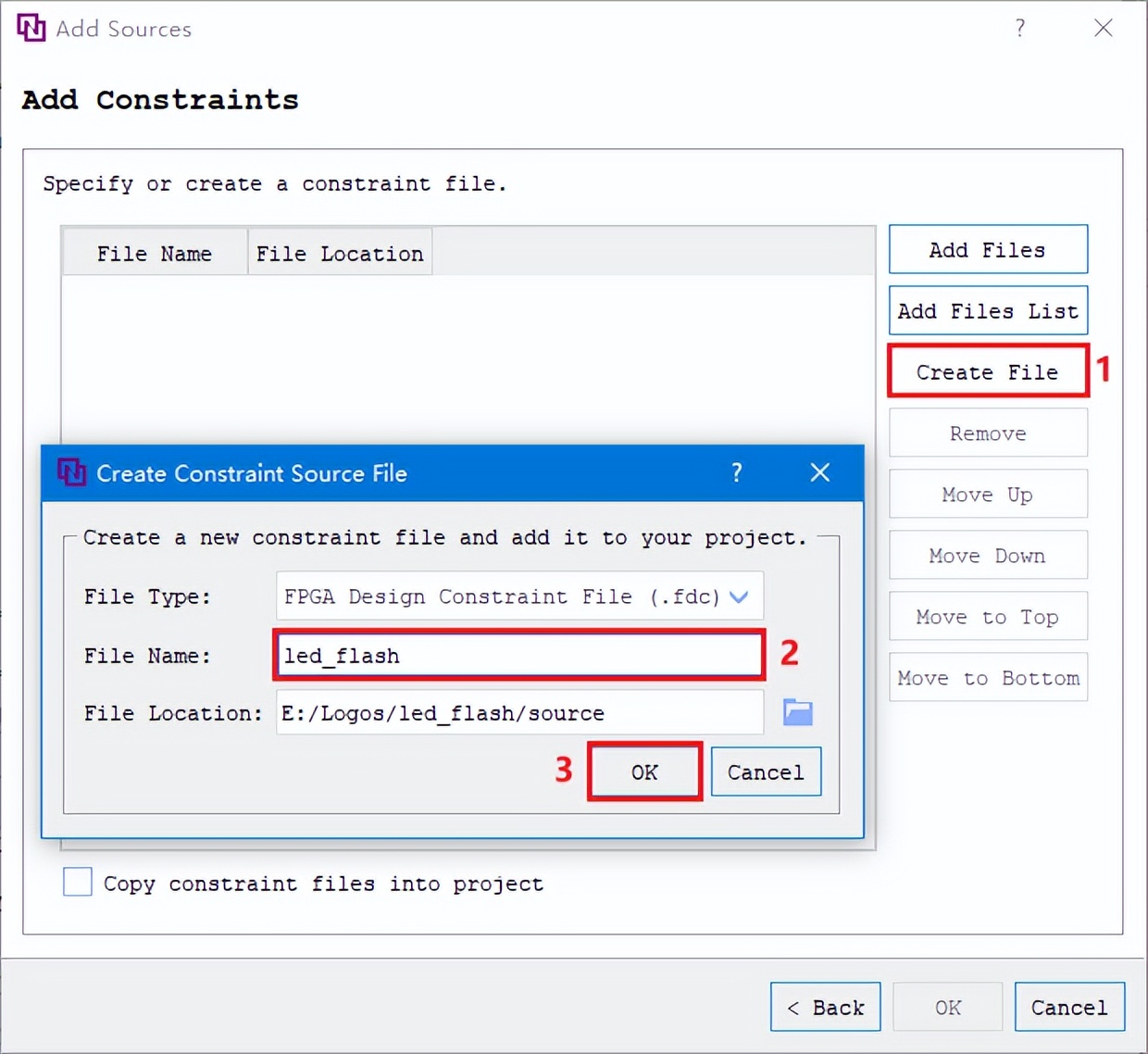

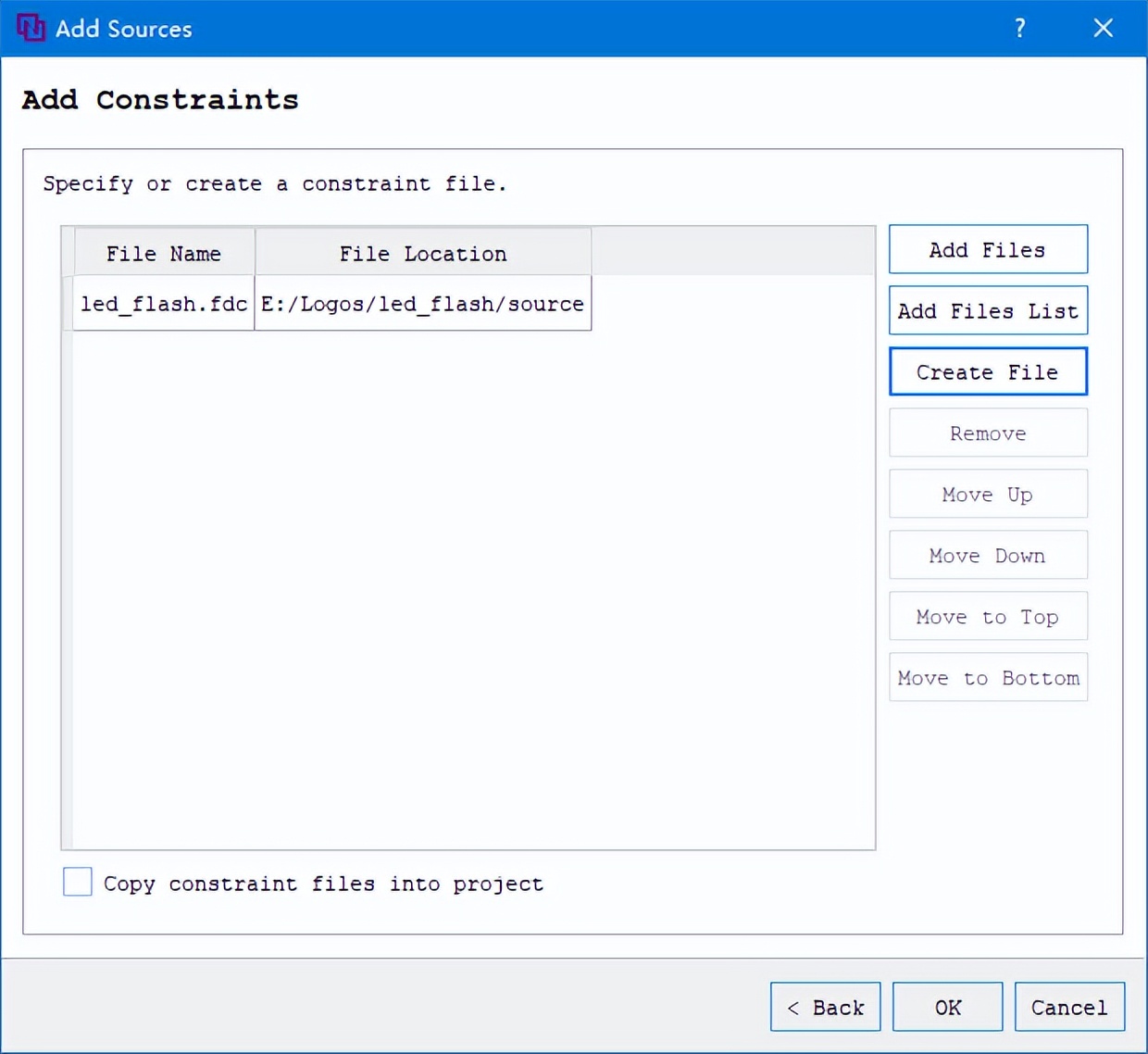

图 41在弹出的界面中,点击"Create File"选项,输入新建引脚约束文件名称,依次点击OK。

图 42

图 42 图 43

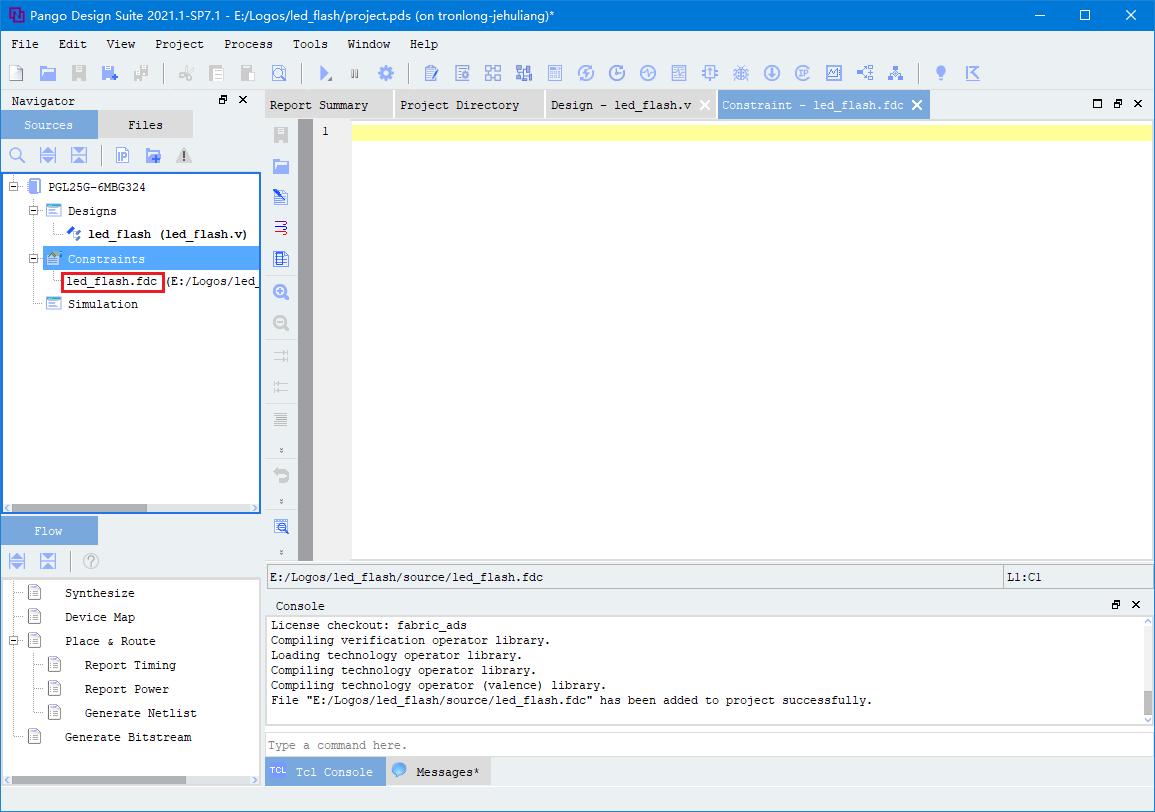

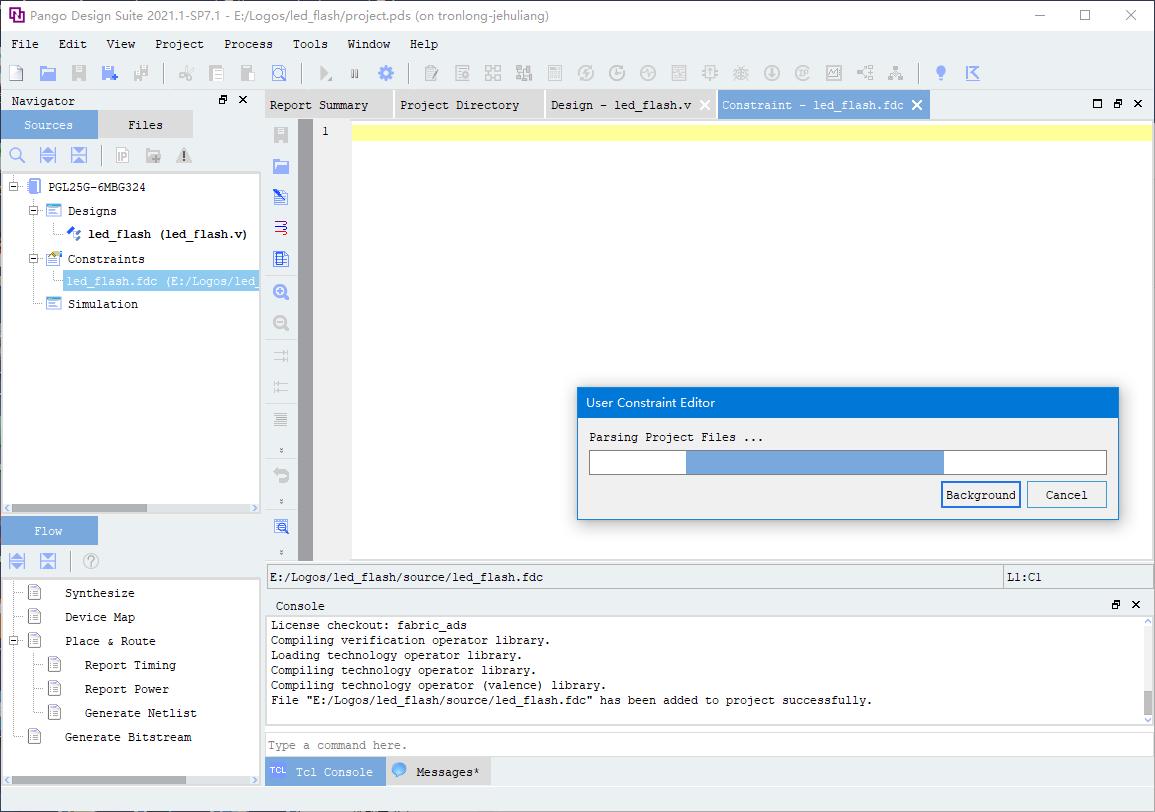

图 43引脚约束文件新建完成后,双击打开工程界面的xxx.fdc文件,如下图所示。

图 44

图 44 图 45

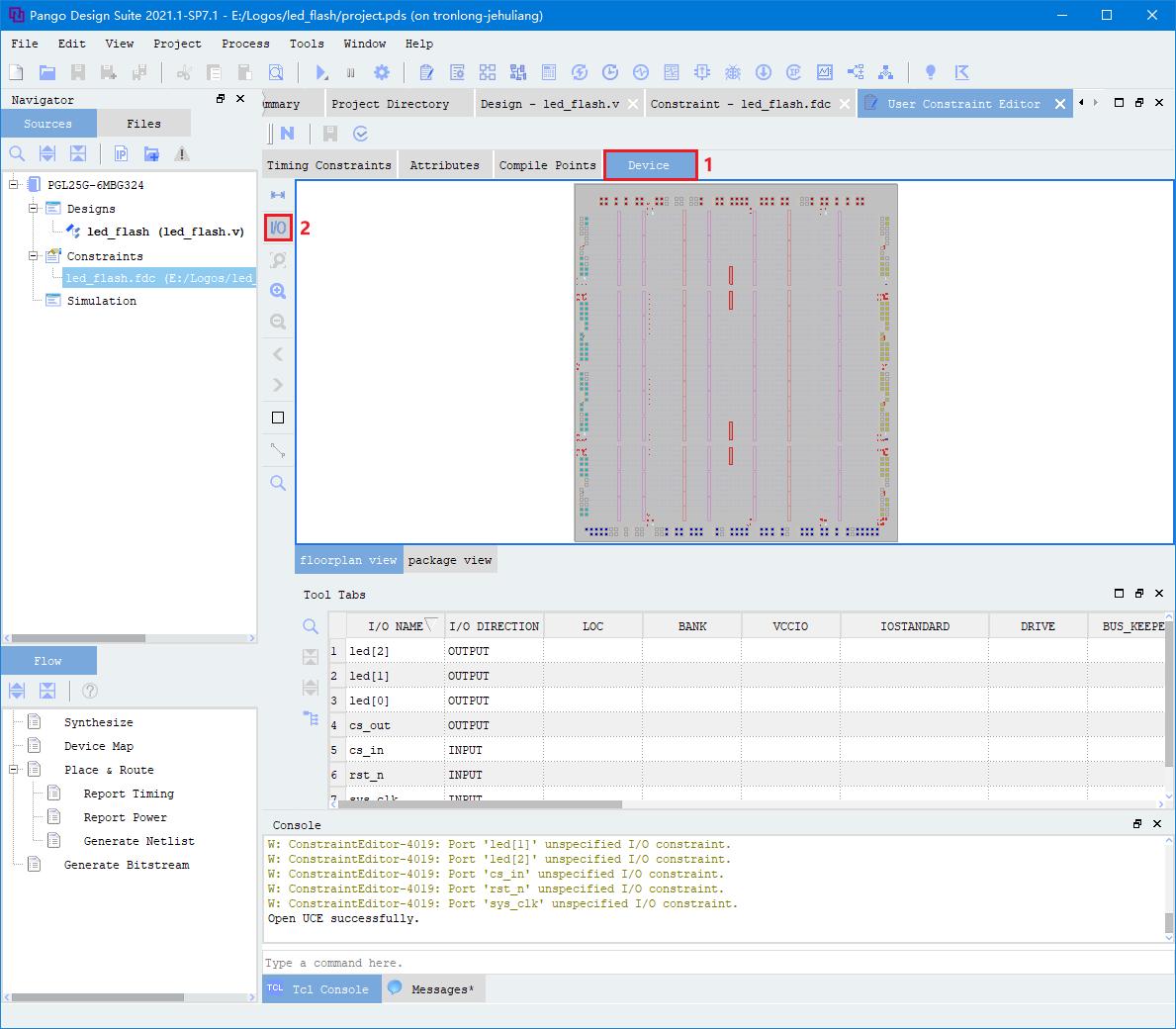

图 45在如下界面选项栏中,依次点击"Device -> IO",根据工程xxx.v文件在"Tool Tabs"窗口生成引脚约束列表。请根据硬件连接进行引脚选择。

图 46

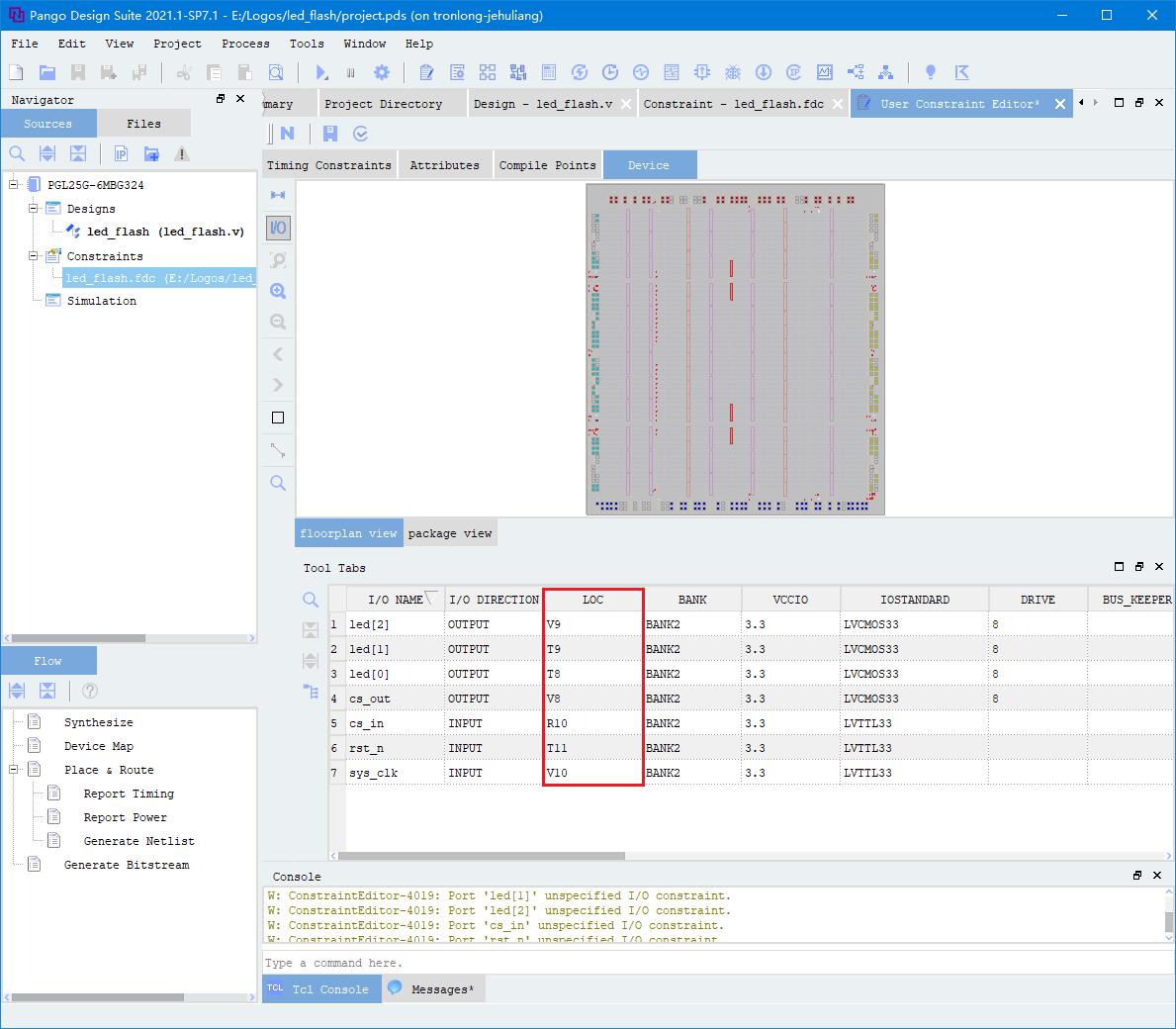

图 46引脚选择完成后,呈现界面如下图所示。至此,FPGA工程新建完成。

图 47

图 47程序编译

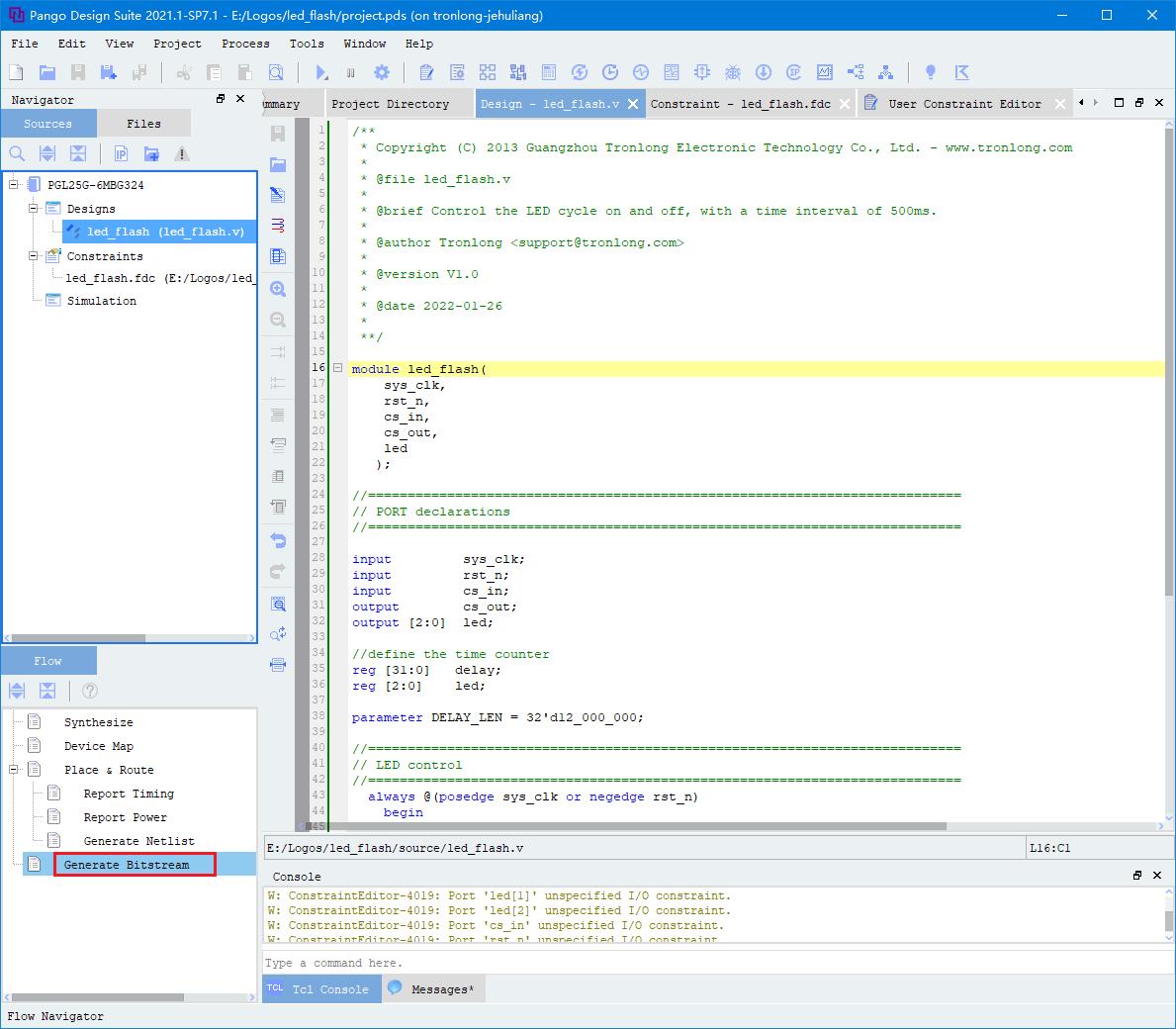

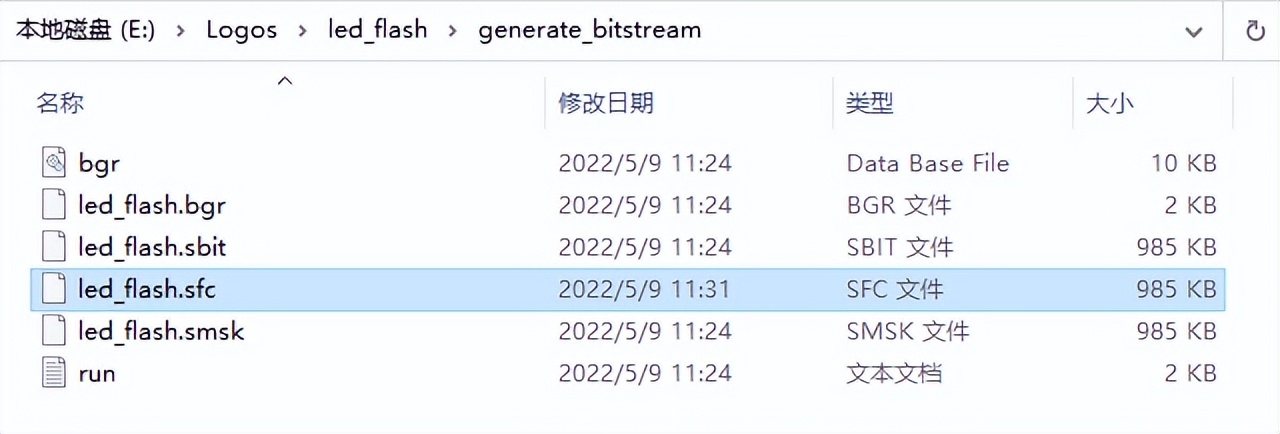

- 双击"Generate Bitstream"进行FPGA程序编译。

图 48

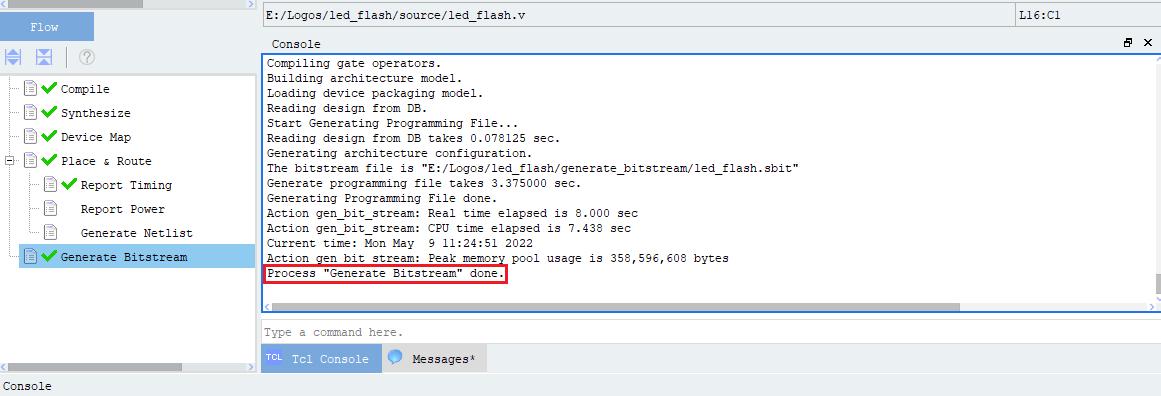

图 48编程完成后Console窗口将会打印信息:Process "Generate Bitstream" done,并在FPGA工程generate_bitstream目录下生成xxx.sbit文件。

图 49

图 49 图 50

图 50如需生成用于固化至SPI FLASH的xxx.sfc文件,请按照如下步骤执行。

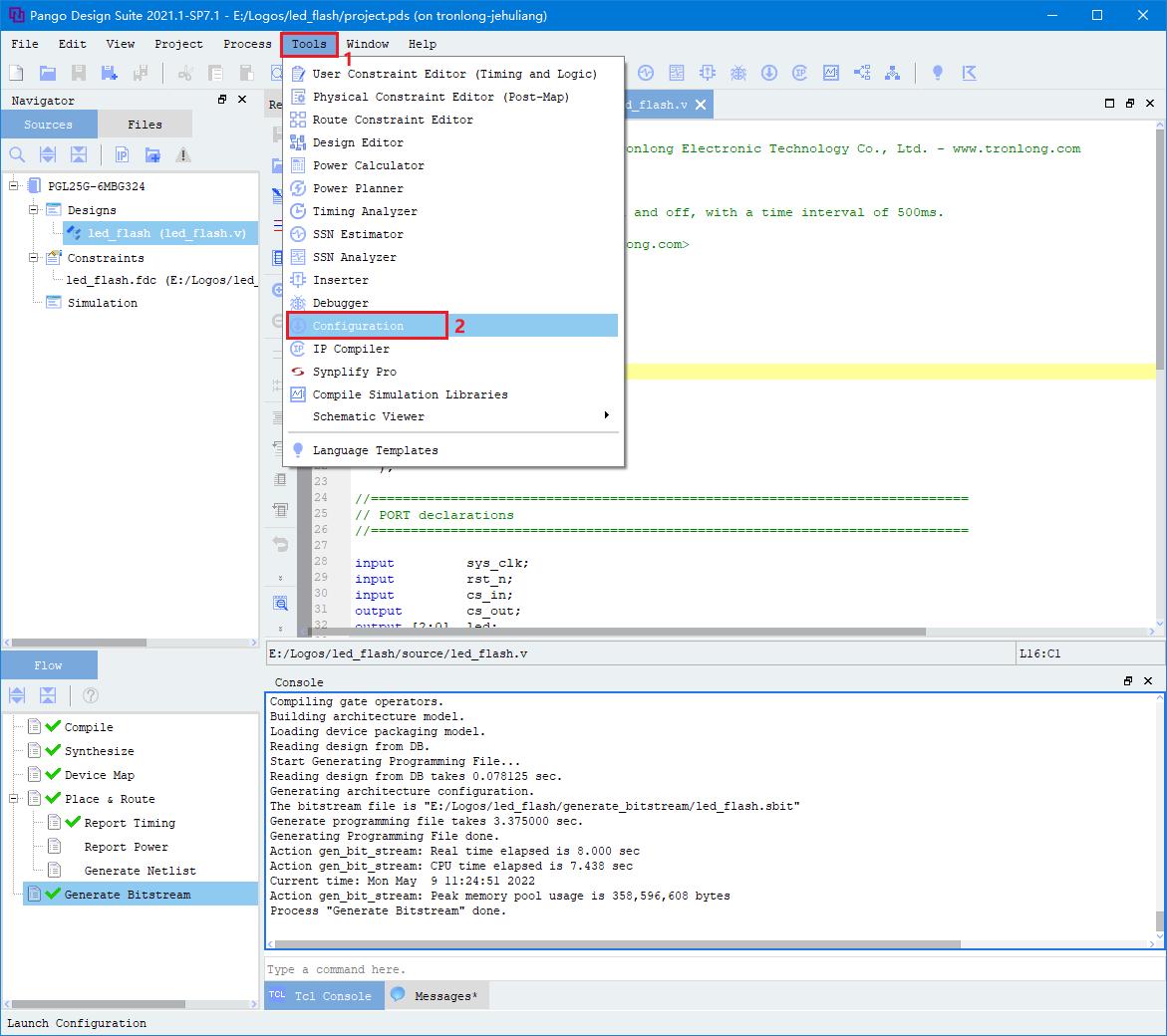

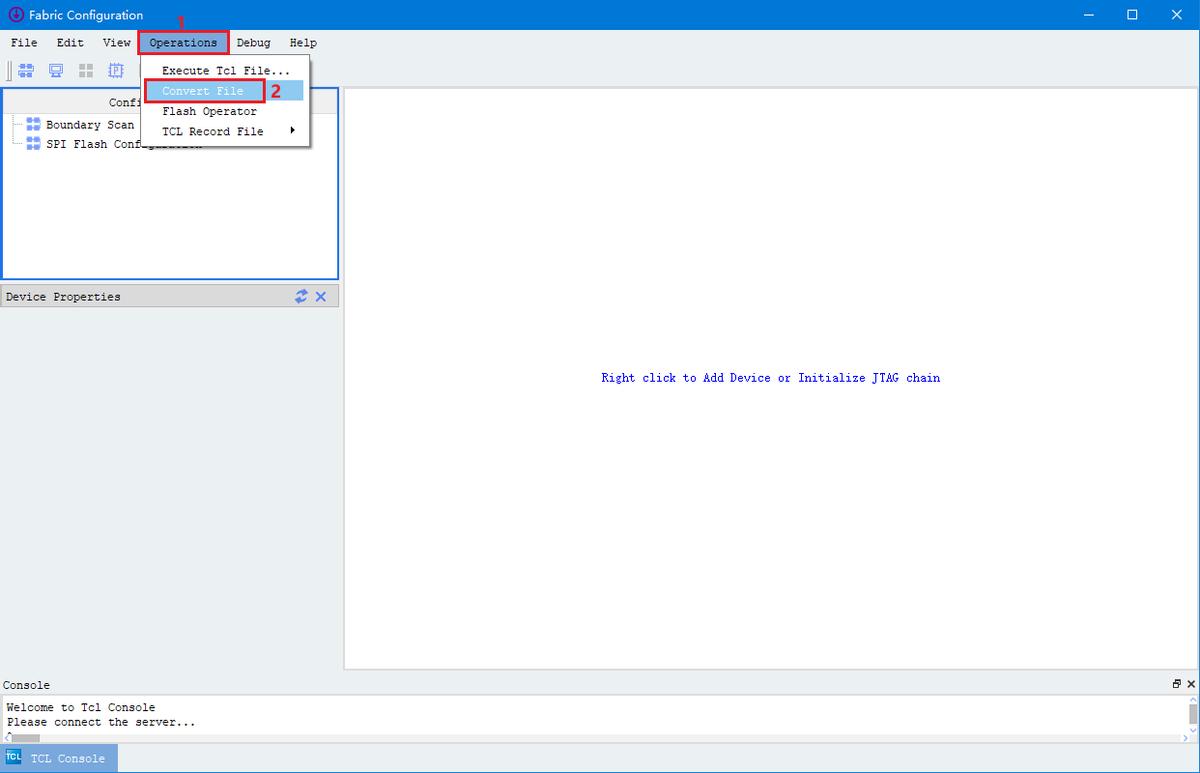

- 在菜单栏依次点击"Tools -> Configuration",进入Fabric Configuration界面,在菜单栏依次点击"Operations -> Convert File"。

图 51

图 51 图 52

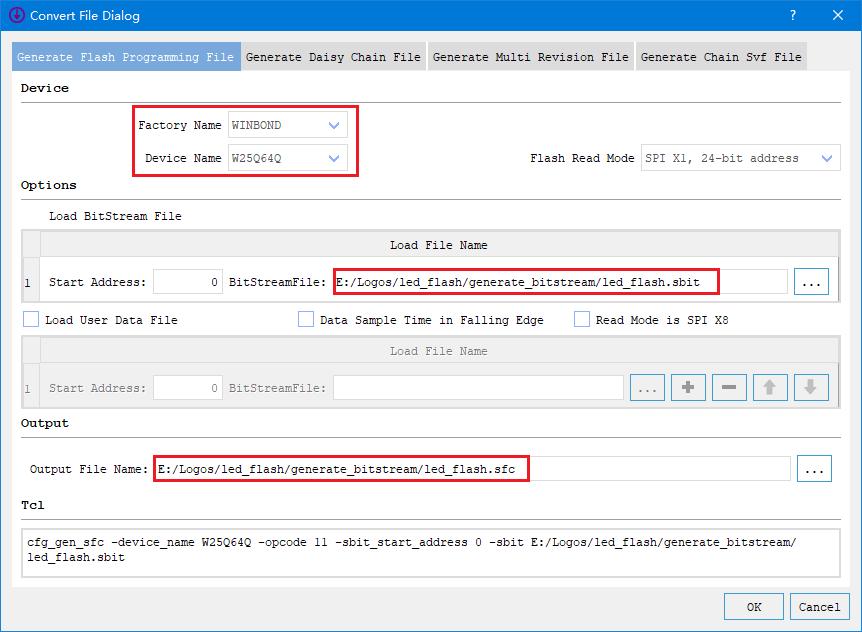

图 52在弹出界面,请按照下图方法配置SPI FLASH信息。Factory Name:WINBOND,Device Name:W25Q64Q(SPI FLASH芯片型号),BitStramFile:BitStramFile文件(xxx.sbit)路径,Output File Name:生成xxx.sfc文件保存路径(默认保存在BitStramFile文件同级目录下)。配置完成后,请点击OK保存配置。

图 53

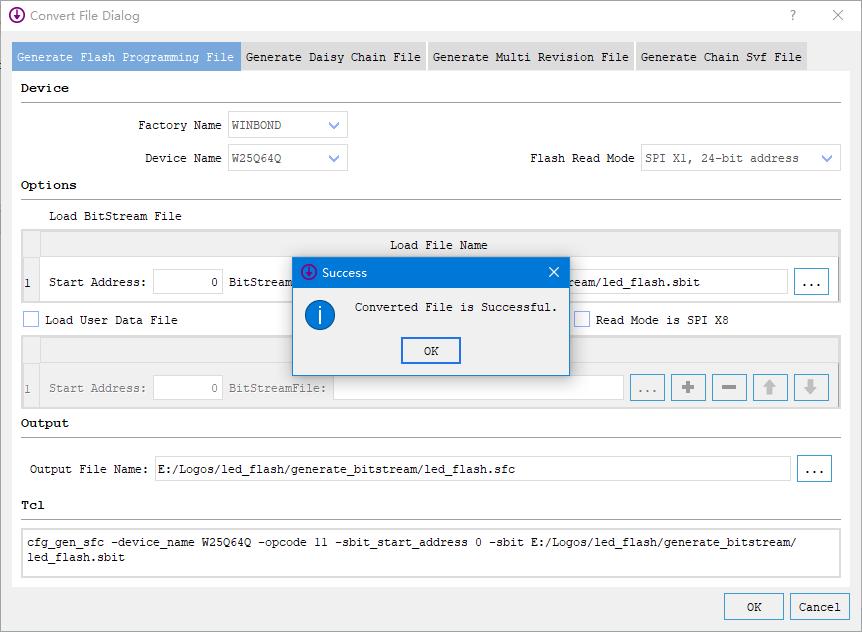

图 53弹出如下界面,请点击OK。即已成功生成用于固化至SPI FLASH的xxx.sfc文件。

图 54

图 54 图 55

图 55全志T3+FPGA国产核心板——Pango Design Suite的FPGA程序加载固化的更多相关文章

- 【新产品发布】【iCore2 ARM / FPGA 双核心板】

iCore2是一款包含ARM / FPGA两大利器的双核心板.ARM方面,采用意法半导体高性能的32位Cortex-M3内核STM32F103VE微处理器,主频达72MHz,并包含丰富外设接口.FPG ...

- 巧用代理设计模式(Proxy Design Pattern)改善前端图片加载体验

这篇文章介绍一种使用代理设计模式(Proxy Design Pattern)的方法来改善您的前端应用里图片加载的体验. 假设我们的应用里需要显示一张尺寸很大的图片,位于远端服务器.我们用一些前端框架的 ...

- u-boot-2011.06在基于s3c2440开发板的移植之引导内核与加载根文件系统

http://www.linuxidc.com/Linux/2012-09/70510.htm 来源:Linux社区 作者:赵春江 uboot最主要的功能就是能够引导内核启动.本文就介绍如何实现该 ...

- 【iCore4 双核心板】4.3寸液晶模块程序发布

一.说明 1.本资料包程序包含两部分,"CAPTURE"为液晶显示截图,"tft4.3"为ARM程序. 2.此程序只适合iCore4液晶模块. 3.iCore4 ...

- 【iCore3 双核心板_FPGA】实验二十二:Niosii——固化程序到 EPCS 里

实验指导书及代码包下载: http://pan.baidu.com/s/1c2lyNQS iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC72K325T的高速数据处理核心板

基于TI DSP TMS320C6678.Xilinx K7 FPGA XC72K325T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

- 175-基于TI DSP TMS320C6455、Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板

基于TI DSP TMS320C6455.Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

- 【iCore1S 双核心板_ARM】例程十七:FSMC实验——读写FPGA

实验现象: 先烧写FPGA程序,再烧写ARM程序,ARM程序烧写完毕后即开始读写RAM测试,测试成功,绿色ARM·LED亮,测试失败,红色ARM·LED闪烁. 核心代码: int main(void) ...

- 【iCore3 双核心板】DEMO 1.0 测试程序发布

iCore3 Demo V1.0 程序说明 一.概要 本资料包包含5个文件夹: 1.“arm”里是 icore3上 arm的程序包,开发环境为 KEIL 5.17: 2.“fpga”里是 icore3 ...

- 【iCore4 双核心板】DEMO V1.0 测试程序发布

iCore4 Demo V1.0程序说明 一.概要 本资料包含5个文件夹: 1.“arm”里是iCore4上arm的程序包,开发环境为KEIL5.17: 2.“fpga”里是iCore4上FPGA的程 ...

随机推荐

- Golang从入门到微服务

学习视频: https://www.bilibili.com/video/BV1Sg411T7TV?p=69 学习资料下载: 链接: https://pan.baidu.com/s/1Yk4GemFR ...

- 09. C语言内嵌汇编代码

C语言函数内可以自定义一段汇编代码,在GCC编译器中使用 asm 或 __asm__ 关键词定义一段汇编代码,并可选添加volatile关键字,表示不要让编译器优化这段汇编代码. 内嵌汇编代码格式如下 ...

- 纯JS制作选项卡--JavaScript实例集锦(初学)

最近重新从最基础学习JavaScript,如同盖房,先要打好基础,一砖一瓦都很重要. 下面我来嘚吧几句,附上从书上学到的实例与效果. JS可以用面向过程去写,也可以使用面向对象.面向对象会使一段JS代 ...

- grads 同时读取多个ctl文件方法

1.不同的文件进行不同的设置:'set dfile 2' 2.读取不同文件的变量:qv.2 实例如下:'reinit''open e:\tskt.CTL''open e:\uwnd.CTL''open ...

- salesforce零基础学习(一百三十六)零碎知识点小总结(八)

本篇参考: Salesforce LWC学习(七) Navigation & Toast https://developer.salesforce.com/docs/platform/lwc/ ...

- 使用 Python 旋转PDF页面、或调整PDF页面顺序

在将纸质文档扫描成PDF电子文档时,有时可能会出现页面方向翻转或者页面顺序混乱的情况.为了确保更好地浏览和查看PDF文件,本文将分享一个使用Python来旋转PDF页面或者调整PDF页面顺序的解决方案 ...

- vue3编译优化之“静态提升”

前言 在上一篇 vue3早已具备抛弃虚拟DOM的能力了文章中讲了对于动态节点,vue做的优化是将这些动态节点收集起来,然后当响应式变量修改后进行靶向更新.那么vue对静态节点有没有做什么优化呢?答案是 ...

- PageOffice6最简集成代码(Asp.Net)

本文描述了PageOffice产品在普通的Asp.Net项目中如何集成调用. 新建Asp.Net项目:PageOffice6-Net-Simple 在您的web项目的"依赖项-包-管理NuG ...

- ICESat-2 ATL03光子数据读取

ICESat-2数据处理的方式一般为将光子数据投影到沿轨距离和高程的二维空间.如下图: ATL03数据读取 H5是一种数据存储结构,读取原理就是按照该结构获取数据,这里给出两种读取方式. ATL03的 ...

- php的下载与安装

一,进入到php的官方网站 https://www.php.net/ ,进入到下载页面: 选择 PHP 7.2.30 的Windows版本 具体的下载页面版本区分: 下载后,得到如下压缩包到如 ...