TCAM CAM 说明 原理 结构 Verilog 硬件实现

TCAM 三态内容地址查找存储器,CAM内容地址查找存储器。区别在于TCAM多了一级掩码功能,也就是说可以指定某几位是dont care。匹配的时候0,1都行的意思。

广泛应用于数据流处理领域,本文简要介绍TCAM和CAM的逻辑组成和Verilog实例。

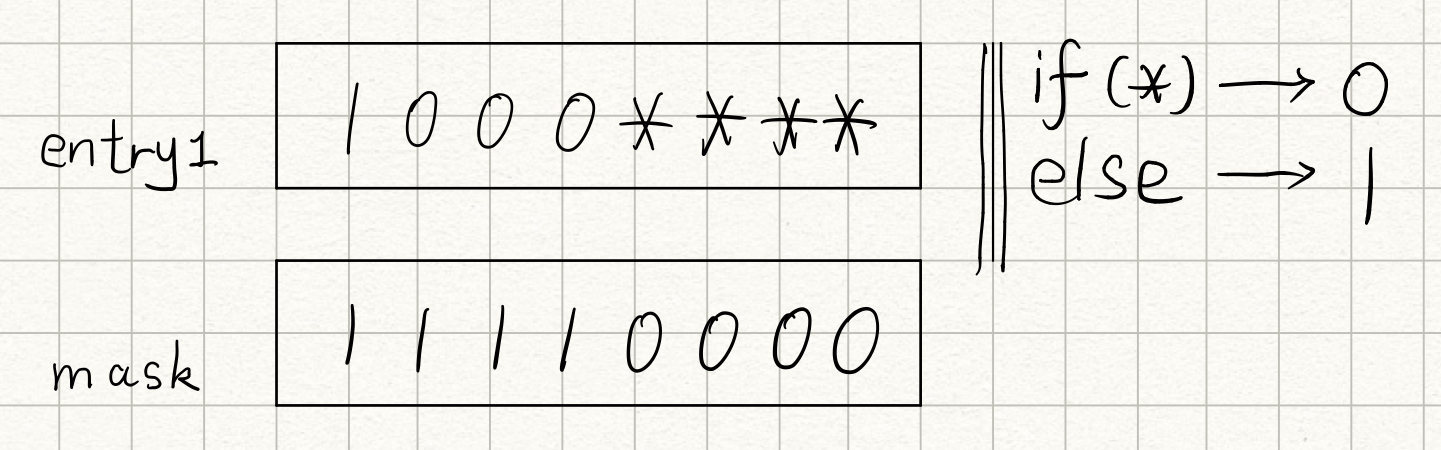

TCAM对于一个带mask的表项,如:“1000 * * * * ”。

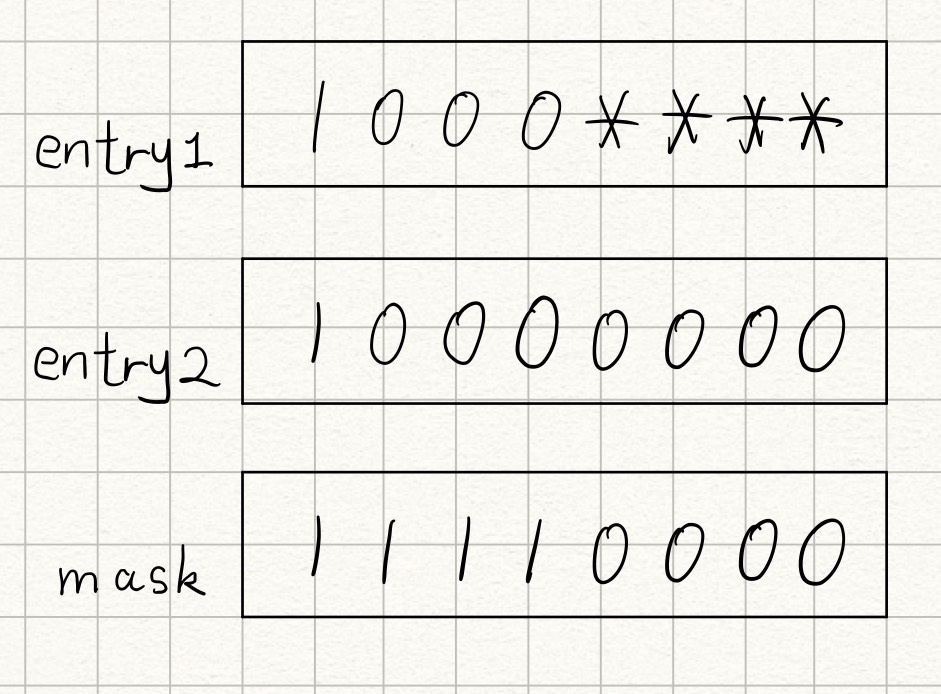

为表达流表项,我们在下载流表之前我们需要做一步计算,

首先将其分解为entry1 和 mask:

第二步,令entry2 = entry & mask

所以entry2 = 10000000

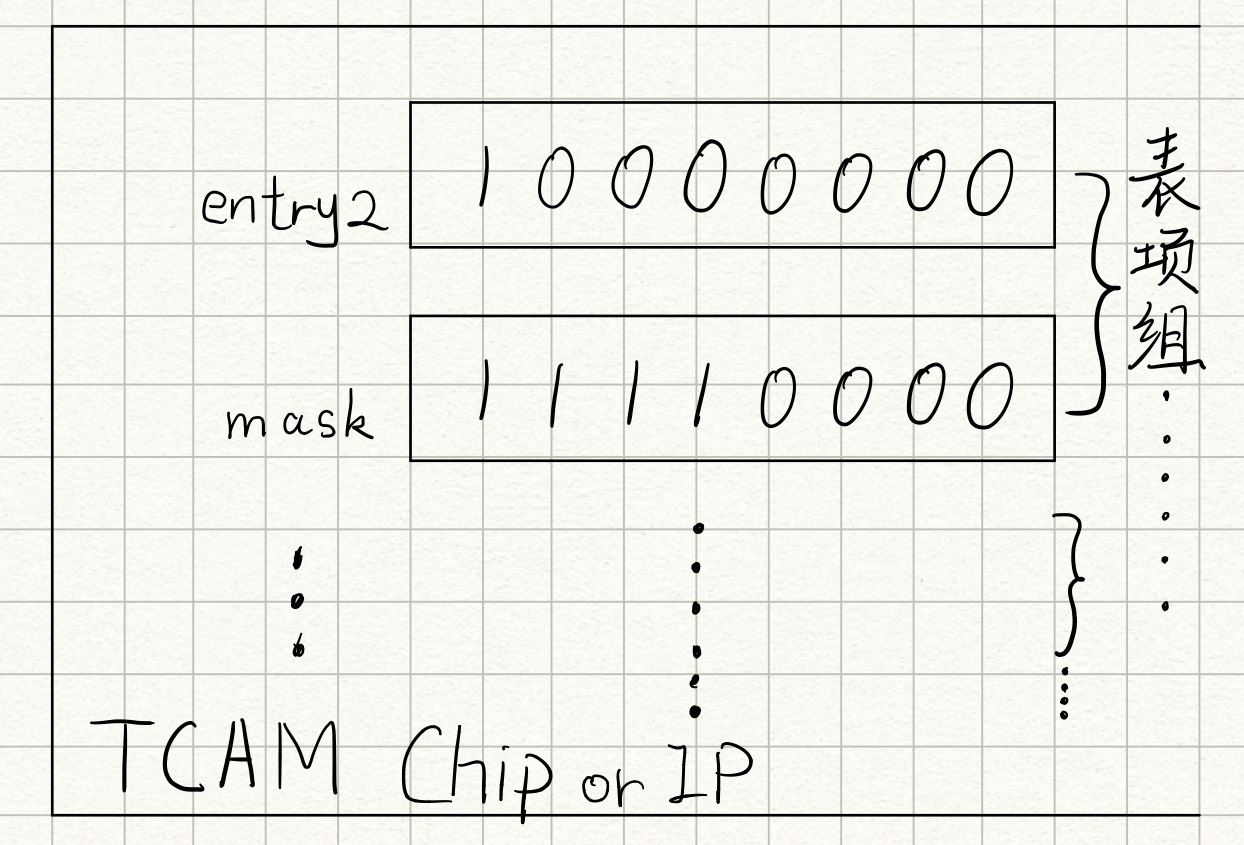

将entry2 和mask 下载存入TCAM表项组中:

在做查找的时候,key广播到每个表项组中。之后将key和当前表项组中的mask做与运算,如key = 10001010. key& mask = 10001010 & 11110000 = 10000000

最后再和entry做比较,如果相等则将1写入结果寄存器。之后所有的结果汇总到优先级选路器中。并得到id编号。

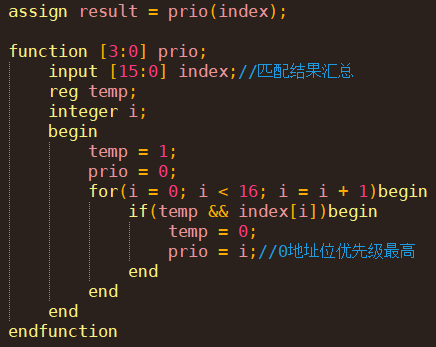

优先级选路器:

可以用function函数实现:

参考代码请看这里一个粗糙的实现:https://github.com/qiaosiyi/progASICp4SWITCH/blob/master/tcam.v

这样我们基本上就可以用Verilog语言去实现了,其次要注意的是,广播,复制,或者做逻辑运算,都会比较占用时延,不要在一个时钟周期去做,很可能无法完成时序约束。

建议一个操作使用一个时钟周期,所以tcam查找我这里延迟了四个周期,但是fully-pipeline。吞吐还是一周期一次。

有时候表项很多,也许优先级选路器timing收不了,其实可以考虑将这一步延长俩周期做。其实本质相当于降低了tcam处理频率。

关于CAM:

CAM与TCAM类似,CAM是精确匹配,key广播到每个entry,然后比较出结果汇总到优先选路器中,得到id。比tcam操作步骤减少了一些,而且逻辑资源也减少了很多。

可以在这里看一下我粗糙的代码:https://github.com/qiaosiyi/progASICp4SWITCH/blob/master/cam.v

========================

qsy

15MAR2019

TCAM CAM 说明 原理 结构 Verilog 硬件实现的更多相关文章

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 定点CORDIC算法求所有三角函数及向量模的原理分析、硬件实现(FPGA)

一.CORDIC算法 CORDIC(Coordinate Rotation DIgital Computer)是一种通过迭代对多种数学函数求值的方法,它可以对三角函数.双曲函数和平面旋转问题进行求解. ...

- 格雷码原理与Verilog实现

格雷码原理 格雷码是一个叫弗兰克*格雷的人在1953年发明的,最初用于通信.格雷码是一种循环二进制码或者叫作反射二进制码.格雷码的特点是从一个数变为相邻的一个数时,只有一个数据位发生跳变,由于这种特点 ...

- 我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言

这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器. 3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下: | 输入 | 输出 | -------- ...

- FIR滤波原理及verilog设计

FIR(Finite Impulse Response)Filter:有限冲激响应滤波器,又称为非递归线性滤波器. FIR滤波器的冲击响应是一个值为滤波器抽头系数的采样序列,其脉冲响应由有限个采样值构 ...

随机推荐

- SQL Server 跨服务器 不同数据库之间复制表的数据

不同数据库之间复制表的数据的方法: 当表目标表存在时: insert into 目的数据库..表 select * from 源数据库..表 当目标表不存在时: select * into 目的数据库 ...

- 最短路径求解(Dijkstra)

Dijkstra算法分析 题目分析参照<数据结构>(严蔚敏)7-6节 最短路径问题描述 参照日常生活中的公交查询系统.我们有选项: 少换乘/最少站数 价格最少/时间最短.... (ps:下 ...

- bzoj1024

题意: 给你一个x*y的矩阵,让你把他用n-1次切割分成n块 要求每一块的长与宽的比值最大的最小 求这个比值(保留6位小数) 题解: 本来想用二分来做 然而n<=10 所以我们可以暴力枚举+贪心 ...

- Maven入门-1.介绍及搭建开发环境

1.介绍1.1 Maven和Ant的比较?2.搭建Maven开发环境2.1 配置环境变量2.2 测试安装是否成功2.3 配置Maven的本地仓库位置3.Maven的约定4.Maven项目类型5.Mav ...

- facade外观模式

通过买股票与通过基金买股票引出外观模式: package com.disign.facade; /** * Created by zhen on 2017-05-18. */ public class ...

- win10中jdk1.8环境配置完,重启之后配置失效

1.win10操作系统下重启电脑java环境变量失效 解决方式: 右击开始按钮,选择管理员方式的windows powershell,如下图: 在窗口中输入javac,一切正常,即使重启都不会有问题啦 ...

- train validation test

http://stats.stackexchange.com/questions/19048/what-is-the-difference-between-test-set-and-validatio ...

- supervisor 使用tips

Supervisor (http://supervisord.org) 是一个用 Python 写的进程管理工具,可以很方便的用来启动.重启.关闭进程,supervisor可以同时监控多个进程,并可以 ...

- C#中时间计算方法汇总

这几天要做一个关于时间数据统计的页面,发现有些东西还是比较用的,现总结如下. DateTime dt = DateTime.Now; //当前时间 DateTime startWeek = dt.A ...

- CenOS7.4内核升级修复系统漏洞

先查看当前内核版本# uname -a 一. 导入key# rpm --import https://www.elrepo.org/RPM-GPG-KEY-elrepo.org 二. 安装elrepo ...