ARM协处理器CP15寄存器详解

改自:https://blog.csdn.net/gameit/article/details/13169405

*C2描述的不对,bit[31-14]才是TTB,不是所有的bit去存储ttb。很明显,从C7开始,博主已经懒得打字了,直接书本截图*

<Rd>不能为PC。 当其为PC时。指令操作结果不可预知。

- 在基于ARM的嵌入式系统中,存储系统通常是通过系统控制协处理器CP15完成的。

- CP15可以包含16个32位的寄存器,其编号为0-15。实际上对于某些编号的寄存器可能对应有多个物理寄存器。在指令中指定特定的标志位来区分这些物理寄存器。有些类似于ARM寄存器中,处于不同的处理器模式时,ARM某些寄存器可能不同。

|

寄存器编号 |

基本作用 |

在 MMU 中的作用 |

在 PU 中的作用 |

|

0 |

ID 编码(只读) |

ID 编码和 cache 类型 |

|

|

1 |

控制位(可读写) |

各种控制位 |

|

|

2 |

存储保护和控制 |

地址转换表基地址 |

Cachability 的控制位 |

|

3 |

存储保护和控制 |

域访问控制位 |

Bufferablity 控制位 |

|

4 |

存储保护和控制 |

保留 |

保 留 |

|

5 |

存储保护和控制 |

内存失效状态 |

访问权限控制位 |

|

6 |

存储保护和控制 |

内存失效地址 |

保护区域控制 |

|

7 |

高速缓存和写缓存 |

高速缓存和写缓存控制 |

|

|

8 |

存储保护和控制 |

TLB 控制 |

保 留 |

|

9 |

高速缓存和写缓存 |

高速缓存锁定 |

|

|

10 |

存储保护和控制 |

TLB 锁定 |

保 留 |

|

11 |

保留 |

||

|

12 |

保留 |

||

|

13 |

进程标识符 |

进程标识符 |

|

|

14 |

保留 |

||

|

15 |

因不同设计而异 |

因不同设计而异 |

因不同设计而异 |

|

opcode2 编码 |

对应的标识符号寄存器 |

|

0b000 |

主标识符寄存器 |

|

0b001 |

cache类型标识符寄存器 |

|

其 他 |

保留 |

对于AMR7之后的处理器,其主标示符编码格式如下 :

|

30 24 |

23 20 |

19 16 |

15 4 |

3 0 |

|

由生产商确定 |

产品子编号 |

ARM 体系版本号 |

产品主编号 |

处理器版本号 |

|

位 |

说 明 |

|

位 [3: 0] |

生产商定义的处理器版本号 |

|

位 [15: 4] |

生产商定义的产品主编号 其中最高 4 位即位 [15:12] 可能的取值为0x0~0x7 但不能是 0x0 或 0x7 因为: 0x0表示 ARM7之前的处理器 0x7 表示ARM7处理器 |

|

位 [19: 16] |

ARM 体系的版本号,可能的取值如 下: 0x1 ARM 体系版本 4 0x2 ARM 体系版本 4T 0x3 ARM 体系版本 5 0x4 ARM 体系版本 5T 0x5 ARM 体系版本 5TE 其他 由 ARM 公司保留将来使用 |

|

位 [23: 20] |

生产商定义的产品子编号。当产品主编号相同时,使用子编号来区分不同的产品子类,如产品中不 同的高速缓存的大小等 |

|

位 [31: 24] |

生产厂商的编号,现在已经定义的有以下值: 0x41 =A ARM 公司 0x44 =D Digital Equipment 公司 0x69 =I intel 公司 |

|

31 29 |

28 25 |

24 |

23 12 |

11 0 |

|

000 |

属性字段 |

S |

数据 cache 相关属性 |

指令cache 相关属性 |

|

位 |

含义 |

|

位 [28: 25] |

主要用于定义对于写回类型的cache的一些属性 |

|

位 [24] |

定义系统中的数据 cache 和指令 cache 是分开的还是统一的: 0 系统的数据 cache 和指令 cache 是统一的; 1 系统的数据 cache 和指令 cache 是分开的 |

|

位 [23: 12] |

定义数据 cache 的相关属性 如果位 [24] 为 0 ,本字段定义整个cache 的属性 |

|

位 [31: 24] |

定义指令 cache 的相关属性 如果位 [24] 为 0 ,本字段定义整个cache 的属性 |

- 控制字段位 [28 : 25] 的含义

cache 类型标识符寄存器的控制字段位 [28 : 25]:

|

编 码 |

cache 类型 |

cache 内容清除方法 |

cache 内容锁定方法 |

|

0b0000 |

写通类型 |

不需要内容清除 |

不支持内容锁定 |

|

0b0001 |

写回类型 |

数据块读取 |

不支持内容锁定 |

|

0b0010 |

写回类型 |

由寄存器 C7 定义 |

不支持内容锁定 |

|

0b0110 |

写回类型 |

由寄存器 C7 定义 |

支持格式 A |

|

0b0111 |

写回类型 |

由寄存器 C7 定义 |

支持格式 B |

- 控制字段位 [23 : 12] 及控制字段位 [11 : 0] 含义

|

11 9 |

8 6 |

5 3 |

2 |

1 0 |

|

000 |

cache 容量 |

cache 相联特性 |

M |

块大小 |

其中bits[1:0]含义如下:

|

编 码 |

cache 块大小 |

|

0b00 |

2 个 字( 8 字节) |

|

0b01 |

4 个 字( 16 字节) |

|

0b10 |

8 个 字( 32 字节) |

|

0b11 |

16 个 字( 64 字节) |

其中bits[5:3]含义如下:

|

编 码 |

M=0 时含义 |

M=1 时含义 |

|

0b000 |

1 路 相联(直接映射) |

没有 cache |

|

0b001 |

2 路 相联 |

3 路 相联 |

|

0b010 |

4 路 相联 |

6 路 相联 |

|

0b011 |

8 路 相联 |

12 路 相联 |

|

0b100 |

16 路 相联 |

24 路 相联 |

|

0b101 |

32 路 相联 |

48 路 相联 |

|

0b110 |

64 路 相联 |

96 路 相联 |

|

0b111 |

128 路相联 |

192 路相联 |

其中bits[8:6]含义如下:

|

编 码 |

M=0 时含义 |

M=1时含义 |

|

0b000 |

0.5KB |

0.75 KB |

|

0b001 |

1 KB |

1.5 KB |

|

0b010 |

2 KB |

3 KB |

|

0b011 |

4 KB |

6 KB |

|

0b100 |

8 KB |

12 KB |

|

0b101 |

16 KB |

24 KB |

|

0b110 |

32 KB |

48 KB |

|

0b111 |

64 KB |

96 KB |

- 禁止或使能MMU以及其他与存储系统相关的功能

- 配置存储系统以及ARM处理器中的相关部分的工作

|

C1中的控制位 |

含义 |

|

M(bit[0]) |

0 :禁止 MMU 或者 PU 1 :使能 MMU 或者 PU 如果系统中没有MMU及PU,读取时该位返回0,写入时忽略该位 |

|

A(bit[1]) |

0 :禁止地址对齐检查 1 :使能地址对齐检查 |

|

C(bit[2]) |

当数据cache和指令cache分开时,本控制位禁止/使能数据cache。当数据cache和指令cache统一时,该控制位禁止/使能整个cache。 0 :禁止数据 / 整个 cache 1 :使能数据 / 整个 cache 如果系统中不含cache,读取时该位返回0.写入时忽略 当系统中不能禁止cache 时,读取时返回1.写入时忽略 |

|

W(bit[3]) |

0 :禁止写缓冲 1 :使能写缓冲 如果系统中不含写缓冲时,读取时该位返回0.写入时忽略 当系统中不能禁止写缓冲时,读取时返回1.写入时忽略 |

|

P(bit[4]) |

对于向前兼容26位地址的ARM处理器,本控制位控制PROG32控制信号 0 :异常中断处理程序进入 32 位地址模式 1 :异常中断处理程序进入26 位地址模式 如果本系统中不支持向前兼容26位地址,读取该位时返回1,写入时忽略 |

|

D(bit[5]) |

对于向前兼容26位地址的ARM处理器,本控制位控制DATA32控制信号 0 :禁止 26 位地址异常检查 1 :使能 26 位地址异常检查 如果本系统中不支持向前兼容26位地址,读取该位时返回1,写入时忽略 |

|

L(bit[6]) |

对于ARMv3及以前的版本,本控制位可以控制处理器的中止模型 0 :选择早期中止模型 1 :选择后期中止模型 |

|

B(bit[7]) |

对于存储系统同时支持big-endian和little-endian的ARM系统,本控制位配置系统的存储模式 0 : little endian 1 : big endian 对于只支持little-endian的系统,读取时该位返回0,写入时忽略 对于只支持big-endian的系统,读取时该位返回1,写入时忽略 |

|

S(bit[8]) |

在基于 MMU 的存储系统中,本位用作系统保护 |

|

R(bit[9]) |

在基于 MMU 的存储系统中,本位用作 ROM 保护 |

|

F(bit[10]) |

由生产商定义 |

|

Z(bit[11]) |

对于支持跳转预测的ARM系统,本控制位禁止/使能跳转预测功能 0 :禁止跳转预测功能 1 :使能跳转预测功能 对于不支持跳转预测的ARM系统,读取该位时返回0,写入时忽略 |

|

I(bit[12]) |

当数据cache和指令cache是分开的,本控制位禁止/使能指令cache 0 :禁止指令 cache 1 :使能指令 cache 如果系统中使用统一的指令cache和数据cache或者系统中不含cache,读取该位时返回0,写入时忽略。当系统中的指令cache不能禁止时,读取时该位返回1,写入时忽略 |

|

V(bit[13]) |

对于支持高端异常向量表的系统,本控制位控制向量表的位置 0 :选择低端异常中断向量 0x0~0x1c 1 :选择高端异常中断向量0xffff0000~ 0xffff001c 对于不支持高端异常向量表的系统,读取时该位返回0,写入时忽略 |

|

PR(bit[14]) |

如果系统中的cache的淘汰算法可以选择的话,本控制位选择淘汰算法 0 :常规的 cache 淘汰算法,如随机淘汰 1 :预测性淘汰算法,如round-robin 淘汰算法 如果系统中cache的淘汰算法不可选择,写入该位时忽略。读取该位时,根据其淘汰算法是否可以比较简单地预测最坏情况返回0或者1 |

|

L4(bit[15]) |

对于ARM版本5及以上的版本,本控制位可以提供兼容以前的ARM版本的功能 0 :保持 ARMv5 以上版本的正常功能 1 :将 ARMv5 以上版本与以前版本处理器 兼容,不根据跳转地址的 bit[0] 进行 ARM 指令和 Thumb 状态切换: bit[0] 等于 0 表示 ARM 指令,等于 1 表示 Thumb 指令 |

|

Bits[31:16]) |

这些位保留将来使用,应为UNP/SBZP |

(三)CP15 的寄存器 C2

C2寄存器的别名:Translation table base (TTB) register

C2寄存器用来保存页表的基地址,即一级映射描述符表的基地址。其编码格如下所示:

|

31 0 |

|

一级映射描述符表的基地址(物理地址) |

CP15 中的寄存器 C3 定义了 ARM 处理器的 16 个域的访问权限。

|

31 0 |

|||||||||||||||

|

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

10:保留状态(我们最好不要填写该值,以免引起不能确定的问题)

11:当前级别下,对该内存区域的访问都不进行权限检查。 这时 AP位无效

MRC p15, 0, <Rd>, c5, c0, 0 访问数据失效状态寄存器

MRC p15, 0, <Rd>, c5, c0, 1 访问指令状态失效寄存器

编码格式如下所示:

|

31 9 |

8 |

7 4 |

3 0 |

|

UNP/SBZP |

0 |

域标识 |

状态标识 |

其中,域标识bit[7:4]表示存放引起存储访问失效的存储访问所属的域。

状态标识 bit[3:0] 表示放引起存储访问失效的存储访问类型,该字段含义如下表所示(优先级由上到下递减)。

|

引起访问失效的原因 |

状态标识 |

域标识 |

C6 |

|

终 端异常( Terminal Exception ) |

0b0010 |

无 效 |

生 产商定义 |

|

中 断向量访问异常( Vector Exception) |

0b0000 |

无 效 |

有 效 |

|

地 址对齐 |

0b00x1 |

无 效 |

有 效 |

|

一 级页表访问失效 |

0b1100 |

无 效 |

有 效 |

|

二 级页表访问失效 |

0b1110 |

有 效 |

有 效 |

|

基 于段的地址变换失效 |

0b0101 |

无 效 |

有 效 |

|

基 于页的地址变换失效 |

0b0111 |

有 效 |

有 效 |

|

基 于段的存储访问中域控制失效 |

0b1001 |

有 效 |

有 效 |

|

基 于页的存储访问中域控制失效 |

0b1101 |

有 效 |

有 效 |

|

基 于段的存储访问中访问权限控制失效 |

0b1111 |

有 效 |

有 效 |

|

基 于页的存储访问中访问权限控制失效 |

0b0100 |

有 效 |

有 效 |

|

基 于段的 cache 预 取时外部存储系统失效 |

0b0110 |

有 效 |

有 效 |

|

基 于页的 cache 预 取时外部存储系统失效 |

0b1000 |

有 效 |

有 效 |

|

基 于段的非 cache 预 取时外部存储系统失效 |

0b1010 |

有 效 |

有 效 |

CP15 中的寄存器 C6 是失效地址寄存器,其中保存了引起存储访问失效的地址,分为数据失效地址寄存器和指令失效地址寄存器

MRC p15, 0, <Rd>, c6, c0, 0 访问数据失效地址寄存器

MRC p15, 0, <Rd>, c6, c0, 2 访问指令失效地址寄存器

编码格式如下所示:

|

31 0 |

|

失效地址(虚拟地址) |

系统协处理器CP15的寄存器C8就是清除TLB内容的相关操作。它是一个只写的寄存器。

MCR p15,0,Rd,c8,CRm,opcode_2

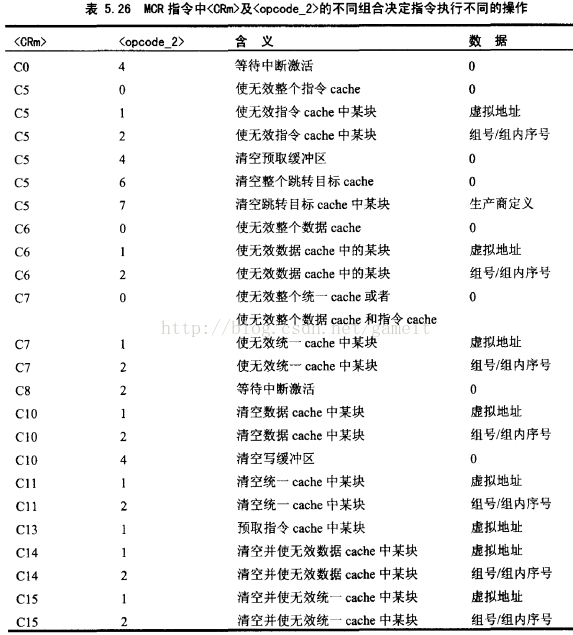

Rd中为要写入C8寄存器的内容,CRm和opcode_2的不同组合决定指令执行的不同操作。

|

指令 |

Rd |

含义 |

MCR p15, 0, Rd, c8, c5, 0 |

0 |

使无效整个指令TLB |

MCR p15, 0, Rd, c8, c5, 1 |

虚拟地址 |

使无效指令TLB中的单个地址变换条目 |

MCR p15, 0, Rd, c8, c6, 0 |

0 |

使无效整个数据TLB |

MCR p15, 0, Rd, c8, c6, 1 |

虚拟地址 |

使无效数据TLB中的单个地址变换条目 |

MCR p15, 0, <Rd>, c8, c7, 0 |

0 |

使无效整个数据和指令TLB |

MCR p15, 0, <Rd>, c8, c7, 1 |

虚拟地址 |

使无效数据和指令TLB中的单个地址变换条目 |

MCR p15, 0, <Rd>, c12, c0, 0 ;Rd中存放要修改的异常向量基地址

|

31 5 |

4 0 |

|

异常向量基地址 |

Reserve |

CP15中的寄存器C13用于快速上下文切换。其编码格式如下所示。

访问寄存器C13的指令格式如下所示。

MCR p15, 0,<Rd>,<c13>,c0,0

MRC P15, 0,<Rd>,<c13>,c0,0

其中, 在读操作时,结果中位[31::25]返回PID,其他位 的数值是不可以预知的。写操作将设置PID的值。

当PID的值为0时,MVA = VA | (0(PID)<<25),MVA=VA,相当于禁止了FCSE。系统复位后PID即为0.

当PID的值不为0时,相当于使能了FCSE。

ARM协处理器CP15寄存器详解的更多相关文章

- [转载]ARM协处理器CP15寄存器详解

用于系统存储管理的协处理器CP15 原地址:http://blog.csdn.net/gameit/article/details/13169405 MCR{cond} coproc,opc ...

- ARM协处理器CP15寄存器详解【转】

本文转载i自;https://blog.csdn.net/gameit/article/details/13169405 用于系统存储管理的协处理器CP15 MCR{cond} copro ...

- 浅析ARM协处理器CP15寄存器有关指令:MCR\MRC

ref:http://blog.csdn.net/gameit/article/details/13169405 背景: 在uboot中,start.s中涉及到了 CP15 的有关操作.查阅有关资料, ...

- 大脸猫讲逆向之ARM汇编中PC寄存器详解

i春秋作家:v4ever 近日,在研究一些开源native层hook方案的实现方式,并据此对ARM汇编层中容易出问题的一些地方做了整理,以便后来人能有从中有所收获并应用于现实问题中.当然,文中许多介绍 ...

- 2.3 ARM寄存器详解

一共有37个寄存器 1. 31个通用寄存器 2. 6个状态寄存器 R13作为堆栈指针 R14链接寄存器 1.保存函数返回地址 2. 异常返回地址 R15程序计数器(PC指针) 程序状态寄存器 只有在异 ...

- 022 ARM寄存器详解

R13:堆栈指针寄存器 SP R14:链接寄存器 LR R15:程序计数器 PC指针 CPSR:当前程序状态寄存器 SPSR:备份程序状态寄存器

- Part2_lesson3---ARM寄存器详解

进入到ARM Architecture Reference Manual这个文档里面的A2.3 Registers R13在程序中通常用于充当SP堆栈指针的!! R14在程序当中通常用于充当LR(链接 ...

- STM32_NVIC寄存器详解

在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体: typedef struct { vu32 ISER[2]; //2个32位中断使能寄存器分别对应到60 ...

- ARM字节对齐问题详解

一.什么是字节对齐,为什么要对齐? 现代计算机中内存空间都是按照byte划分的,从理论上讲似乎对任何类型的变量的访问可以从任何地址开始,但实际情况是在访问特定类型变量的时候经常在特定的内存地址访问,这 ...

随机推荐

- 常用的etl工具比较

ETL是什么? ETL,是英文 Extract-Transform-Load 的缩写,用来描述将数据从来源端经过抽取(extract).转换(transform).加载(load)至目的端的过程.(数 ...

- 使用 If-Then-Else 逻辑进行分支

If-then-else 逻辑看似简单,功能却十分强大,它可以根据不同条件执行不同的操作.If-then-else 逻辑可理解为:如果某个条件为 true (IF),则执行某个操作:如果条件为 fal ...

- sqlserver 动态sql执行execute和sp_executesql

sp_executesql的运用 书写语法要点: exec sp_executesql @sql,N’参数1 类型1,参数2 类型2,参数3 类型3 OUTPUT’,参数1,参数2,参数3 OUTPU ...

- 浅谈TextView Ellipsize效果与Marquee跑马灯无效果问题

说到TextView 效果,相信大家一定熟悉跑马灯. 先来看看 Ellipsize是什么,Ellipsize 从开发技术上翻译为省略效果.故名思议,就是当文本无法显示全部时,用什么效果来显示未显示的部 ...

- Ubuntu + Apache2 环境下用C编写 一个简单的cgi脚本

我只学习过c语言,没有学习过prel,网上很多教程都是针对prel的,很少有针对c的.自己在Ubuntu下鼓捣了一下午,也总算是用c成功编写了一个helloworld的cgi,算是cgi入门的第一步. ...

- 阶段5 3.微服务项目【学成在线】_day09 课程预览 Eureka Feign_17-课程预览功能开发-前后端测试

启动前端代码 前端课程找到课程的发布页面 这样就打开了预览页面 结束

- myeclipse启动的过程中没提示就自动退出,闪退的有效解决方法

今天遇到一个问题,已经打开myeclipse的电脑因为非正常关机后myeclipse打不开了,进度条进到十分之一就闪退,什么提示都没有的解决方案如下: 1.打开myeclipse工作空间(存放项目 ...

- PAT 甲级 1054 The Dominant Color (20 分)(简单题)

1054 The Dominant Color (20 分) Behind the scenes in the computer's memory, color is always talked ...

- (转)Flink简介

1. Flink的引入 这几年大数据的飞速发展,出现了很多热门的开源社区,其中著名的有 Hadoop.Storm,以及后来的 Spark,他们都有着各自专注的应用场景.Spark 掀开了内存计算的先河 ...

- C# 后台POST和GET 获取数据

C# 后台POST和GET 获取数据 , data.Length); newStream.Close(); HttpWebResponse myResponse = (HttpWebR ...