基于INTEL FPGA硬浮点DSP实现卷积运算

概述

卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波。而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络。本参考设计主要介绍如何基于INTEL 硬浮点的DSP Block实现32位单精度浮点的卷积运算,而针对定点及低精度的浮点运算,则需要对硬浮点DSP Block进行相应的替换即可。

原理分析

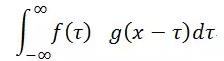

设:f(x), g(x)是两个可积函数,作积分:

随着x的不同取值,该积分定义了一个新的函数h(x),称为函数f(x)与g(x)的卷积,记为h(x)=f(x)*g(x)。

如果卷积的变量是序列x(n)和h(n),则卷积的结果为

其中*表示卷积。因此两个序列的卷积,实际上就是多项式的乘法,用个例子说明其工作原理。a = [7,5,4]; b = [6,7,9];则实现a和b的卷积,就是把a和b作为一个多项式的系数,按多项式的升幂或降幂排列,即为:

因此得到a*b=[42,79,122,73,36];与Matlab运算结果一致。而二维卷积可以采用通用多项式乘积方法实现卷积运算。

基于INTEL FPGA的实现分析

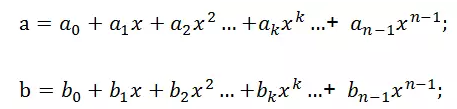

如上我们确定了两个序列的卷积等同于两个多项式的乘法,因此当我们需要计算序列[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果时,可以成立a,b两个n阶多项式,如下所示:

则[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果即为由a*b得到的多项式的各项系数所组成的序列。令c=a*b,得到

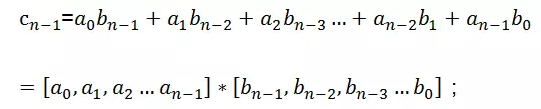

则由多项式c的各阶系数所组成的新的序列[c0,c1,c2, …,c2n-1]即为[a0,a1,a2, …,an-1]与[b0,b1,b2, …,bn-1]的卷积结果。则按照高阶多项式计算展开可得到:

┆┆

┆┆

因此卷积的运算可以转化为行向量与列向量相乘的结果,即乘累加的运算结构。

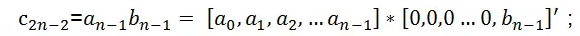

Intel FPGA在Arria10DSP Block中首次支持了单精度硬浮点DSP block,是行业内第一个支持单精度DSP block,硬浮点DSP block架构如图1所示:

图1 硬浮点DSPblock架构

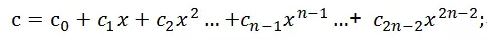

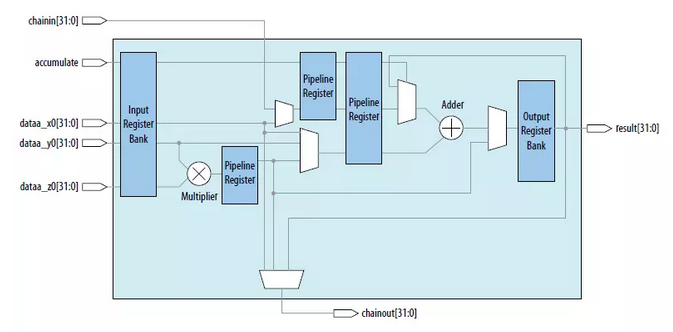

硬浮点DSP Block包含硬浮点乘法器,硬浮点加法器,支持乘累加运算,因此采用硬浮点DSPblock实现行列向量相乘是非常好的方式。下面我们针对一个实际的卷积运算,介绍如何基于INTEL硬浮点DSP block实现。假设我们需要求随机数组a=[4,8,9,11]与b=[10,5,7,13]的卷积运算结果,则根据上面的分析,保持数组a顺序不变,而数组b需根据上述分析结果,针对每一个卷积结果产生新的序列。所以整个实现包括数列重组模块和硬浮点乘法器模块及输出处理。下面是实现框图及仿真结果。

图2 实现框图

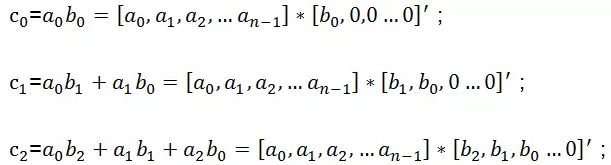

图3 Modelsim仿真结果

仿真结果与Matlab实现结果一致,并且该设计中充分考虑了FPGA并行扩展特性,对于低速率要求的设计可采用DSP Block复用的方式节约DSP block数量。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

基于INTEL FPGA硬浮点DSP实现卷积运算的更多相关文章

- 关于INTEL FPGA设计工具DSP Builder

一段时间以来,MathWorks一直主张使用Matlab和Simulink开发工具进行基于模型的设计,因为好的设计技术使您能够在更短的时间内开发更高质量的复杂软件.基于模块的设计采用了数学和可视化的方 ...

- OpenCL设计优化(基于Intel FPGA SDK for OpenCL)

1.首先了解Intel FPGA SDK for OpenCL实现OpenCL的设计组件,包括: kernels, global memory interconnect, local memory, ...

- Intel FPGA Clock Region概念以及用法

目录 Intel FPGA 的Clock Region概念 Intel 不同系列FPGA 的Clock Region 1. Clock Region Assignments in Intel Stra ...

- TI科学家谈浮点DSP未来发展

自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案.不过,定点器件至今仍是业界的主流.当然低成本是主要原因.定点DSP每器件产品的价格很低,这对大规 ...

- 基于Intel x86 Android的RAD游戏开发

zip文件还包含编译的"MonkeyGame-debug".可以在模拟器中运行的二进制文件.在"game.build"文件夹中有一个HTML5 build.在C ...

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- ARMCC和GCC编译ARM代码的软浮点和硬浮点问题 【转】

转自:http://houh-1984.blog.163.com/blog/static/31127834201211112129167/ 本文介绍了ARM代码编译时的软浮点(soft-float)和 ...

- ARMCC和GCC编译ARM代码的软浮点和硬浮点问题【转】

转自:https://blog.csdn.net/hunanchenxingyu/article/details/47003279 本文介绍了ARM代码编译时的软浮点(soft-float)和硬浮点( ...

- 基于FPGA的光口通信开发案例|基于Kintex-7 FPGA SFP+光口的10G UDP网络通信开发案例

前言 自著名华人物理学家高锟先生提出"光传输理论",实用化的光纤传输产品始于1976年,经历了PDH→SDH→DWDM→ASON→MSTP的发展历程.本世纪初期,ASON/OADM ...

随机推荐

- 012PHP基础知识——运算符(五)

<?php /** * 运算符的短路: * && 逻辑与 || 逻辑或 存在短路: */ /* $a = 1; $a==1 ||$c=100; //逻辑或:第一个表达式返回tru ...

- hdu4309

题解: 暴力枚举 然后网络流 代码: #include<iostream> #include<cstdio> #include<cstring> using nam ...

- 重置input checked

<!-- 作者:duke 时间:2018-10-24 描述: 重置input 样式--> <!DOCTYPE HTML><html> <head> &l ...

- 消除浏览器对input输入框的自动填充

Mozilla官方文档建议的是 直接使用 autocomplete = ‘off’ 即可禁止输入框从浏览器cache获取数据,博主以前使用这个也就足够兼容浏览器了. 现在发现,却在chrome.fir ...

- 2017-2018-2 20165202 实验三《敏捷开发与XP实践》实验报告

一.实验报告封面 二.实验内容 XP基础 XP核心实践 相关工具 三.实验步骤 (一)格式化代码 实验要求: 在IDEA中使用工具(Code->Reformate Code)把下面代码重新格式化 ...

- Golang的简明安装指南

引言: Go language现在是大名鼎鼎,很多的开源项目都是基于go来做的,比如codis, ethereum等都用到了go lang,所以免不了要使用这个东东,本文将简明介绍安装步骤以及环境变量 ...

- linux环境搭建记录

第一次搭建环境,部署服务,在此记录一下过程 1.项目用到的hosts设置好 2.mkdir data,在data文件夹下建server,log,soft,resource路径,上载jdk.zip到so ...

- python对文件的读写

文件 File 什么是文件 文件是用于数据存储和单位 文件通常用来长期存储数据 文件中的数据是以字节为单位进行顺序存储的 文件的操作流程: 1. 打开文件 2. 读/写文件 3. 关闭文件 注: 任何 ...

- nodejs调用百度统计api摆脱人肉数据统计

var http = require("https"); var url = require('url'); var postData = JSON.stringify( { &q ...

- 10day1

但愿复赛的时候旁边坐的不是学军镇海杭二绍一的众神犇. 阅览室 模拟 [问题描述] 一个阅览室每天都要接待大批读者.阅览室开门时间是 0,关门时间是 T.每位读者的到达时间都 不一样,并且想要阅读的 ...