SignalTap ii的使用

1、实现原理

SignalTap II获取实时数据的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以预先设定的时钟采样实时数据,并存储于FPGA片上ram资源中,然后通过JTAG传送回Quartus II分析。可见SignalTap II,其实也是在工程额外加入了模块来采集信号,所以使用SignalTap II需要一定的代价,首先是ELA,其次是ram,如果, 工程中剩余的ram资源比较充足,则SignalTap II 一次可以采集较多的数据,相应的如果FPGA资源已被工程耗尽则无法使用SignalTap II调试。

2、创建STP文件

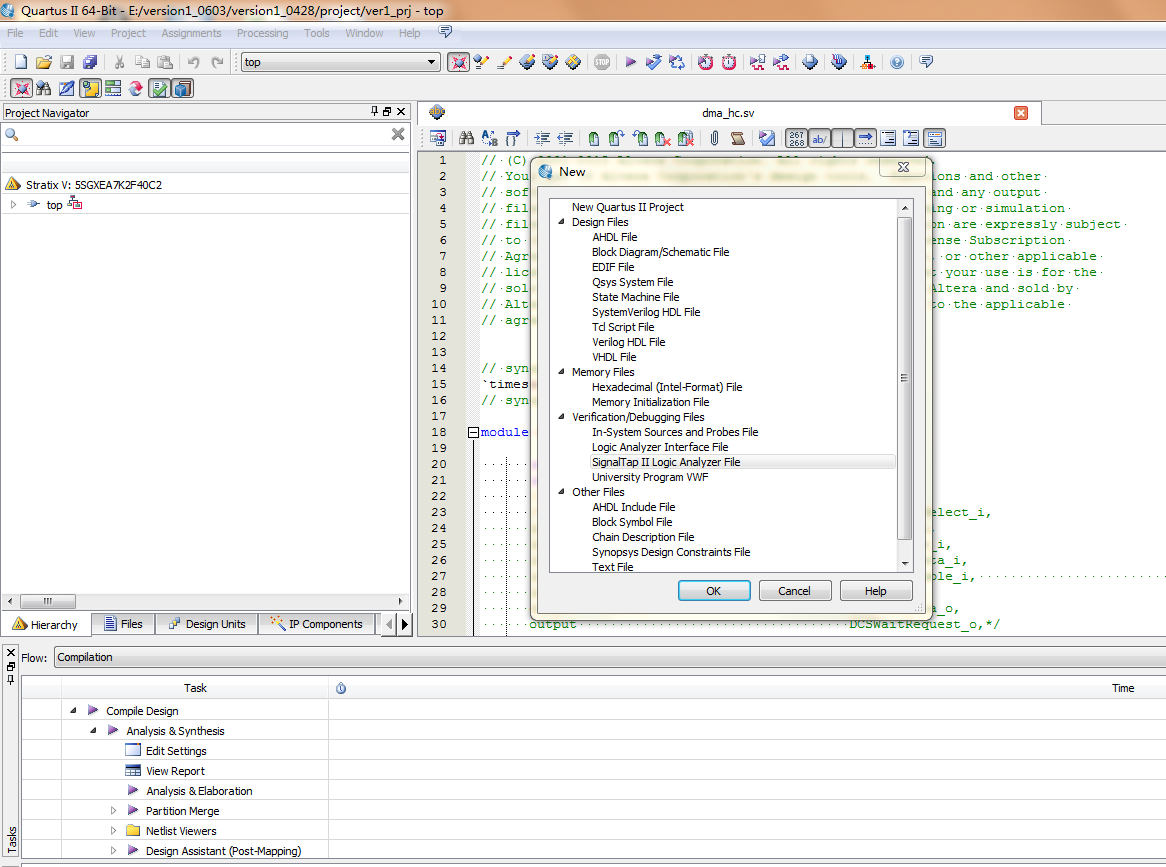

在quartus界面中点击file,选中new,弹出下面框:

选中SignalTap II Logic A nalyzer File点击OK,弹出下面框:

3、在STP文件中添加实例(instance)

添加方法:在上图中的instance窗口中点击右键,选择create instance。

默认情况下,STP中有一个默认名为auto_signaltap_0的instance,双击auto_signaltap_0可以修改为自己定义的名字

4、在instance中添加观测节点(nodes)

点击Edit,选中Add Nodes...(此处有一个需要注意的:上面的步骤必须在打开一个工程后操作,否则Edit中的Add Nodes...将会是灰色,无法选中) ,然后弹出:

这个时候就需要添加你所需要抓取的信号。Look in中选择抓取的信号所在的模块,Filter修改为:

SignalTap II:pre-synthesis,在Named中输入所需抓取的信号名,点击List,在Nodes Found中就会出现该信号,双击该信号,该信号就会出现在Selected Nodes里面。同样在Named中输入另外需要抓取的信号,使之出现在Selected Nodes里面。添加完所有的信号后,点击OK。

5、为instance添加采样时钟

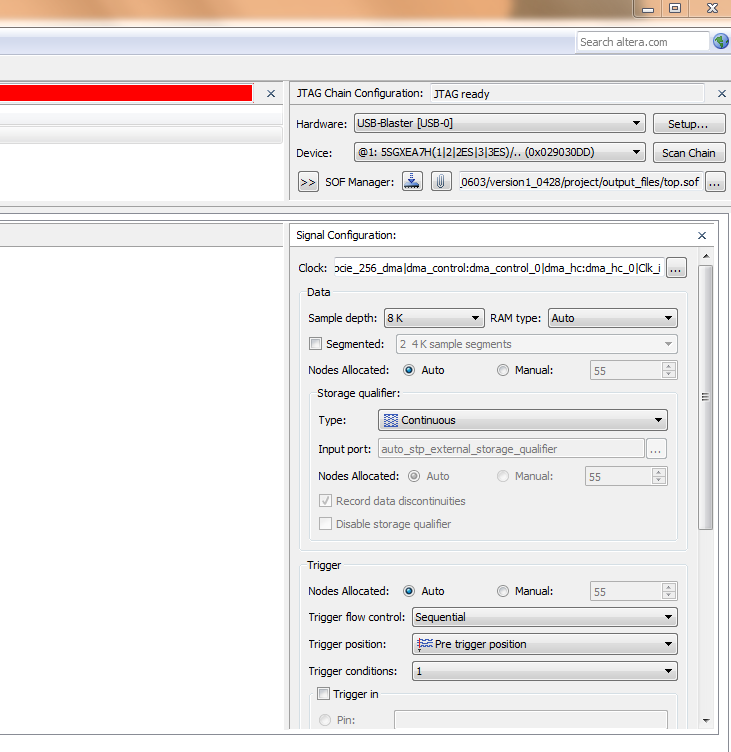

点击软件中下部的Setup按键,在右边会出现:

点击上图的clk旁边的[...]将会弹出与上面一样的Noder Finder窗口,选择好合适的时钟信号。然后设置一些基本的参数:

采样深度,Sample depth 个人建议选大些,但是又不能超过FPGA资源,不然在后面的编译会报错。

RAM类型,这个默认为auto,不用管

触发,Trigger 这个在初期使用signal tap就选择默认,后期可以根据具体信号波形来设置。

6、重新编译添加了signal tap工程

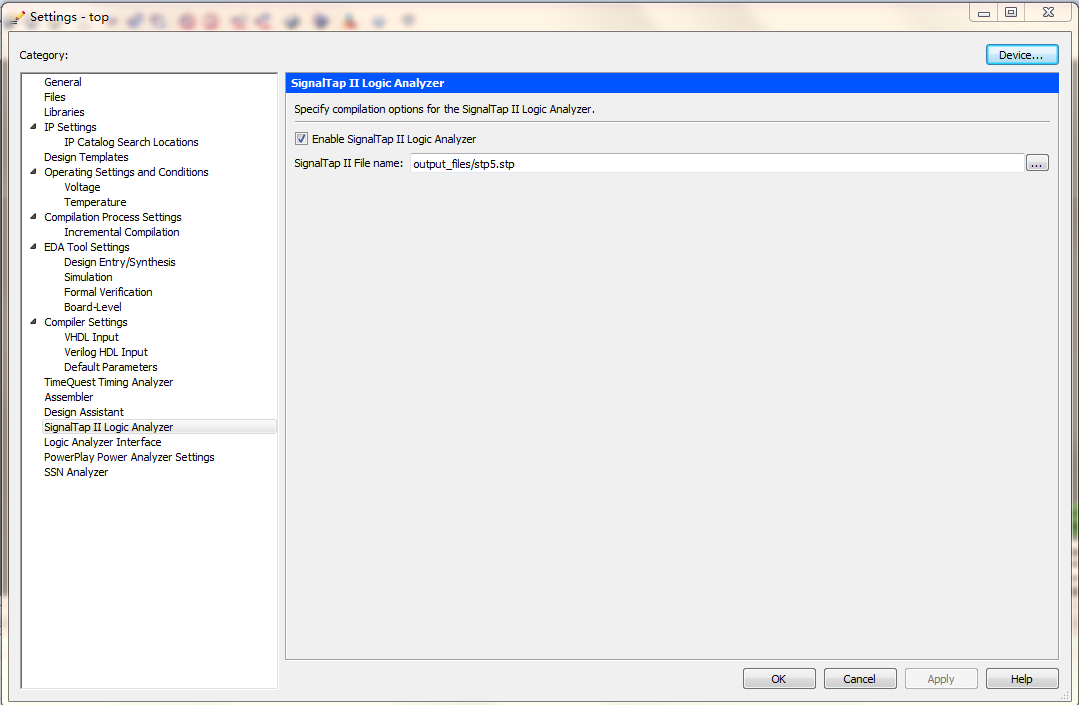

在quartus10.1中一般在上面的步骤都做好后,关闭signal tap窗口一直点击OK就行。为了确保工程中的确添加了我们刚刚新建的stp文件,可以打开工程,选中Entity中的顶层,右键点击settings,就会出现:

7、编译和下载代码

按照一般的方法,编译和生成sof文件。下载代码需要在SignalTap II 中下载,双击stp文件,就会弹出:

点击右上角的SOF Manager后面的[...],选择好刚刚生成的SOF文件,然后点击program device。

8、抓取数据,观测波形

在下载好sof后,点击Instance Manager旁边的run analyzer(也就是红色的三角标志),就可以观察波行了。

转载自:http://www.eefocus.com/zh880813/blog/16-06/385441_3c219.html

SignalTap ii的使用的更多相关文章

- SignalTap II逻辑分析仪的使用

一.例子 我们使用如图1所示的verilog代码所实现的开关电路作为例子.这个电路把DE系列开发板上的前8个开关简单的和对应的8个红色LED相连接.它是这样工作的:在时钟(CLOCK_50)的上升沿读 ...

- SignalTap II应用小实例之触发位置

概述 SignalTap II一直以来都是笔者调试Altera FPGA设计的利器,最近比较有时间静下心来研究SignalTap II某些细节,虽然笔者有过不少关于SignalTap的使用,且也发表过 ...

- Quartus prime 16.0 signaltap II 使用

前言 由于逻辑分析仪太贵,altera贴心提供signal tap II来观察输出波形,不过使能signaltap II会占用片内ram,毕竟原理就是把数据采样到ram中再通过jtag口上传到quar ...

- 如何使用SignalTap II觀察reg與wire值? (SOC) (Verilog) (Quartus II) (SignalTap II)

Abstract撰寫Verilog時,雖然每個module都會先用ModelSim或Quartus II自帶的simulator仿真過,但真的將每個module合併時,一些不可預期的『run-time ...

- 【黑金原创教程】 FPGA那些事儿 SignalTap II 调试技巧

简介工具篇系列的第三本教程,讲述各种与SignalTap II 有关的调试技巧. 目录[黑金原创教程] FPGA那些事儿<工具篇III>:File01 - 上线调试与下线调试[黑金原创教程 ...

- 从SignalTap II中获取“最真实”的仿真测试向量(ZZ)

在实际工作中,经常会遇到这样的情况:在硬件调试中采用SignalTap II反复多次编译并最终捕获到问题的原因时,才会发现,原来这个问题是逻辑问题,是可以在仿真环境下发现并快速解决的.先前没 ...

- Altera培训SignalTap II的使用--笔记

培训的内容有点多(啰嗦)(笔记为截图) 听课笔记:Altera培训SignalTap II的使用--笔记

- 嵌入式逻辑分析仪SignalTap II 设计范例

Crazy Bingo :嵌入式逻辑分析仪SignalTap II 设计范例 例程下载地址 http://www.cnblogs.com/crazybingo/archive/2011/07/26/ ...

- SignalTap II Logic Analyzer 无法观测到信号?

在Quartus SignalTap 工具中加入信号,发现加入的信号变成红色,如图所示的data_slave[7..0]: 这样的信号是没有办法观测的,不会根据SignalTap 的Clock和Tri ...

随机推荐

- Appium+python自动化15-在Mac上环境搭建

前言 mac上搭建appium+python的环境还是有点复杂的,需要准备的软件 1.nodejs 2.npm 3.cnpm 4.appium 5.pip 6.Appium-Python-Client ...

- iOS: FFmpeg的使用二

1.下载并编译FFMPEG. https://github.com/kewlbear/FFmpeg-iOS-build-script 下载后有一个build-ffmpeg.sh文件.终端执行即可自动下 ...

- Power Desginer系列02【转载】

在概念模型中主要有以下几个操作和设置的对象:实体(Entity).实体属性 (Attribute).实体标识(Identifiers).关系(Relationship).继承(Inheritance) ...

- jquery选择div下的ul下的li下的a

使用jQuery选择器: $("div#div的id ul li a")//选择的是div下 ul下所有li下的所有a标签 $("div#div的id").ch ...

- Servlet学习笔记(二):表单数据

很多情况下,需要传递一些信息,从浏览器到 Web 服务器,最终到后台程序.浏览器使用两种方法可将这些信息传递到 Web 服务器,分别为 GET 方法和 POST 方法. 1.GET 方法:GET 方法 ...

- SQL INNER JOIN

A INNER JOIN command is queries that combine data from more than 1 table.For two tables that want to ...

- hadoop中实现定制Writable类

Hadoop中有一套Writable实现可以满足大部分需求,但是在有些情况下,我们需要根据自己的需要构造一个新的实现,有了定制的Writable,我们就可以完全控制二进制表示和排序顺序. 为了演示如何 ...

- [Python爬虫] 之八:Selenium +phantomjs抓取微博数据

基本思路:在登录状态下,打开首页,利用高级搜索框输入需要查询的条件,点击搜索链接进行搜索.如果数据有多页,每页数据是20条件,读取页数 然后循环页数,对每页数据进行抓取数据. 在实践过程中发现一个问题 ...

- Qt正则表达式提取数据

这几天在上嵌入式课程设计,需要用到Qt,这个是信号与槽的,寒假的时候也简单学习了一些,但是没有怎么深入,又回过来看了看Qt,发现Qt的ui界面配置与Android的好像,当然Qt也可以拿来开发Andr ...

- 如何在CentOS 7中添加新磁盘而不用重启系统

导读 对大多数系统管理员来说扩充 Linux 服务器的磁盘空间是日常的工作之一.因此这篇文章会通过使用 Linux 命令,在 CentOS 7 系统上演示一些简单的操作步骤来扩充您的磁盘空间而不需要重 ...