FPGA VGA时序的理解

最近在做FPGA毕业设计,毕业设计规划的是摄像头采集图像,经过均值滤波,中值滤波,高斯滤波,然后通过VGA接口控制显示器显示出来,所以最近学习了一下FPGA的VGA驱动的相关内容。

VGA接口

如上图所示,VGA接口一共15针,分为3*5。

主要使用的信号线是上面的5根线,行同步信号,场同步信号和R,G,B基色的模拟信号。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

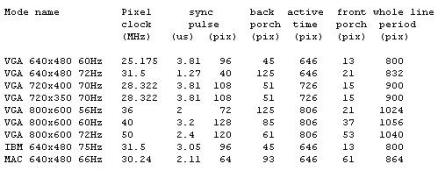

VGA水平扫描时序

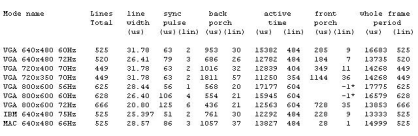

VGA垂直扫描时序

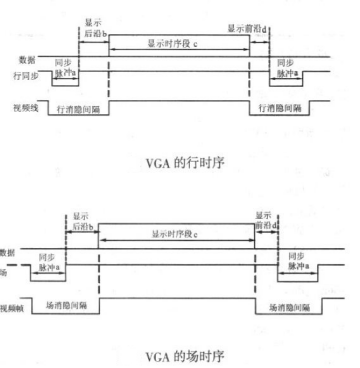

VGA时序图

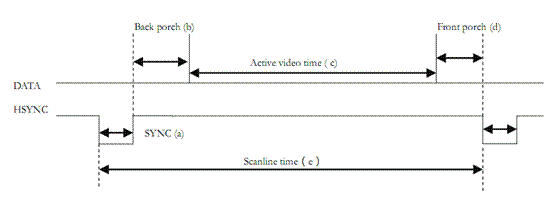

如上图VGA显示时序所示,VGA每次显示都需要同步信号,经过同步脉冲a,显示后沿b,显示时序段c,显示前沿d,然后是同步脉冲a,这样一个循环。

根据VGA协议标准,以640*480 60HZ为例,每秒钟要显示60次,一次显示800*525个点,其中640*480为显示时序段的有效点,其他的是为了同步时序的无效点。

如下图所示黄色区域为800个点的行周期,红色区域为525个点的场周期,只有行周期和场周期同时有效的橘色区域640*480才是有效显示区域。

VGA时序分析

一秒钟需要显示800*525*60个点,而时序的时钟频率是25MHZ,所以显示一个点的时间是25M/(800*525*60)=40ns.

行时序如上图所示:

a段的持续时间是96*40ns

b段的持续时间是45*40ns

c段的持续时间是646*40ns

d段的持续时间是13*40ns

e段的持续时间是800*40ns(e段是整个行周期)

场时序如上图所示:

o段的持续时间是2*e

p段的持续时间是30*e

q段的持续时间是484*e

r段的持续时间是9*e

S段的持续时间是528*e

只有行时序处于c段和场时序处于q段的时候发送的才是有效数据,一个行周期要显示640个点,一个场周期要显示480个行。

代码如下,代码只实现了VGA时序,时钟默认25MHZ。需要进一步修改。

- module vga_driver(

- clk ,

- rst_n ,

- din ,

- vga_hys ,

- vga_vys ,

- vga_rgb

- );

- parameter DATA_W = 16;

- input clk ;

- input rst_n ;

- input din ;

- output vga_hys ;

- output vga_vys ;

- output [DATA_W-1:0] vga_rgb ;

- reg vga_hys;

- reg vga_vys;

- reg [DATA_W-1:0] vga_rgb;

- reg [9:0] cnt_hys;

- reg [9:0] cnt_vys;

- wire add_cnt_hys;

- wire end_cnt_hys;

- wire add_cnt_vys;

- wire end_cnt_vys;

- reg display_area;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_hys <= 0;

- end

- else if(add_cnt_hys)begin

- if(end_cnt_hys)

- cnt_hys <= 0;

- else

- cnt_hys <= cnt_hys + 1;

- end

- end

- assign add_cnt_hys = 1;

- assign end_cnt_hys = add_cnt_hys && cnt_hys== 800-1;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_vys <= 0;

- end

- else if(add_cnt_vys)begin

- if(end_cnt_vys)

- cnt_vys <= 0;

- else

- cnt_vys <= cnt_vys + 1;

- end

- end

- assign add_cnt_vys = end_cnt_hys;

- assign end_cnt_vys = add_cnt_vys && cnt_vys==525-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_hys <= 0;

- end

- else if(add_cnt_hys && cnt_hys == 96-1)begin

- vga_hys <= 1;

- end

- else if(end_cnt_hys)begin

- vga_hys <= 0;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_vys <= 0;

- end

- else if(add_cnt_vys && cnt_vys == 2-1)begin

- vga_vys <= 1;

- end

- else if(end_cnt_vys)begin

- vga_vys <= 0;

- end

- end

- always @(*)begin

- display_area = cnt_hys >= 141 && cnt_hys <= (141+646) && cnt_vys >= 32 && cnt_vys < (32+484);

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_rgb <= 0;

- end

- else if(display_area)

- begin

- vga_rgb <= din;

- end

- else begin

- vga_rgb <= 0;

- end

- end

- endmodule

FPGA VGA时序的理解的更多相关文章

- 图像处理算法的仿真平台之VGA时序

一 概述 图像处理算法一般是用matla或OpenCV实现的,若是用FPGA实现,设计思路差别极大.matlab和opencv的优势:这些工具的优势在于可以方便地载入图像文件,或输出数据到图像文件, ...

- 【转载】VGA时序与原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- VGA 时序标准

VGA 显示器扫描方式从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步:当扫描完所有的行 ...

- VGA时序及其原理(转载)

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA时序约束理解记录

最近整理了一下时序约束的内容,顺便发出来分享记录一下. 任何硬件想要工作正常,均需满足建立和保持时间,至于这个概念不再陈述. 下面将重点介绍两个概念:建立余量和保持余量.FPGA内部进行时序分析无非就 ...

- fpga vga 显示

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高.显示速率快.颜色丰富等优点,在彩色显示器领域得到了广泛的应用.不支持热插拔, ...

- 【转】 VGA时序及其原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- 每天进步一点点------FPGA 静态时序分析模型——reg2reg

2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满 ...

随机推荐

- U-Boot Driver Model领域模型设计 (转)

需求分析 在2014年以前,uboot没有一种类似于linux kernel的设备驱动模型,随着uboot支持的设备越来越多,其一直受到如下问题困扰: 设备初始化流程都独立实现,而且为了集成到系统,需 ...

- noi.ac NA531 【神树和物品】

今日成就:本来以为过了这题,然后被mcfx发现写假并针对地造了一组hack数据之后FST了. 复杂度什么的咱也不会证,咱也不会卡,被hack之后只能FST. 是个决策单调性sb题,但是由于太菜不怎么会 ...

- 我说CMMI之二:CMMI里有什么?--转载

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明.本文链接:https://blog.csdn.net/dylanren/article/deta ...

- 使用Nginx的proxy_cache缓存功能取代Squid[原创]

使用Nginx的proxy_cache缓存功能取代Squid[原创] [文章作者:张宴 本文版本:v1.2 最后修改:2009.01.12 转载请注明原文链接:http://blog.zyan.cc/ ...

- JAVA学长

https://www.cnblogs.com/chenmingjun/p/9697371.html

- 2018中国大学生程序设计竞赛 - 网络选拔赛 Find Integer

Find Integer Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/65536 K (Java/Others) Tot ...

- PyQT5堆叠布局:切换界面(QStackedLayout)

几乎所有的GUI界面都需要用到这个场景:在一个界面里面,点击不同的按钮显示不同的内容 在Qt设计师中没有堆叠布局,需要我们手动添加 在Qt设计师中,设计3个切换的页面,和一个主界面. 注意在主界面是两 ...

- R_Studio(聚类)针对iris数据比较几种聚类方法优劣

聚类分析 百度百科:传送门 聚类分析指将物理或抽象对象的集合分组为由类似的对象组成的多个类的分析过程 聚类与分类的不同在于,聚类所要求划分的类是未知的 聚类分析是一种探索性的分析,在分类的过程中,人们 ...

- win7,win10 系统上搭建testlink1.9.18环境实操步骤

Windows7,10系统上安装TestLink1.9.18(基于xampp) 写于:2018.11.28 二次排版微调:2019.01.01 如遇本文资料缺失,可点击百度网盘查看原始资料. 链接:h ...

- Mongo Cursor

简介 在使用 Java 对数据库进行连接时,都会获取到一个 cursor ,cursor 实际指到的是我们查询数据库的query,而并不是 query 查询到的数据集. 此次在使用 mongo 的 c ...