旁路电容的PCB布局布线透彻详解(4)

前面使用了较多的篇幅介绍旁路电容的工作原理及其选择依据,我们已经能够为电路系统中相应的数字集成芯片选择合适的旁路电容,在实际应用过程中,旁路电容的PCB布局布线也会影响到高频噪声旁路功能的充分发挥,下面我们介绍旁路电容在PCB布局布线过程中应该注意的一些事项。

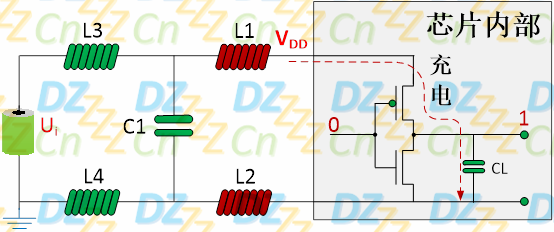

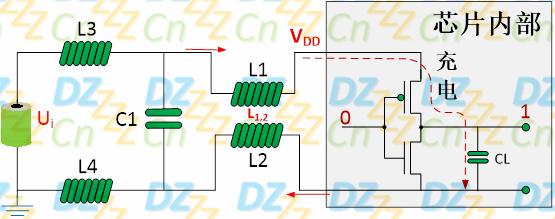

我们已经对旁路电容在高频工作下的等效电路及其原理作了一番介绍,其等效电路如下图所示:

其中,C1就是为芯片配备的旁路电容,L1、L2、L3、L4就是线路(包括过孔、引脚、走线等)在高频下的等效分布电感,这些分布电感对于高频信号相当于是高阻抗,这对于前级过来的高频干扰的抑制是有好处的,但同时对芯片内部(后级)开关切换带来的干扰也是有抑制作用的,这种抑制作用在旁路电容(或更远的直流电源V)与芯片之间形成了阻碍,使得VDD供电端子无法在及时获取到足够电荷继而导致VDD瞬间下降(即变差)。

为了使旁路电容能够最大限度地发挥高频噪声旁路的作用,我们在进行PCB布局布线时应遵循一个基本原则:使旁路电容与芯片之间的分布电感(L1、L2)尽可能减小。

PCB走线电感的计算公式如下:

其中,L表示走线长度,W为走线宽度,走线宽度W越宽,长度L越小,则PCB走线分布电感越小,从公式中可以看出,PCB走线分布电感随走线长度几乎同比例变化(PCB走线长度减少50%,相应的电感也将减少50%),但走线宽度必须增加10倍才能减少50%的电感。

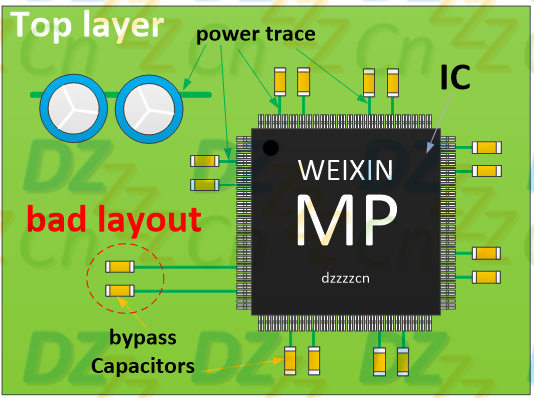

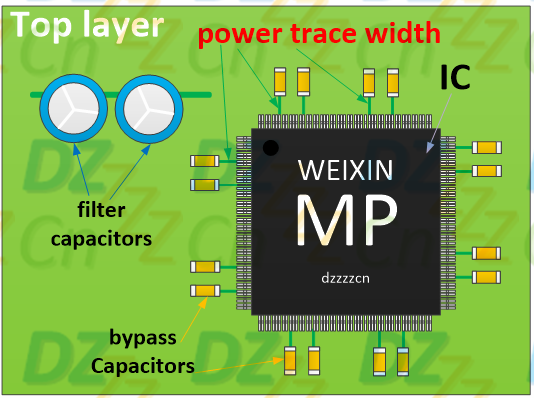

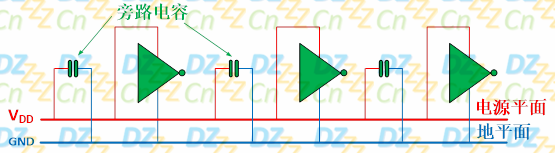

因此,减小走线分布电感最直观最有效的布线措施之一就是:尽量缩短旁路电容与芯片之间的走线长度,这也是为什么我们通常都要求将旁路电容与芯片尽可能靠近的道理,如下图所示:

将旁路电容尽量靠近芯片获得的另一个附加好处是:可以使高频噪声的回流路径最小化,换言之,可以限制芯片(噪声)电流流过的范围(不至于干扰电路系统的其它部分),如下图所示:

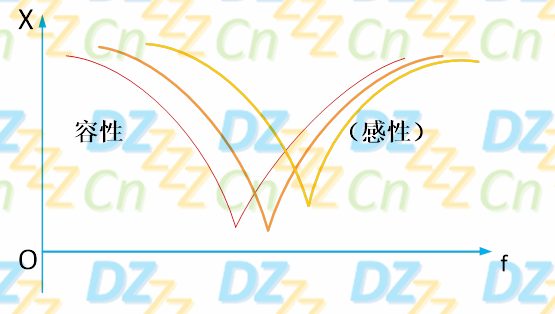

很多场合下,芯片产生出来的高频噪声频率范围比较宽,仅仅使用一种容量的旁路电容将无法有效削弱多种频率的叠加强噪声,这时我们可以使用多个不同容量的旁路电容并联在一起,以获取较宽频率范围内的低阻抗,这样得到的阻抗曲线如下图所示:

由于不同容量的旁路电容有不同的自谐振频率(在同等条件下,容量越小,则自谐振频率越高,前面已经讲解过,此处不再赘述),多个不同容量的旁路电容并联时,可以在更宽的频率范围内表现出对高频噪声的低阻抗。

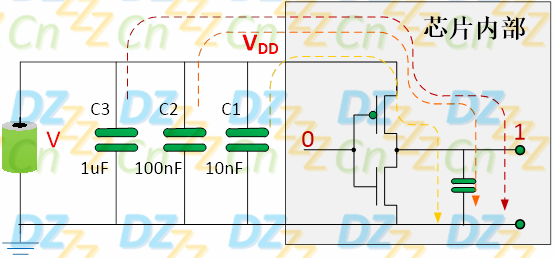

多个旁路电容并联方案在PCB中布局的基本原则是:容量越小的旁路电容则越靠近芯片,其基本布局示意图如所示:

通常频率越高的噪声电流成分,对电路稳定性的潜在威胁更大,因此,我们将容量最小的旁路电容最靠近芯片,使得频率最高的噪声回流路径是最小的,这样多种频率不同噪声电流环路面积均可通过各自合适的旁路电容而被限制,如下图所示:

其次,尽量加粗旁路电容与芯片之间电源与地的走线。虽然从PCB走线电感公式中可以看出走线宽度加粗的效果并不如走线长度缩短那么明显,但聊胜于无,饿的时候有块馒头啃啃也不错呀,其基本示意图如下所示:

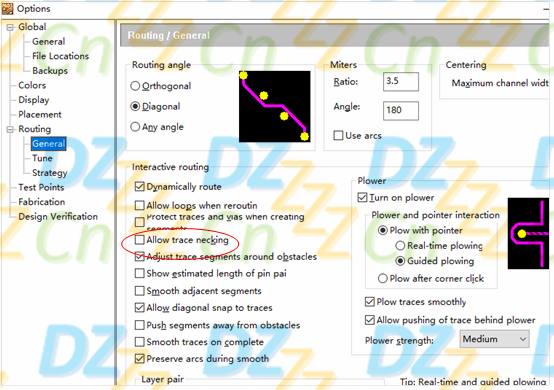

很多大规模集成芯片的引脚很密(引脚间距Pitch小),如果直接用较宽走线拉出来,PCB绘图软件可能会报规则冲突(通常在PCB布线时都是将设计规则检查DRC打开),换言之,走线无法从引脚中拉出来,如下图所示:

这时我们可以先从芯片引脚拉出一段比较窄的走线,布出一段后再进行走线加粗。有些PCB 绘图软件为方便此类网络的PCB布线,对此有一些特殊的设置,下图所示为PADS Router中走线选项设置对话框:

上图中的选项“Allow trace necking”用来设置:在布线时,可否根据情况调整线宽的大小。

在实际布线时,勾选此项与否的影响如下图所示:

我们将默认走线宽度设置为200mil(5.08mm),如果就这样从芯片的引脚开始布线,则由于芯片引脚本身的间距小于200mil,则会提示“Cant exit a pin/via with trace with 200”之类的提示,表示由于设计规则的冲突而无法继续布线,但如果选择了该项,系统会将有冲突的那一段走线自动调整到合适的线宽,随后又按正常的线宽200mil进行布线。

这里我们也有一个问题:在进行旁路电容的PCB布局布线时,是应该先经过旁路电容再进入芯片引脚,还是先进入芯片引脚再进入旁路电容?换言之,是旁路电容优先,还是芯片优先!如下图所示:

有人说:这不明摆着的吗?左边(旁路电容优先)肯定要好一些,右边(芯片优先)那个地网络走线那么长。事实上,对于大多数高速数字PCB板而言,使用的都是地平面与电源平面,通常都是直接打孔到平面层,两者的差距是不大的。

也有人说:滤波电容与旁路电容在电路中起的作用不一样,滤波电容在布线时应该按滤波电容优先的原则,而旁路电容的作用是提供高频回流路径,两种走法并没有多大的不同。

我们假设两种布线方案都采用最短的走线连接,那两种布线方案中的旁路电容的功能发挥是否还有区别呢?我们只要把两者的等效电路画出来就明白孰优孰劣,如下图所示(旁路电容优先):

直流供电电源 Ui经过分布电感L3、L4对C1进行充电,再通过分布电感L1、L2给芯片供电,当供电电源的电压Ui变动时也会引起芯片的开关电流随之变化,因此,旁路电容C1能够起到补偿电荷作用,这与滤波电容的储能原理是完全一致的。

旁路电容优先的方案中,旁路电容的存在使得直流供电电源与芯片实现了高效的分离(去耦),另一方面,虽然分布电感L1与L2对于芯片获取旁路电容中的电荷是有抑制作用的,但对于芯片内部的噪声向外扩散的抑制也有一定的好处,从这个角度来说,分布电感也是有那么一点点的好处。

我们再来看看如下图所示芯片优先布线方案:

如上图所示,由于直流供电电源 Ui与芯片直接相连, 电源电压的变动将直接影响到芯片,尽管旁路电容可以进行起到一定的旁路作用,但芯片与供电电源部分不再是高效的分离状态,而分布电感 L1、L2将对电流噪声的抑制没有任何好处(只有坏处)。

可以看到,旁路电容优先的布线方案相对而言更能够发挥旁路功能,然而我们通常见到的旁路电容的布局如下图所示(芯片优先):

如上图所示,旁路电容放在芯片周围,芯片从电源引脚拉出与旁路电容连接,通常电源走线在芯片下面连接(芯片优先的布线方案),这其实是不得已而为之的,因为芯片与旁路电容在同一板层时,布线时采用旁路电容优先的布线方案不太现实,走线会复杂得多(然而旁路电容在芯片底层布局时却相对比较好实现)。

看来该讲的已经讲完了,然而还没完!每一个从事电子技术行业的工程师都知道,电感有自感与互感两种,前面我们讲的是如何降低自感,而事实上,芯片能否快速获取到旁路电容的电荷量,不仅仅与自感有关,而是与整个环路的总电感有关。

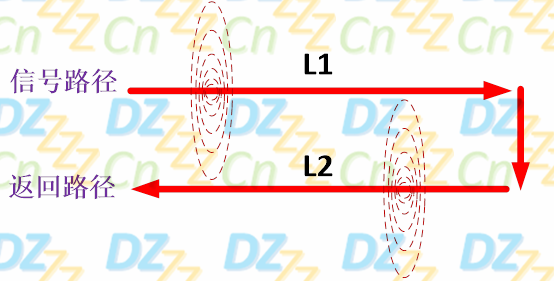

假设信号路径与返回路径的自感如下图所示:

当信号路径与返回路径离得比较远时,我们认为两个路径是没有耦合的,因此环路总电感应为两个路径自感之和(L1+L2),这也是我们前面描述的情况。

然而当两个路径离得较近时,其情况如下图所示:

由于信号路径与返回路径的电流是相反的,因此两者产生的磁场会相互抵消,换言之,两个路径之间有一定的互感L1,2,因此,此时的环路总电感量应为(L1+L2-2L1,2)

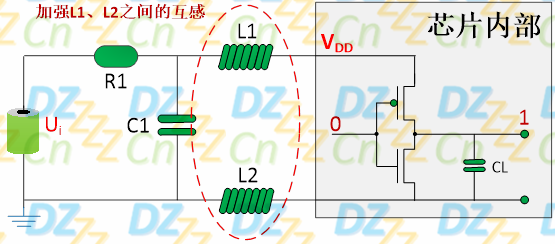

这说明了什么呢?我们前面得到高频条件下的分布电感等效图如下图所示:

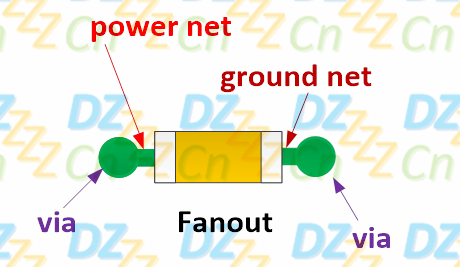

只要我们能将分布电感L1与 L2之间的互感加强,也可以在一定程度上优化旁路电容的功能。在多层PCB板中,我们通常都是将旁路电容的电源与地引脚通过过孔与平面层相连接(特别是很多BGA封装的芯片,旁路电容都是放在芯片的背面)的如下图所示:

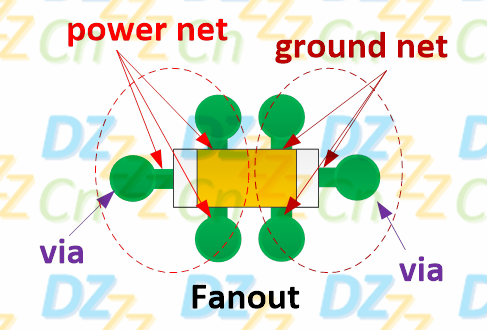

为了降低旁路电容与芯片之间的环路总电感,我们可以采用如下图所示的扇出方案:

上图中,我们增加了2对过孔,并且使电源过孔与地过孔尽可能地接近,同时将同类型过孔之间(电源过孔或地过孔)的距离尽可能拉开,此时电路板的截面就如下图所示:

如此一来,我们前述的旁路电容高频等效电路应如下图所示:

电源过孔与地过孔中流过的电流是相反的,因此,对于旁路电容C1而言,环路总电感应为(L1+L2-2L1,2),比单独使用两个过孔的方案(L1+L2)要小一些,如下图所示:

当然,如果过孔间的中心距大于过孔的长度,那两者之间的互感将非常小。

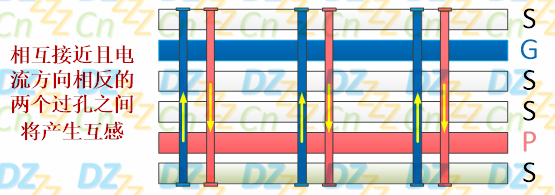

需要注意的是:电流方向相同的过孔不应该靠近,因为那样反而会增加环路电感,如下图所示:

上图中,由于电流方向相同,就算返回路径的自感可以忽略,则总的环路等效电感为(L1+L2+2L1,2),这就是为什么我们之前提到要将同类型电源过孔(或地过孔)之间的距离尽量拉开的原因

我们很容易可以联想到高速数字设计中的多层电路板,电源平面与地平面之间的间隔越小,则两者之间的互感就越大,环路总电感将减小,最终由噪声导致的电压瞬间波动将越小,这也是使用平面层带来的好处之一,如下图所示:

我们通常还遇到一种叫做去耦电容(decoupling capacitor)的玩意儿,它与旁路电容的区别在哪里呢?下面我们来谈谈这个问题。

旁路电容的PCB布局布线透彻详解(4)的更多相关文章

- 透彻详解(3)旁路电容100nF_0.1uF的由来计算

原文地址点击这里: 前一节我们已经详细解释了旁路电容在数字电路系统中所起的基本且重要作用,即储能与为高频噪声电流提供低阻抗路径,尽管还并未给旁路电容的这些功能概括一个"高大上"的名 ...

- oracle游标透彻详解分析

主:本文来自:http://www.cnblogs.com/huyong/archive/2011/05/04/2036377.html 4.1 游标概念 4.1.1 处理显式游标 4.1.2 处理隐 ...

- 为什么PMOS比NMOS的沟道导通电阻大,速度慢,价格高-透彻详解

原文地址点击这里: 在前一节,我们对PMOS与NMOS两种增强型场效应管的开关电路作了详细的介绍, 并且还提到过一种广为流传的说法:相对于NMOS管,PMOS管的沟道导通电阻更大.速度更慢.成本更高等 ...

- EEPROM工作原理透彻详解

原文链接点击这里 EEPROM(Electrically Erasable Programmable read only memory)即电可擦可编程只读存储器,是一种掉电后数据不丢失(不挥发)存储芯 ...

- WiFi天线对PCB布局布线和结构的要求详解 - 全文

随着市场竞争的加剧,硬件设备正以集成化的方向发展.天线也由外置进化内置再进化到嵌入式,我们先来介绍这类应用的天线种类: ⑴ On Board板载式:采用PCB蚀刻一体成型,性能受限,极低成本,应用于蓝 ...

- [转帖]进程状态的转换与PCB详解

进程状态的转换与PCB详解 https://blog.csdn.net/qq_34666857/article/details/102852747 挺好的 之前没好好学习. 返回主目录 之前的 ...

- GDT,LDT,GDTR,LDTR 详解,包你理解透彻(转)

引自:http://www.techbulo.com/708.html 一.引入 保护模式下的段寄存器 由 16位的选择器 与 64位的段描述符寄存器 构成 段描述符寄存器: 存储段描述符 选择器:存 ...

- 用IDEA详解Spring中的IoC和DI(挺透彻的,点进来看看吧)

用IDEA详解Spring中的IoC和DI 一.Spring IoC的基本概念 控制反转(IoC)是一个比较抽象的概念,它主要用来消减计算机程序的耦合问题,是Spring框架的核心.依赖注入(DI)是 ...

- 电容参数:X5R,X7R,Y5V,COG 详解

电容参数:X5R,X7R,Y5V,COG 详解 文章来源:http://www.hzlitai.com.cn/article/ARM9-article/cphard/1777.html 仅供分享学习~ ...

随机推荐

- 在Visual Studio 中使用git——文件管理-下(六)

在Visual Studio 中使用git--什么是Git(一) 在Visual Studio 中使用git--给Visual Studio安装 git插件(二) 在Visual Studio 中使用 ...

- 编译课设·CLion到VS踩坑·解决·备忘录

应试用,VS使用习惯和JB系差别还是蛮大的 打不过他们就加入他们 键位修改 工具-选项 键盘:改keymap 字体和颜色:宋体必改. 自动恢复:自动保存默认3分钟 CMake:自救时可以看一下 键位名 ...

- jquery的入口函数 和 js和jq的转化

先引入jq包 然后<script type="text/javascript"> $(function{ 获取标签:$('#box2') jq转为js:$('#box2 ...

- jenkins邮件报警机制配置

1.下载email插件 Jenkins配置email前需要先安装email插件:Email Extension.Email Extension Template Plugin 2.系统配置 在Jenk ...

- JAVA的基本介绍和JDK的安装

JAVA帝国 JAVA特性和优势 简单 面向对象 可复制性 高性能 分布式 动态性 多线性 安全性 健壮性 JAVA三大版本 javaSE:标准版(桌面程序.控制台开发) javaME(嵌入式开发) ...

- 一、MegaCli命令介绍

一.MegaCli命令介绍 MegaCli是一款管理维护硬件RAID软件,可以用来查看raid信息等MegaCli 的Media Error Count: 0 Other Error Count: 0 ...

- pre -regulator 前端稳压器

regulator

- 1.5linux用户权限相关命令

用户权限相关命令 目标 用户 和 权限 的基本概念 用户管理 终端命令 组管理 终端命令 修改权限 终端命令 01. 用户 和 权限 的基本概念 1.1 基本概念 用户 是 Linux 系统工作中重要 ...

- 9.random_os_sys_shutil_shelve_xml_hashlib

此章未能精读,待回顾random模块import randomrandom.random() 随机生成一个0-1之间随机的浮点数random.randint(a,b) 随机生成一个a-b之间的整数 a ...

- /usr/bin/docker-current: Error response from daemon: oci runtime error: container_linux.go:247: starting container process caused "process_linux.go:245: running exec setns .....

docker创建容器时报错如下: containerd: start container" error="oci runtime error: container_linux.go ...