基于 TI Sitara系列 AM64x核心板——程序自启动说明

前 言

本文主要介绍AM64x的Cortex-A53、Cortex-M4F和Cortex-R5F核心程序自启动使用说明。默认使用AM6442进行测试演示,AM6412测试步骤与之类似。

本说明文档适用开发环境如下:

Windows开发环境:Windows 7 64bit、Windows 10 64bit

虚拟机:VMware15.5.5

Linux开发环境:Ubuntu 18.04.4 64bit

Linux Processor SDK:ti-processor-sdk-linux-rt-am64xx-evm-08.01.00.39

U-Boot:U-Boot-2021.01

CCS版本:CCS11.2.0

MCU+ SDK:mcu_plus_sdk_am64x_08_03_00_18

SysConfig:sysconfig-1.12.1_2446

GCC AARCH64 Compiler:gcc-arm-9.2-2019.12-mingw-w64-i686-aarch64-none-elf

本文测试板卡为创龙科技SOM-TL64x核心板,它是一款基于TI Sitara系列AM64x双核ARM Cortex-A53 + 单/四核Cortex-R5F + 单核Cortex-M4F设计的多核工业级核心板,通过工业级B2B连接器引出5x TSN Ethernet、9x UART、2x CAN-FD、GPMC、PCIe/USB 3.1等接口。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

用户使用核心板进行二次开发时,仅需专注上层运用,降低了开发难度和时间成本,可快速进行产品方案评估与技术预研。

基于SBL引导裸机、FreeRTOS程序启动

程序启动流程说明

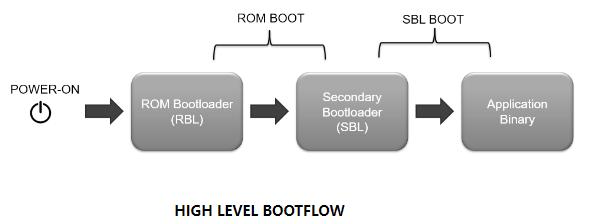

评估板上电后,固化在CPU内部的RBL将会先运行,RBL根据评估板BOOT SET从启动介质(如eMMC,Micro SD、SPI FLASH)读取SBL,然后通过SBL引导应用程序启动。

程序启动流程如下图所示。

图 1

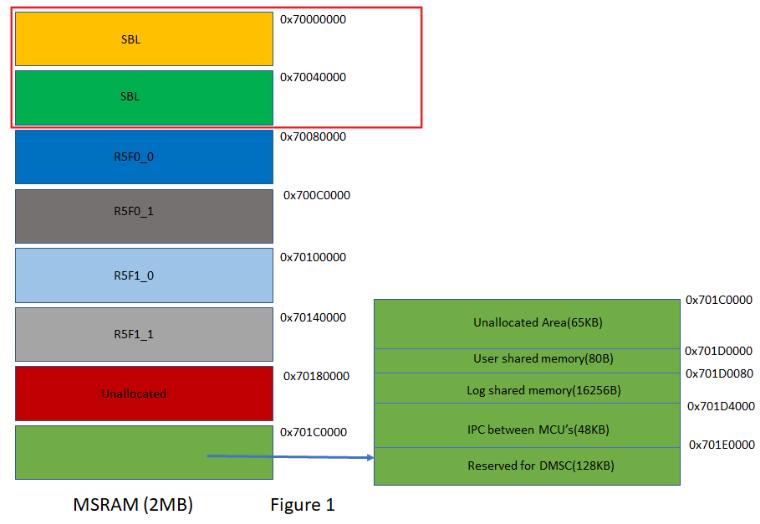

图 1目前官方提供的MCU+ SDK(版本为mcu_plus_sdk_am64x_08_03_00_18),SBL将会先读取应用程序至MSRAM,然后再进行解析。由于MSRAM空间有限,分配给SBL使用的内存空间仅512KByte,并且SBL运行需使用部分MSRAM空间。因此,为确保SBL引导应用程序正常启动,应用程序大小不能超过380KByte。

图 2

基于Micro SD卡启动

启动卡制作

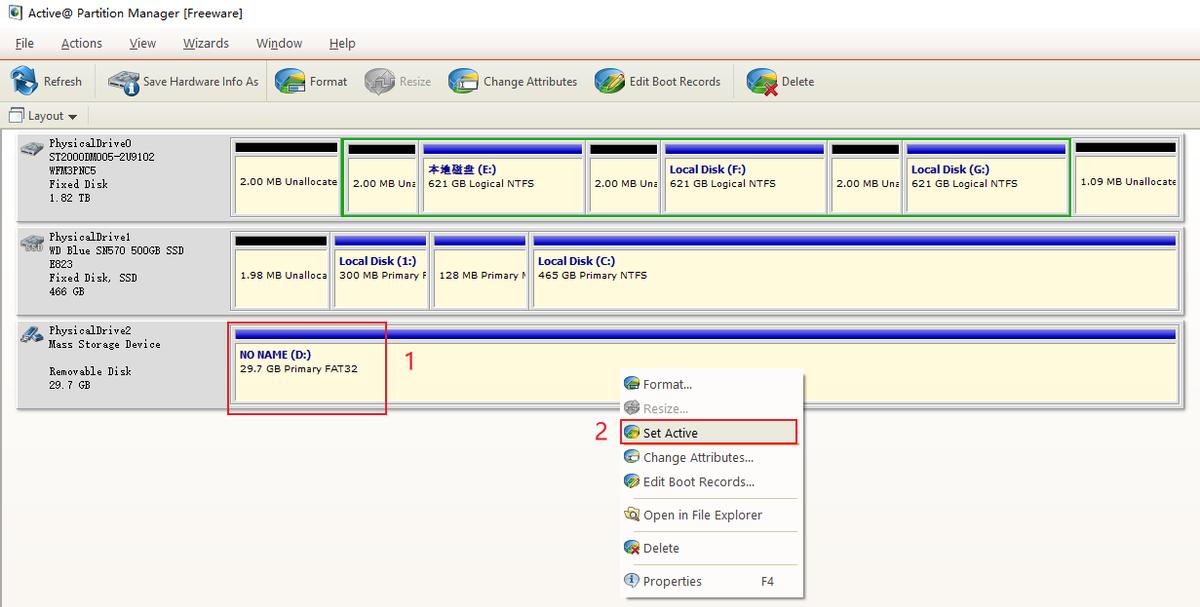

请准备一张FAT32格式的Micro SD卡,通过读卡器将Micro SD卡连接至PC机。

双击产品资料“4-软件资料\Tools\Windows\”目录下PartManFree-Setup.exe分区管理软件,按默认安装即可。安装完成后,打开分区管理软件,将会自动识别到Micro SD卡分区,请右键选中该分区,点击"Set Active"设置为活跃分区,如下图所示。

图 3

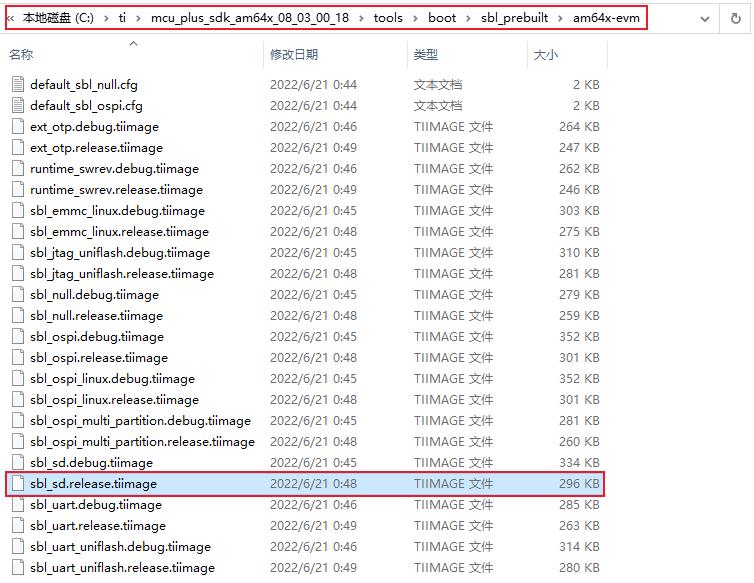

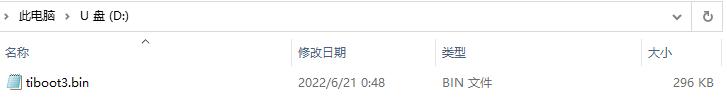

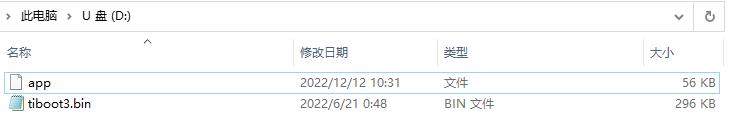

进入MCU+ SDK组件安装目录"C:\ti\mcu_plus_sdk_am64x_08_03_00_18\tools\boot\sbl_prebuilt\am64x-evm\",将sbl_sd.release.tiimage拷贝至Micro SD卡,并重命名为tiboot3.bin,如下图所示。

备注:sbl_sd.release.tiimage为官方提供的SBL镜像。

图 4

图 5

单核启动

本小节以Cortex-A53核心的led_flash裸机工程为例进行演示,Cortex-M4F和Cortex-R5F核心操作步骤与之类似。

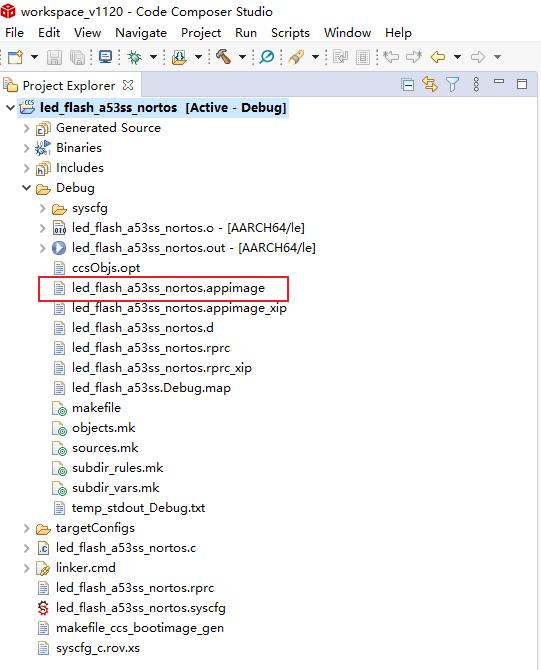

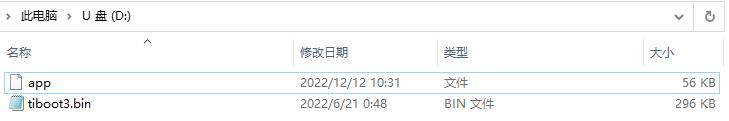

请参考《FreeRTOS、Baremetal案例开发手册》文档,正确编译产品资料“4-软件资料\Demo\Baremetal-demos\led_flash\project\”目录下的led_flash_a53ss_nortos工程,然后将编译生成的led_flash_a53ss_nortos.appimage镜像文件拷贝至Micro SD卡,并重命名为app。

图 6

图 7

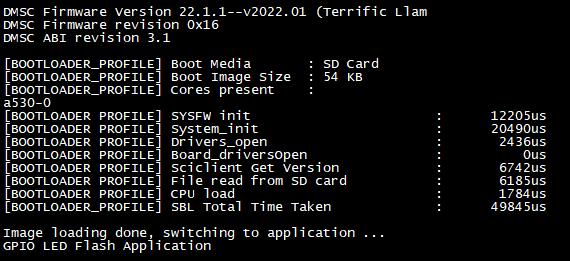

请将Micro SD卡插入评估板Micro SD卡槽,根据评估底板丝印将启动方式选择拨码开关拨为101000(1~6),此档位为Micro SD启动模式。然后使用Micro USB线连接评估板的USB TO UART0调试串口至PC机,

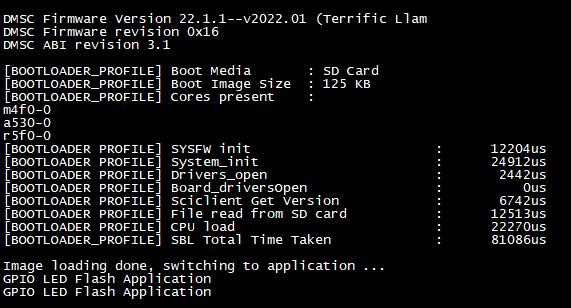

请将评估板上电启动,串口调试终端将会打印如下类似启动信息。同时,可观察到评估底板LED1、LED2闪烁,说明程序自启动成功。

图 8

多核启动

本小节以Cortex-A53、Cortex-M4F和Cortex-R5F核心的led_flash裸机工程为例进行演示。

请在磁盘根目录新建一个非中文文件夹test,将产品资料“4-软件资料\Demo\Baremetal-demos\led_flash\bin\”目录下的led_flash_a53ss_nortos.out、led_flash_m4fss_nortos.out、led_flash_r5fss_nortos.out全部拷贝至该目录下。

图 9

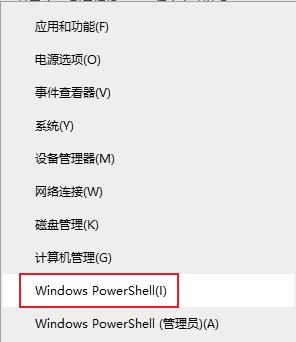

右键Windows按钮,点击"Windows PowerShell(I)",打开Windows PowerShell终端。

图 10

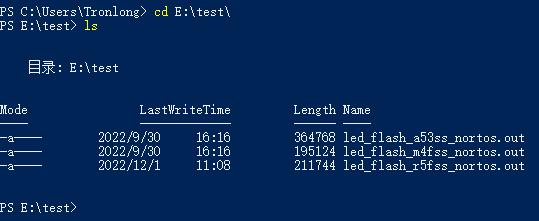

在Windows PowerShell终端执行如下命令进入test目录。

Window# cd E:\test\

图 11

- rprc文件生成

在Windows PowerShell终端执行如下命令,基于xxx.out文件使用CCS和MCU+ SDK生成xxx.rprc文件,xxx.rprc文件已包含可加载段的bin文件。CCS与MCU+ SDK路径请以实际情况为准。

Window# C:\ti\ccs1120\ccs/tools/node/node C:/ti/mcu_plus_sdk_am64x_08_03_00_18/tools/boot/out2rprc/elf2rprc.js led_flash_a53ss_nortos.out

Window# C:\ti\ccs1120\ccs/tools/node/node C:/ti/mcu_plus_sdk_am64x_08_03_00_18/tools/boot/out2rprc/elf2rprc.js led_flash_m4fss_nortos.out

Window# C:\ti\ccs1120\ccs/tools/node/node C:/ti/mcu_plus_sdk_am64x_08_03_00_18/tools/boot/out2rprc/elf2rprc.js led_flash_r5fss_nortos.out

图 12

执行完成后,将会在当前目录下生成了led_flash_a53ss_nortos.rprc、led_flash_m4fss_nortos.rprc、led_flash_r5fss_nortos.rprc文件。

图 13

- appimage文件生成

基于xxx.rprc文件生成镜像xxx.appimage,需指定启动核心的ID,对应关系如下表所示。

备注:AM6412包含1个Cortex-R5F核心:r5fss0_0;AM6442包含4个Cortex-R5F核心分别为:r5fss0_0、r5fss0_1、r5fss1_0、r5fss1_1。

表 1

|

核心 |

ID |

|

|

Cortex-A53 |

a53ss0_0 |

0 |

|

Cortex-R5F |

r5fss0_0 |

4 |

|

r5fss0_1 |

5 |

|

|

r5fss1_0 |

6 |

|

|

r5fss1_1 |

7 |

|

|

Cortex-M4F |

m4fss0_0 |

14 |

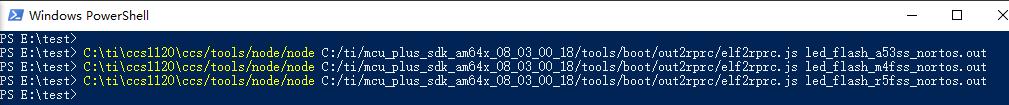

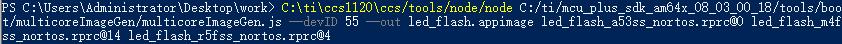

在Windows PowerShell终端执行如下命令,将Cortex-A53、Cortex-M4F和Cortex-R5F核心的led_flash可执行程序合并为led_flash.appimage,并指定运行核心分别为a53ss0_0、m4fss0_0、r5fss0_0。

Window# C:\ti\ccs1120\ccs/tools/node/node C:/ti/mcu_plus_sdk_am64x_08_03_00_18/tools/boot/multicoreImageGen/multicoreImageGen.js --devID 55 --out led_flash.appimage led_flash_a53ss_nortos.rprc@0 led_flash_m4fss_nortos.rprc@14 led_flash_r5fss_nortos.rprc@4

图 14

执行完成后,将会在当前目录下生成led_flash.appimage镜像文件。

图 15

请将生成的led_flash.appimage镜像文件拷贝至Micro SD卡,并重命名为app。

图 16

请将Micro SD卡插入评估板Micro SD卡槽,根据评估底板丝印将启动方式选择拨码开关拨为101000(1~6),此档位为Micro SD启动模式。然后使用Micro USB线连接评估板的USB TO UART0调试串口至PC机。

评估板上电启动,串口调试终端将会打印如下类似启动信息。同时,可观察到评估底板LED1、LED2、LED3闪烁,说明程序自启动成功。

图 17

基于Linux引导裸机、FreeRTOS程序启动

基于Linux启动

本小节以产品资料“4-软件资料\Demo\RTOS-demos\”目录下的ipc_rpmsg_echo_linux案例为例进行演示。该案例主要实现Cortex-A53与Cortex-R5F核间通信,以及Cortex-A53与Cortex-M4F核间通信。

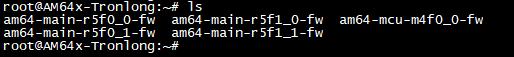

请将案例bin目录下的am64-main-r5f0_0-fw、am64-main-r5f0_1-fw、am64-main-r5f1_0-fw、am64-main-r5f1_1-fw、am64-mcu-m4f0_0-fw镜像文件拷贝至评估板文件系统根目录下。

图 18

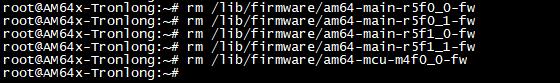

进入评估板文件系统,执行如下命令,删除原来的软链接。

Target# rm /lib/firmware/am64-main-r5f0_0-fw

Target# rm /lib/firmware/am64-main-r5f0_1-fw

Target# rm /lib/firmware/am64-main-r5f1_0-fw

Target# rm /lib/firmware/am64-main-r5f1_1-fw

Target# rm /lib/firmware/am64-mcu-m4f0_0-fw

图 19

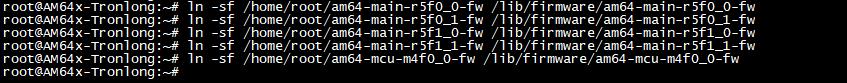

执行如下命令,创建新的软链接。

Target# ln -sf /home/root/am64-main-r5f0_0-fw /lib/firmware/am64-main-r5f0_0-fw

Target# ln -sf /home/root/am64-main-r5f0_1-fw /lib/firmware/am64-main-r5f0_1-fw

Target# ln -sf /home/root/am64-main-r5f1_0-fw /lib/firmware/am64-main-r5f1_0-fw

Target# ln -sf /home/root/am64-main-r5f1_1-fw /lib/firmware/am64-main-r5f1_1-fw

Target# ln -sf /home/root/am64-mcu-m4f0_0-fw /lib/firmware/am64-mcu-m4f0_0-fw

图 20

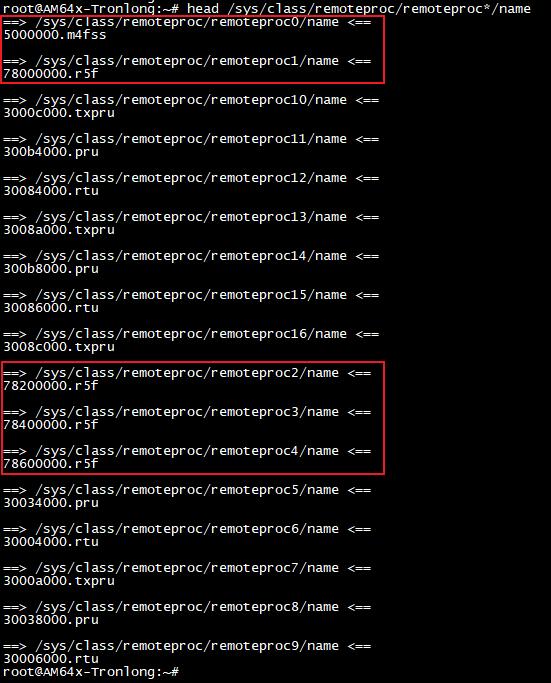

请将评估板重启,在系统启动过程中,Cortex-R5F、Cortex-M4F核心将会引导启动。在评估板文件系统执行如下命令,查询Cortex-R5F、Cortex-M4F核心与remoteproc关系。

Target# head /sys/class/remoteproc/remoteproc*/name

图 21

表 2

|

CPU核心 |

remoteproc |

|

m4fss0_0 |

remoteproc0 |

|

r5fss0_0 |

remoteproc1 |

|

r5fss0_1 |

remoteproc2 |

|

r5fss1_0 |

remoteproc3 |

|

r5fss1_0 |

remoteproc4 |

备注:核心与remoteproc对应关系,请以实际情况为准。

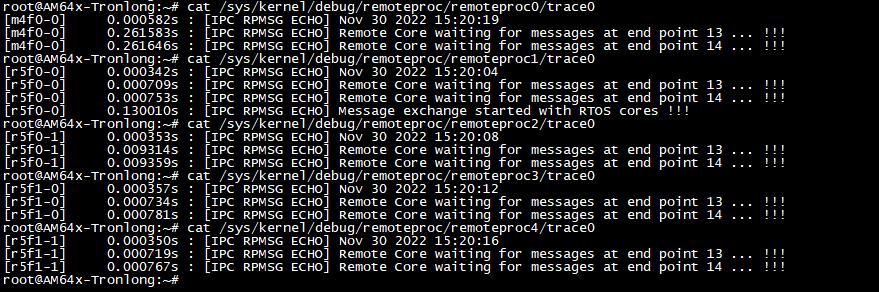

执行如下命令,可查看Cortex-M4F、Cortex-R5F核心程序运行日志。

Target# cat /sys/kernel/debug/remoteproc/remoteproc0/trace0

Target# cat /sys/kernel/debug/remoteproc/remoteproc1/trace0

Target# cat /sys/kernel/debug/remoteproc/remoteproc2/trace0

Target# cat /sys/kernel/debug/remoteproc/remoteproc3/trace0

Target# cat /sys/kernel/debug/remoteproc/remoteproc4/trace0

图 22

工程配置说明

本小节主要演示如何在Cortex-R5F、Cortex-M4F核心的Baremetal(裸机)工程与FreeRTOS工程中添加Linux引导配置。

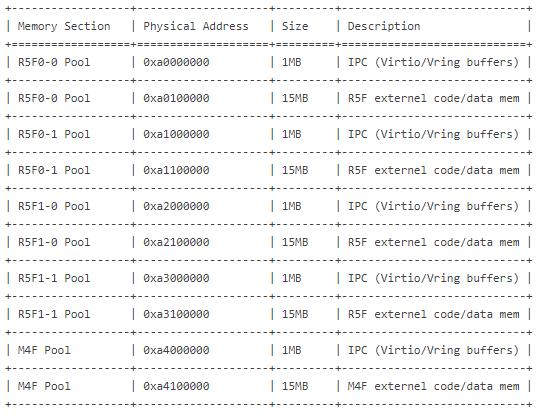

内存空间说明

如Cortex-R5F、Cortex-M4F核心的工程需支持基于Linux启动,则需进行内存空间分配,在Linux设备树中已指定内存空间,预留给Cortex-R5F、Cortex-M4F核心使用。内存空间分配如下图所示。

图 23

Cortex-M4F工程配置

本小节以Cortex-M4F核心的led_flash裸机工程为例进行演示。

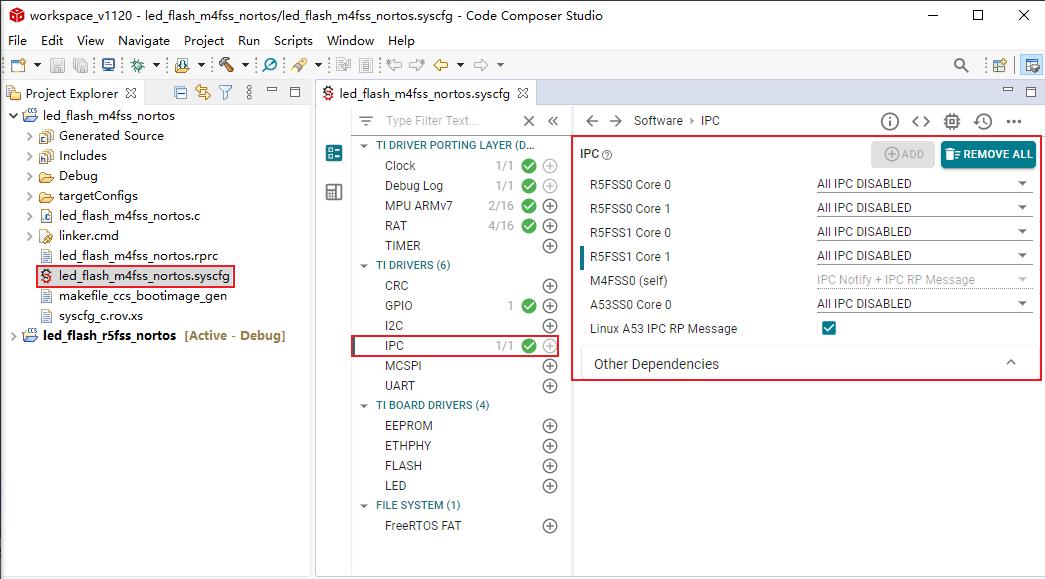

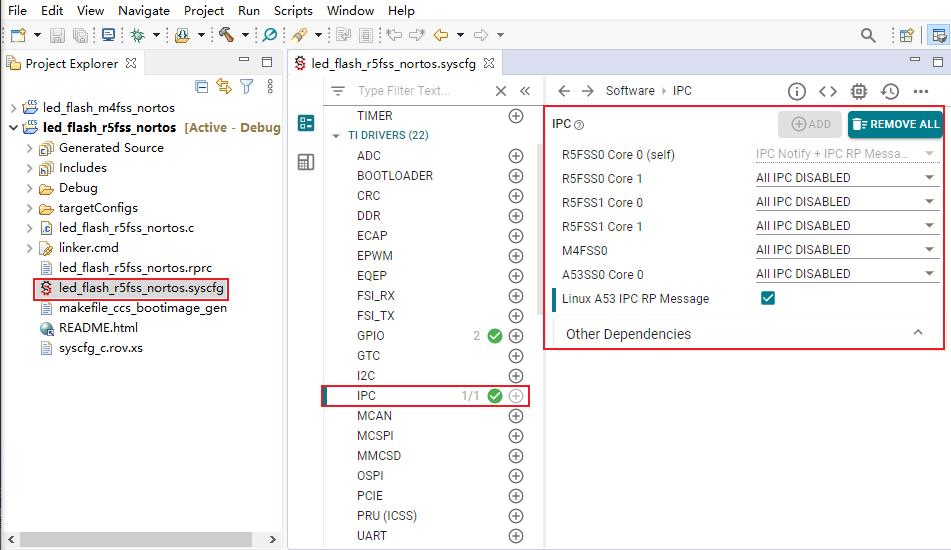

- IPC配置

在syscfg配置文件,添加IPC配置,具体配置如下图所示。

图 24

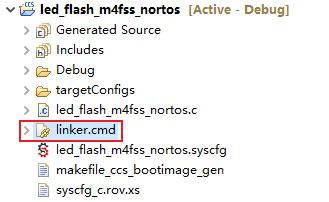

- 编译器链接脚本修改

双击打开编译器链接脚本linker.cmd,修改脚本内容。

图 25

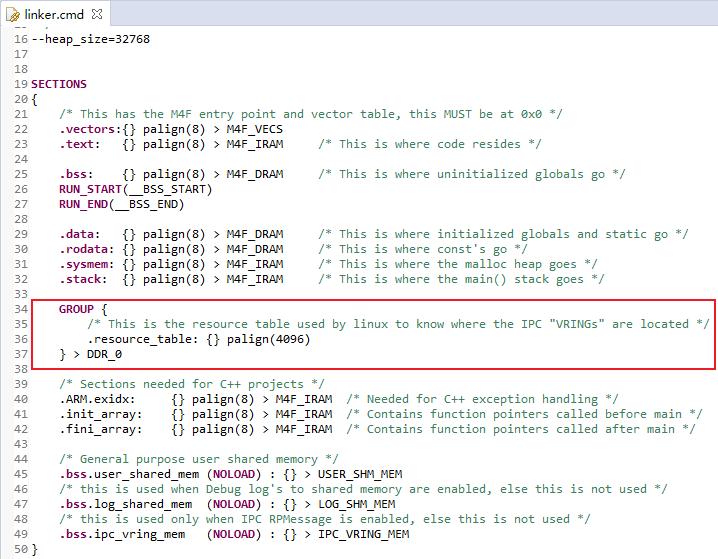

- 在SECTIONS命令中新增一个.resource_table段,具体代码如下所示。

GROUP {

/* This is the resource table used by linux to know where the IPC "VRINGs" are located */

.resource_table: {} palign(4096)

} > DDR_0

图 26

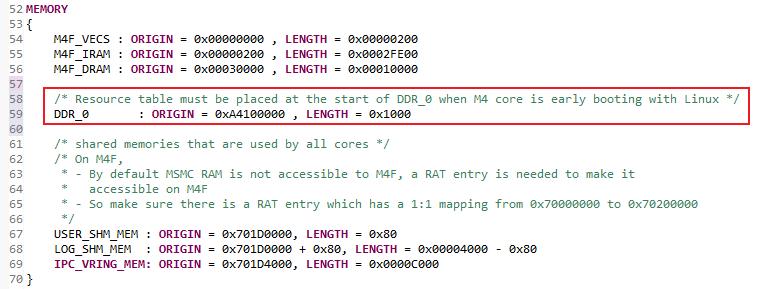

- 在MEMORY命令中,设置.resource_table段的加载地址为0xA4100000,作为Cortex-M4F预留内存空间,具体代码如下所示。

/* Resource table must be placed at the start of DDR_0 when M4 core is early booting with Linux */

DDR_0 : ORIGIN = 0xA4100000 , LENGTH = 0x1000

图 27

Cortex-R5F工程配置

本小节以Cortex-R5F核心的led_flash裸机工程为例进行演示。

AM6412包含1个Cortex-R5F核心:r5fss0_0;AM6442包含4个Cortex-R5F核心分别为:r5fss0_0、r5fss0_1、r5fss1_0、r5fss1_1。不同的Cortex-R5F核心,编译器链接脚本指定的.resource_table段加载地址有所不同,具体如下表所示。

表 3

|

CPU核心 |

加载地址 |

|

r5fss0_0 |

0xA0100000 |

|

r5fss0_1 |

0xA1100000 |

|

r5fss1_0 |

0xA2100000 |

|

r5fss1_1 |

0xA3100000 |

led_flash_r5fss_nortos工程配置的Cortex-R5F核心为r5fss0_0,下面演示如何修改led_flash_r5fss_nortos工程配置,实现基于Linux引导启动r5fss0_0。

- IPC配置

在syscfg配置文件,添加IPC配置,具体配置如下图所示。

图 28

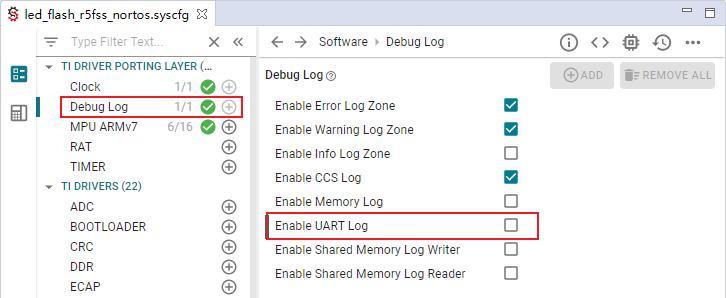

- UART配置

UART0为Cortex-A53核心(Linux系统)的调试串口。在led_flash_r5fss_nortos工程中已配置UART0作为调试串口,请在syscfg配置文件取消勾选"Enable UART Log"配置选项,或修改为Linux设备树中未使能的串口。

图 29

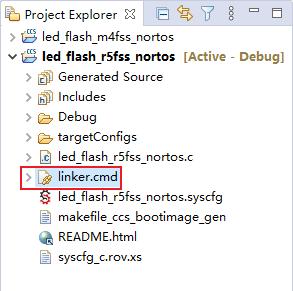

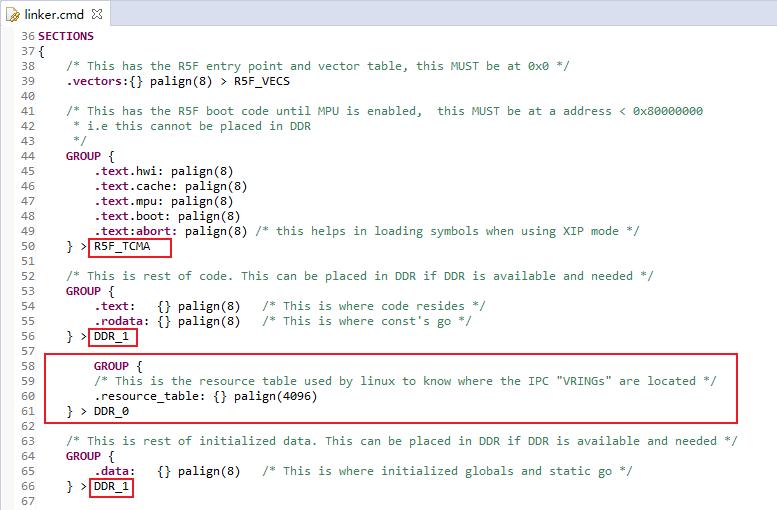

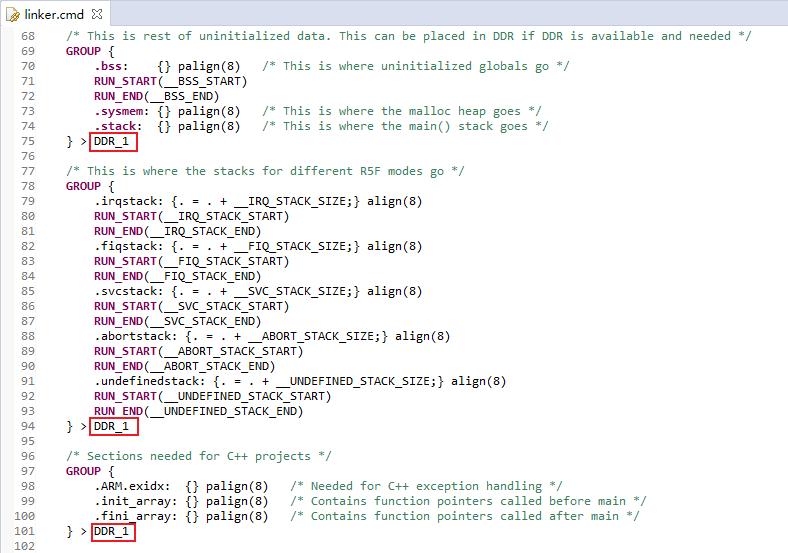

- 编译器链接脚本修改

双击打开编译器链接脚本linker.cmd,修改脚本内容。

图 30

修改内容如下:

- 启动代码链接至R5F_TCMA;

- 新增一个.resource_table段;

- 代码段、数据段、bss段、堆栈全部链接至DDR,在Linux上为r5fss0_0预留内存地址空间;

SECTIONS

{

GROUP {

.text.hwi: palign(8)

.text.cache: palign(8)

.text.mpu: palign(8)

.text.boot: palign(8)

.text:abort: palign(8) /* this helps in loading symbols when using XIP mode */

} > R5F_TCMA

GROUP {

.text: {} palign(8) /* This is where code resides */

.rodata: {} palign(8) /* This is where const's go */

} > DDR_1

GROUP {

/* This is the resource table used by linux to know where the IPC "VRINGs" are located */

.resource_table: {} palign(4096)

} > DDR_0

GROUP {

.data: {} palign(8) /* This is where initialized globals and static go */

} > DDR_1

GROUP {

.bss: {} palign(8) /* This is where uninitialized globals go */

RUN_START(__BSS_START)

RUN_END(__BSS_END)

.sysmem: {} palign(8) /* This is where the malloc heap goes */

.stack: {} palign(8) /* This is where the main() stack goes */

} > DDR_1

GROUP {

.irqstack: {. = . + __IRQ_STACK_SIZE;} align(8)

RUN_START(__IRQ_STACK_START)

RUN_END(__IRQ_STACK_END)

.fiqstack: {. = . + __FIQ_STACK_SIZE;} align(8)

RUN_START(__FIQ_STACK_START)

RUN_END(__FIQ_STACK_END)

.svcstack: {. = . + __SVC_STACK_SIZE;} align(8)

RUN_START(__SVC_STACK_START)

RUN_END(__SVC_STACK_END)

.abortstack: {. = . + __ABORT_STACK_SIZE;} align(8)

RUN_START(__ABORT_STACK_START)

RUN_END(__ABORT_STACK_END)

.undefinedstack: {. = . + __UNDEFINED_STACK_SIZE;} align(8)

RUN_START(__UNDEFINED_STACK_START)

RUN_END(__UNDEFINED_STACK_END)

} > DDR_1

/* Sections needed for C++ projects */

GROUP {

.ARM.exidx: {} palign(8) /* Needed for C++ exception handling */

.init_array: {} palign(8) /* Contains function pointers called before main */

.fini_array: {} palign(8) /* Contains function pointers called after main */

} > DDR_1

/* Sections needed for C++ projects */

GROUP {

.ARM.exidx: {} palign(8) /* Needed for C++ exception handling */

.init_array: {} palign(8) /* Contains function pointers called before main */

.fini_array: {} palign(8) /* Contains function pointers called after main */

} > DDR_1

}

图 31

图 32

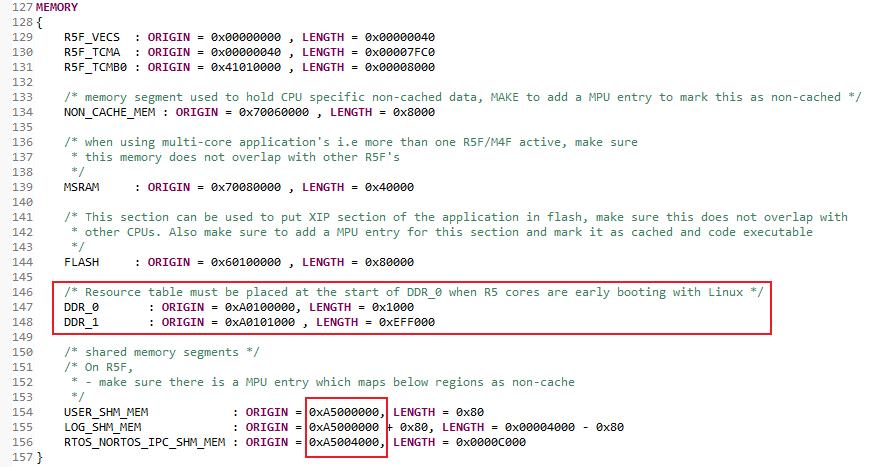

- 设置.resource_table段的加载地址为0xA0100000,作为r5fss0_0核心预留内存空间;

- 设置共享内存链接至Linux为共享内存预留的内存地址空间。

/* Resource table must be placed at the start of DDR_0 when R5 cores are early booting with Linux */

DDR_0 : ORIGIN = 0xA0100000, LENGTH = 0x1000

DDR_1 : ORIGIN = 0xA0101000 , LENGTH = 0xEFF000

USER_SHM_MEM : ORIGIN = 0xA5000000, LENGTH = 0x80

LOG_SHM_MEM : ORIGIN = 0xA5000000 + 0x80, LENGTH = 0x00004000 - 0x80

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0xA5004000, LENGTH = 0x0000C000

图 33

图 33基于 TI Sitara系列 AM64x核心板——程序自启动说明的更多相关文章

- 全新TI AM62xx系列核心板上市,小小身板蕴藏巨大势能!

2011年TI推出AM335x,成为了此后市场上最受欢迎的通用工业级ARM处理器,并广泛应用于工业HMI, 医疗电子,机器人,能源,汽车等领域.随着工业4.0的发展,HMI人机交互.工业工控.医疗等领 ...

- 基于TI Davinci架构的多核/双核开发高速扫盲(以OMAP L138为例),dm8168多核开发參考以及达芬奇系列资料user guide整理

基于TI Davinci架构的双核嵌入式应用处理器OMAPL138开发入门 原文转自http://blog.csdn.net/wangpengqi/article/details/8115614 感谢 ...

- 高性能嵌入式核心板新标杆!米尔推出基于NXP i.MX8M处理器的MYC-JX8MX核心板

随着嵌入式及物联网技术的飞速发展,高性能计算的嵌入式板卡已经成为智能产品的基础硬件平台.为响应行业应用和满足客户需求,米尔电子推出基于NXP公司i.MX8M系列芯片的开发平台MYD-JX8MX系列开发 ...

- 375-基于TI DSP TMS320C6657、XC7K325T的高速数据处理核心板

基于TI DSP TMS320C6657.XC7K325T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP TMS320C6657和 ...

- 202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC72K325T的高速数据处理核心板

基于TI DSP TMS320C6678.Xilinx K7 FPGA XC72K325T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

- 175-基于TI DSP TMS320C6455、Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板

基于TI DSP TMS320C6455.Xilinx V5 FPGA XC5VSX95T的高速数据处理核心板 一.板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP ...

- TI AM335x ARM Cortex-A8工业级核心板,工业网关、工业HMI等用户首选

创龙科技近期推出了ti AM335x ARM Cortex-A8工业级核心板,它拥有高性能.低功耗.低成本.接口丰富等优势,成为了工业网关.工业HMI等用户的首要选择.另外,核心板采用邮票孔连接方式, ...

- 基于xilinx Zynq UltraScale MPSoC平台的核心板及开发板介绍-米尔科技

近日,米尔科技推出国内首款基于xilinx Zynq UltraScale+MPSoC 平台的核心板及开发板.其优势主要有:采用16纳米制程,相比Znyq7000系列每瓦性能提升5倍,且单芯片融合4核 ...

- 基于TMS320C6670的软件无线电核心板

一.板卡概述 北京太速科技自主研发的TMS320C6670核心板,采用TI KeyStone系列的四核定点/浮点DSP TMS320C6670作主处理器.板卡引出处理器的全部信号引脚,便于客户二次开发 ...

- 【iCore、iCore2 双核心板】EPCS 实验(SPI Flash)(基于Verilog语言)

_____________________________________ 深入交流QQ群: A: 204255896(1000人超级群,可加入) B: 165201798(500人超级群,满员) C ...

随机推荐

- linux开发vue项目,不能热更新?

只需要运行下面的命令即可: echo fs.inotify.max_user_watches=524288 | sudo tee -a /etc/sysctl.conf && sudo ...

- 简易的 Linux 流量实时监控工具 watch+ifstat

非常简单小巧的流量实时监控工具,贵在不需要安装,Linux 操作系统自带,在不出外网的环境中很是实用. watch -d ifstat eth1 如果连 ifstat 都没有的环境中也可以使用 ifc ...

- C#应用的用户配置窗体方案 - 开源研究系列文章

这次继续整理以前的代码.本着软件模块化的原理,这次笔者对软件中的用户配置窗体进行剥离出来,单独的放在一个Dll类库里进行操作,这样在其它应用程序里也能够快速的复用该类库,达到了快速开发软件的效果. 笔 ...

- Vue 组件生命周期:探索钩子

title: Vue 组件生命周期:探索钩子 date: 2024/5/27 18:42:38 updated: 2024/5/27 18:42:38 categories: 前端开发 tags: 生 ...

- 13个优秀的AI工具软件导航网站推荐

人工智能(AI)是现在科技领域的热门话题,它不仅改变了我们的生活方式,也催生了许多创新的工具和应用.AI工具可以帮助我们完成各种任务,如绘画.编程.视频制作.语音合成等,让我们的工作和娱乐更加高效和有 ...

- 领域驱动设计(Domain-Driven Design,简称DDD)【简介 个人学习笔记】

找到了第 1 篇资料:领域驱动设计详解:是什么.为什么.怎么做? - 知乎 找到了第 2 篇资料:领域驱动架构(DDD)建模中的模型到底是什么? - 知乎 找到了第 3 篇资料:一文看懂DDD 领域驱 ...

- 005. gitlab安装

1. gitlab介绍 官方网站: www.gitlab.com gitlab是一款使用ruby编写的代码版本管理系统,他可以通过web界面来管理代码. 2. gitlab安装 官方安装文档: htt ...

- k8s——集群环境问题合集

创建集群 k8s集群创建 集群环境问题合集 重置master节点 kubeadm reset -f # -f 强制重置 可选 重置node节点 # 当你的master节点重置后,node节点需要重新加 ...

- Linux驱动--IOCTL实现

参考:[Linux]实现设备驱动的ioctl函数_哔哩哔哩_bilibili.<Linux设备驱动程序(中文第三版).pdf> 1 用户空间ioctl 用户空间的ioctl函数原型,参数是 ...

- 在 Excel 中使用 Python 自动填充公式

安转Python包的国内镜像源 清华大学 https://pypi.tuna.tsinghua.edu.cn/simple 阿里云 https://mirrors.aliyun.com/pypi/si ...