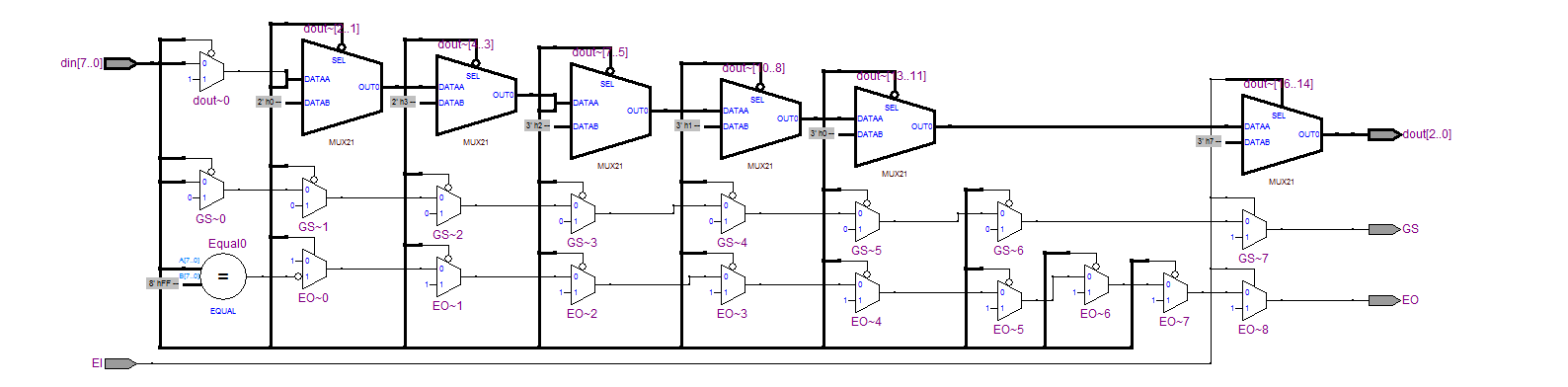

Verilog八线 - 三线优先编码器设计(74LS148)

if语句法

//8线-3线优先编码器设计(74LS148)

//

//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO

//0 | 0 x x x x x x x | 0 0 0 0 1

//0 | 1 0 x x x x x x | 0 0 1 0 1

//0 | 1 1 0 x x x x x | 0 1 0 0 1

//0 | 1 1 1 0 x x x x | 0 1 1 0 1

//0 | 1 1 1 1 0 x x x | 1 0 0 0 1

//0 | 1 1 1 1 1 0 x x | 1 0 1 0 1

//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 1

//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 1

//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 0

//1 | x x x x x x x x | 1 1 1 1 1 module encoder_83 (din, EI, GS, EO, dout);

input [:] din; //编码输入端data_in,低电平有效

input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码

output [:] dout; //编码输出端data_out

output GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效

output EO; //使能输出端EO(选通输出端)

reg [:] dout;

reg GS, EO;

always @(din or EI)

if(EI) begin dout <= 'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平

else if (din[] == ) begin dout <= 'b000; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b001; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b010; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b011; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b100; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b101; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b110; GS <= 0; EO <= 1; end

else if (din[] == ) begin dout <= 'b111; GS <= 0; EO <= 1; end

else if (din == 'b11111111) begin dout <= 3'b111; GS <= ; EO <= ; end //芯片工作,但无编码输入

else begin dout <= 'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)

endmodule //EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作)

//EO = 0 表示电路工作,但无编码输入(用于级联)

//GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)

testbench:

`timescale ps/ ps

module encoder_83_vlg_tst();

reg EI;

reg [:] din;

wire EO;

wire GS;

wire [:] dout;

encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout));

initial

begin

EI = ;

din = 'b11111111;

# EI = ;

# din = 'b01010101;

# din = 'b10101010;

# din = 'b11010101;

# din = 'b11101010;

# din = 'b11110101;

# din = 'b11111010;

# din = 'b11111101;

# din = 'b11111110;

# din = 'b11111111;

end

endmodule

case语句法

//8线-3线优先编码器设计(74LS148)

//

//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO

//0 | 0 x x x x x x x | 0 0 0 0 1

//0 | 1 0 x x x x x x | 0 0 1 0 1

//0 | 1 1 0 x x x x x | 0 1 0 0 1

//0 | 1 1 1 0 x x x x | 0 1 1 0 1

//0 | 1 1 1 1 0 x x x | 1 0 0 0 1

//0 | 1 1 1 1 1 0 x x | 1 0 1 0 1

//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 1

//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 1

//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 0

//1 | x x x x x x x x | 1 1 1 1 1 module encoder_83_case (din, EI, GS, EO, dout);

input [:] din; //编码输入端data_in,低电平有效

input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码

output [:] dout; //编码输出端data_out

output GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效

output EO; //使能输出端EO(选通输出端)

reg [:] dout;

reg GS, EO;

always @(din or EI)

if(EI)

begin dout <= 'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平

else

casez (din) //建议用casez语句,casez把z/?匹配成任意。 casex把z/?/x匹配成任意,x为仿真初态

'b0??????? : begin dout <= 3'b000; GS <= ; EO <= ; end //无关项建议用?表示,?是高阻态的另一种表示。?,z,Z是等价的

'b10?????? : begin dout <= 3'b001; GS <= ; EO <= ; end

'b110????? : begin dout <= 3'b010; GS <= ; EO <= ; end

'b1110???? : begin dout <= 3'b011; GS <= ; EO <= ; end

'b11110??? : begin dout <= 3'b100; GS <= ; EO <= ; end

'b111110?? : begin dout <= 3'b101; GS <= ; EO <= ; end

'b1111110? : begin dout <= 3'b110; GS <= ; EO <= ; end

'b11111110 : begin dout <= 3'b111; GS <= ; EO <= ; end

'b11111111 : begin dout <= 3'b111; GS <= ; EO <= ; end //芯片工作,但无编码输入

default : begin dout <= 'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)

endcase

endmodule //EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作)

//EO = 0 表示电路工作,但无编码输入(用于级联)

//GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!

本人博客:http://www.cnblogs.com/yllinux/

Verilog八线 - 三线优先编码器设计(74LS148)的更多相关文章

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 从YouTube改版看“移动优先”——8个移动优先网站设计案例赏析

2011年,Luke Wroblewski大神提出了移动优先的设计理念.在当时看来这无疑是一个打破行业常规的新型设计原则.而在移动互联网大行其道的今天,谁遵守移动优先的设计理念,设计出最好的移动端网站 ...

- 『TensorFlow』降噪自编码器设计

背景简介 TensorFlow实现讲解 设计新思路: 1.使用类来记录整个网络: 使用_init_()属性来记录 网络超参数 & 网络框架 & 训练过程 使用一个隐式方法初始化网络参数 ...

- 『TensorFlow』单&双隐藏层自编码器设计

计算图设计 很简单的实践, 多了个隐藏层 没有上节的高斯噪声 网络写法由上节的面向对象改为了函数式编程, 其他没有特别需要注意的,实现如下: import numpy as np import mat ...

- 吴裕雄 PYTHON 神经网络——TENSORFLOW 双隐藏层自编码器设计处理MNIST手写数字数据集并使用TENSORBORD描绘神经网络数据2

import os import tensorflow as tf from tensorflow.examples.tutorials.mnist import input_data os.envi ...

- 吴裕雄 PYTHON 神经网络——TENSORFLOW 单隐藏层自编码器设计处理MNIST手写数字数据集并使用TensorBord描绘神经网络数据

import os import numpy as np import tensorflow as tf import matplotlib.pyplot as plt from tensorflow ...

- 8-3编码器,3-8译码器的verilog实现

在数字系统中,由于采用二进制运算处理数据,因此通常将信息变成若干位二进制代码.在逻辑电路中,信号都是以高,低电平的形式输出.编码器:实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码 ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- Verilog HDL 使用规范(一)

本博文参考:<大规模逻辑设计指导书>,对于写出规范的代码,培养良好的代码风格颇有裨益. wire and register 一个reg变量只能在一个always语句中赋值: 这个说明至关重 ...

随机推荐

- C语言变量:名称、地址和值

变量的名称.地址和变量的值之间关系密切. 我们可以认为变量有两个属性:名称和值(其他属性暂不讨论): 计算机编译和加载后也认为变量有两个属性:地址和值.地址就是变量在计算机内部的名称. 许多语言中地址 ...

- Kibana6.x.x——启动后警告信息:Session cookies will be transmitted over insecure connections. This is not recommended.

启动Kibana后,如果你看到如下警告信息: server log [08:03:18.001] [warning][security] Session cookies will be transmi ...

- 使用sqlmetal工具自动生成SQL数据库的Linq类文件

第一部:找到sqlmetal.exe. 运行cmd. 执行命令 cd C:\Program Files (x86)\Microsoft SDKs\Windows\v8.1A\bin\NETFX 4.5 ...

- 牛客Professional Manager(并查集)

t’s universally acknowledged that there’re innumerable trees in the campus of HUST. Thus a professi ...

- TortoiseGit安装简单介绍和使用

首先,你必须有会装软件的技能和一个看得懂英语的眼睛.然后保证Git也装好了 他提供了中文版的安装包哦 安装过程尽量选择默认就行,先装上面那个啊,语言包最后装. 语言配置 因为以前装过,所以...路径是 ...

- hdu2063 最大二分匹配(匈牙利算法)

过山车 Time Limit: 1000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)Total Submiss ...

- hdu1865 1sting (递归+大数加法)

1sting Time Limit: 5000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)Total Subm ...

- vue(6)生态

来自:https://www.jianshu.com/p/22a99426b524?utm_campaign=maleskine&utm_content=note&utm_medium ...

- Vue循环中多个input绑定指定v-model

Vue.js中提供了v-model可以双向绑定表单元素,这个方法可以非常方便的获得输入的值,但是有时候表单元素需要循环生成,在循环中要怎样获得指定输入框的值呢 这里介绍两种,一种是v-for中循环生成 ...

- python连接mysql数据库遇到的问题

1.源代码: from sqlalchemy import create_engine from sqlalchemy.orm import sessionmaker from sqlalchemy ...