GPIO-FPGA架构

GPIO是一种软件运行期间能够动态配置和控制的通用引脚

有不同的GPIObank,每个GPIO口的bank都会有编号的区分,

每个GPIO口除了通用的输入输出功能以外,还有其他复用功能,例如GPIO5_b4可以复用成:

- spi0_clk

- ts0_data4

- uart4exp_ctsn

一、GPIO的特性

1.可编程控制GPIO中断

2.可边沿触发或者电平触发

3输入输出可承受5V

4读写过程中通过位地址线进行位屏蔽

5弱上拉和若下拉电阻

6.2、4/8mA驱动,以及带驱动转换速率skew rate()的8没A驱动

7开漏使能,数字输入使能

二、GPIO的工作模式

1.高阻输入

实际上就是一个带有施密特触发输入的三态缓冲器(U1)高的输入阻抗,施密特触发输入的作用就是将缓慢变化,或是畸变的输入脉冲信号整形成理想的矩形脉冲信号。读脉冲信号把当前的电平状态读出到内部总线上,不执行读操作的时候,外部管脚和内部总线隔离。

2.推挽输出

这里的推挽主要指的是T1 和T2组成的反相器部分,T1或者T2导通的时候,都具有低的阻抗,但是T1T2不会同时导通,或者同时关闭,这样形成的就是推挽输出。在实际的开发板上,T1T2实际上是多组可编程选通的晶体管,驱动能力可以自行配置为各种电流输出的。GPIO还有回读的功能,实现回读功能的实际上是一个简单的三态门U2,回读到的是管教的输出缓存状态,不是外部管脚的状态。

U17.com是输出缓存器,在执行GPIO管教的写操作的时候,在写脉冲的作用下,数据被锁存到Q和Q1。

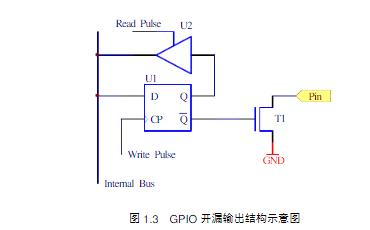

3.开漏输出

开漏输出的结果与推挽输出类似,GPIO管脚在开漏输出下的等效结构模式图,,实际上就是一个开关,输出1时断开,输出0时接到地上,(有一定的内阻)。回读的时候读到的仍然是输出锁存器的状态,而不是外部管脚的pin状态。开漏输出不能用于输入。

实际用用的时候要加上上拉电阻,开漏输出可以方便的实现线与逻辑,另外他可以实现不同逻辑电平之间的转换,只需要接一个上拉电阻,不需要额外的转换电路。典型的应用例子就是基于OD的IIC总线。

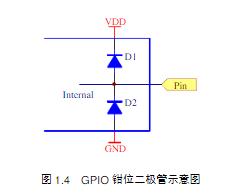

4.钳位二极管

作用在于防止外部管脚Pin的输入电压过高或者过低,VDD的正常供电电压是3.3V,如果从pin输入信号电压超过VDD加上二极管D1的导通压降假定0.6V(),着二极管D1导通,会把多余的电流引入到VDD,而真正输入到内部的信号不会超过3.9V,同理,D2可以限制输入电压的最小值,使之不超过-0.6V 。

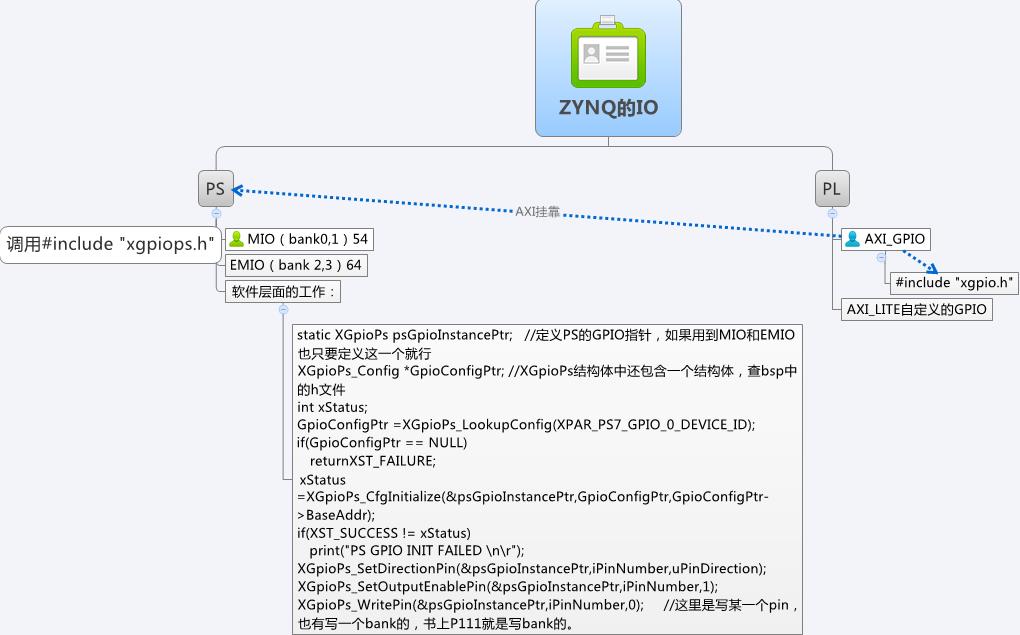

另外,加上一个ZYNQ的IO的用法:

附加一个树莓配的GPIO配置方法:https://blog.csdn.net/xukai871105/article/details/12684617

GPIO-FPGA架构的更多相关文章

- A/X家FPGA架构及资源评估

评估对比xilinx以及altera两家FPGA芯片逻辑资源. 首先要说明, 现今FPGA除了常规逻辑资源,还具有很多其他片内资源比如块RAM.DSP单元.高速串行收发器.PLL.ADC等等,用以应对 ...

- 通过HPS控制FPGA的GPIO

1.学习目的 本例程主要是让 SoC FPGA 初学者了解 HPS/ARM 如何跟 FPGA 交互.“My First HPS-FPGA”工程演示了实现方法的细节.这个工程包括 Quartus II ...

- Xilinx FPGA全局介绍

Xilinx FPGA全局介绍 现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产:许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设 ...

- 笔记之Cyclone IV 第一卷第一章FPGA 器件系列概述

因为本人用的黑金四代开发板,中央芯片采用ALTERA的cycloneIV E,所以就此器件阅读altera官网资料,并做相应的笔记,以便于以后查阅 Cyclone IV 器件系列具有以下特性:■ 低成 ...

- OpenWRT GPIO人口控制 WLED

Linux根据系统GPIO系统架构简介 关于这个GPIO我一直认为非常非常长的时间easy.但.当你需要给一个特定的系统,参与这些GPIO什么时候.你会找到.不对,实例,mt7620n. GPIO#7 ...

- 《那些年,我们拿下FPGA》做笔记

spld.cpld和fpga等可不管什么样的逻辑是大自然来实现.任何逻辑可以由多项式来表示(要么逼关闭).比多项式乘法和处理操作仅此而已. 而就.您可以在门线上用.或门添加剂. fpga扩展架构SOP ...

- 图像处理:卷积模块FPGA 硬件加速

本文记录了利用FPGA加速图像处理中的卷积计算的设计与实现.实现环境为Altera公司的Cyclone IV型芯片,NIOS II软核+FPGA架构. 由于这是第一次设计硬件加速模块,设计中的瑕疵以及 ...

- FPGA与Deep Learning

你还没听过FPGA?那你一定是好久没有更新自己在IT领域的知识了. FPGA全称现场可编程门阵列(Field-Programmable Gate Array),最初作为专用集成电路领域中的一种半定制电 ...

- FPGA学习笔记(一)——初识FPGA

###### [该随笔部分内容转载自小梅哥] ######### FPGA(Field-Programmable Gate Array,现场可编程门阵列),正如其名,FPGA内部有大量的可 ...

- 了解FPGA市场现状和未来趋势

转, 来源: http://www.sohu.com/a/204640373_740053 可编程的“万能芯片” FPGA——现场可编程门阵列,是指一切通过软件手段更改.配置器件内部连接结构和逻辑单元 ...

随机推荐

- Windb实践之Script Command

1.输出参数 .echo The first argument is ${$arg1}. .echo The fifth argument is ${$arg5}. .echo The fourth ...

- github 新建库,提交命令

Command line instructions You can also upload existing files from your computer using the instructio ...

- 小程序Java多次请求Session不变

微信小程序每次请求的sessionid是变化的,导致对应后台的session不一致,无法获取之前保存在session中的openid和sessionKey. 为了解决这个问题,需要强制同意每次小程序前 ...

- php 查看接口运行时间

代码如何: <?php $start_time = microtime(true); for ($i=0;$i<100000000;$i++){}; $end_time = microti ...

- leetcode中的sql

1 组合两张表 组合两张表, 题目很简单, 主要考察JOIN语法的使用.唯一需要注意的一点, 是题目中的这句话, "无论 person 是否有地址信息".说明即使Person表, ...

- Java线程(一)——创建线程的两种方法

Thread 和 Runnable Java程序是通过线程执行的,线程在程序中具有独立的执行路径.当多条线程执行时,它们之间的路径可以不同,例如,一条线程可能在执行switch的一个case语句,另一 ...

- JunOS SRX firewal Web authentication(转)

转载自:https://srxasa.wordpress.com/2011/12/11/junos-srx-firewal-web-authentication/ JunOS SRX firewal ...

- linux 查看链接库的版本

我们编译可执行文件的时候,会链接各种依赖库, 但是怎么知道依赖库的版本正确呢? 下面有几种办法: ldd 这是比较差的,因为打印结果更与位置相关 dpkg -l | grep libprotobuf ...

- 在mybatis框架中,延迟加载与连表查询的差异

1.引子 mybatis的延迟加载,主要应用于一个实体类中有复杂数据类型的属性,包括一对一和一对多的关系(在xml中用collection.association标签标识).这个种属性往往还对应着另一 ...

- 祘头君的字符(DFS)

一.题目 有n名选手在玩游戏,他们每个人有一个字符,每个字符都有自己固定的若干个特征.特征的种类数为k.每个人的特征为特征总集的一个子集. 两个字符的相似度定义为:如果两个字符A和B同时拥有某个特征或 ...