你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点。

二十进制编码器及Verilog HDL描述

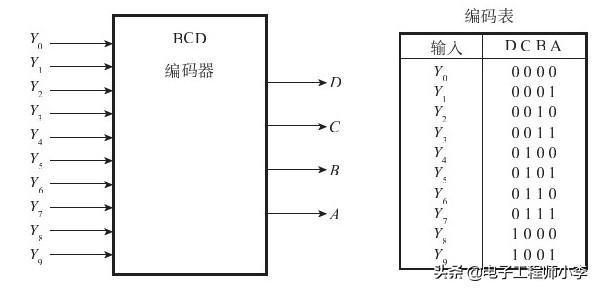

二十进制编码器是数字电路中常用的电路单元,它的输入是代表0~9这10个输入端的状态信息。输入信号为高电平时,输出相应的BCD码,因此也称为10线4线编码器。其功能表及电路符号如图3-1所示。

图3-1 二十进制编码器

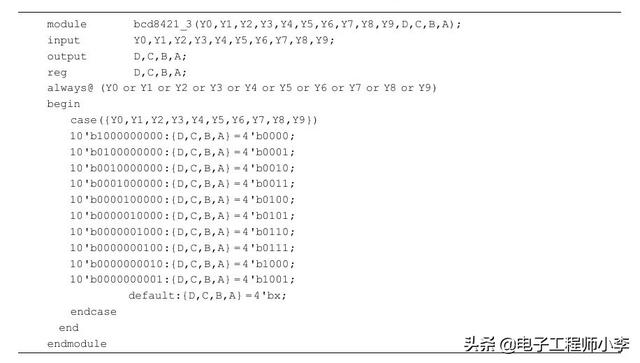

【例3-1】利用Verilog HDL对二十进制编码器进行设计。

Verilog HDL程序的基本构成

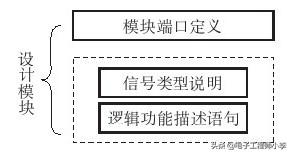

从例3-1可以看出,一个完整的Verilog HDL程序由3个基本部分构成,分别是:模块端口定义部分、信号类型说明部分和逻辑功能描述语句部分。其结构图如3-2所示。

图3-2 Verilog HDL程序基本结构

模块端口定义部分

对于硬件描述语言来说,一个程序代表了一个具有某种逻辑功能的电路,模块端口定义部分描述了该电路的接口部分的信息,即输入输出信号的信息。

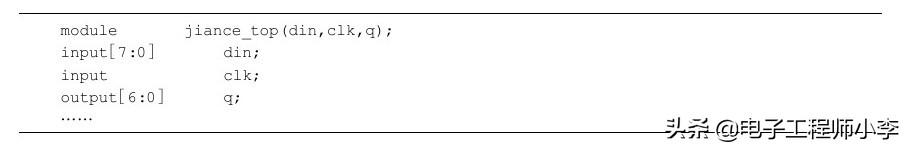

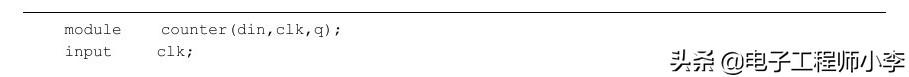

模块端口定义部分的语法结构如下:

module模块名(端口信号1,端口信号2,端口信号3,端口信号4,……);

input[width:0]端口信号1,端口信号3,……;

output[width:0]端口信号2,端口信号4,……;

程序以关键词module引导,模块名是设计者对于设计的电路所取的名字,在模块端口定义的第1行列出了所有进出该电路模块的端口信号,在第2行和第3行中定义了各端口信号流动方向。流动方向包括输入(input)、输出(output)和双向(inout),[width:0]表示信号的位宽,如果位宽没有特别说明,则系统默认为1位宽度。

【例3-2】模块端口定义举例。

信号类型说明部分

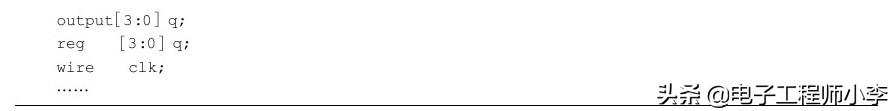

在Verilog HDL语法中,信号共有两种数据类型,分别为:网线类型(net型)和寄存器类型(register型)。在信号类型说明部分除了要对输入/输出端口的信号类型进行说明之外,还要对程序中定义的中间量的数据类型进行说明。

信号类型说明部分的语法结构如下:

wire[width:0]信号1,信号2,……;

reg[width:0]信号3,信号4,……;

【例3-3】信号类型说明举例。

逻辑功能描述语句部分

逻辑功能描述语句部分对输入/输出信号之间的逻辑关系进行了描述,是Verilog HDL程序设计中最主要的部分,在电路上相当于器件的内部电路结构。在Verilog HDL语言中,常用的逻辑功能描述语句可以分为以下3种:

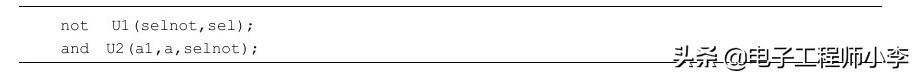

例化语句:调用已进行元件化封装的程序。这种语句常应用于层次化设计的顶层文件设计中。

【例3-4】例化语句举例。

该语句分别调用了一个非门和与门电路模块。

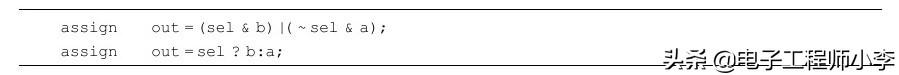

连续赋值语句:描述信号之间简单的赋值关系。在连续赋值语句中,右边表达式使用的操作数无论何时发生变化,右边表达式都重新计算。这类描述通常以关键词assign引导。

【例3-5】连续赋值语句举例。

该语句描述了输出信号与输入信号的赋值关系。

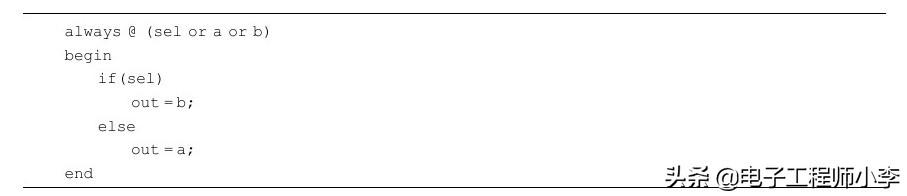

过程语句:以关键词always、initial等关键词引导的语句,描述了一定条件下信号之间的赋值关系。这种变量数据被赋值后,其值保持不变,直到下一次条件具备时对它们重新赋值。

【例3-6】过程语句举例。

与连续赋值语句一样,always和initial也描述了输出信号与输入信号的赋值关系,但是这种赋值往往是一种比较复杂的条件赋值,例如,例3-6就用了if……else语句描述了输出信号与输入信号的条件关系。

本文转自小平头电子技术社区:https://www.xiaopingtou.cn/article-104211.html嵌入式,物联网,硬件PCB,电子技术尽在小平头

你知道Verilog HDL程序是如何构成的吗的更多相关文章

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作. 2--模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的 ...

- Verilog HDL与C语言的比较

Verilog HDL与C语言的比较 Verilog HDL是在C语言的基础上发展起来的,因而它保留了C语言所独有的结构特点. 为便于对Verilog HDL有个大致的认识,在这里将它与C语言的异 ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

随机推荐

- slot插槽

具名插槽只能是template模板标签 插槽组件 <section class="hello"> <slot>Welcome</slot> &l ...

- 【PAT甲级】1070 Mooncake (25 分)(贪心水中水)

题意: 输入两个正整数N和M(存疑M是否为整数,N<=1000,M<=500)表示月饼的种数和市场对于月饼的最大需求,接着输入N个正整数表示某种月饼的库存,再输入N个正数表示某种月饼库存全 ...

- Protobuf协议--java实现

Protobuf协议,全称:Protocol Buffer 它跟JSON,XML一样,是一个规定好的数据传播格式.不过,它的序列化和反序列化的效率太变态了…… 来看看几张图你就知道它有多变态. pr ...

- centos8下gz,bz2,zip压缩解压缩

for gz 1.制作压缩包 [root@192 mnt]# tar czf mydir.tar.gz mydir1/ 2.解压gz 压缩包 [root@192 mnt]# tar xvf mydir ...

- 【PAT甲级】1039 Course List for Student (25 分)(vector嵌套于map,段错误原因未知)

题意: 输入两个正整数N和K(N<=40000,K<=2500),分别为学生和课程的数量.接下来输入K门课的信息,先输入每门课的ID再输入有多少学生选了这门课,接下来输入学生们的ID.最后 ...

- SAM(后缀自动机)总结

“写sam是肯定会去写的,这样才学的了字符串,后缀数组又不会用 >ω<, sam套上数据结构的感觉就像回家一样! 里面又能剖分又能线段树合并,调试又好调,我爱死这种写法了 !qwq” SA ...

- 反射实现定位Servlet中的方法

public class BaseServlet extends HttpServlet{ @Override protected void service(HttpServletRequest re ...

- jmeter 并发控制

1.吞吐控制器以线程组的请求sampler为控制对象, 2.事务控制器: 3.同步定时器syn timer:对某线程组下任意的sampler任意位置作用为,有序控制单个sampler的并发先sampl ...

- redis requires Ruby version >= 2.2.2 系统默认 ruby 版本过低,导致 Redis 接口安装失败

安装 Redis 接口时异常 ,系统 ruby 版本过低 ! 输入命令 " gem install redis " 出现 " ERROR: Error installi ...

- redhat 7.6 流量监控命令、软件(3)nethogs 监控进程实时流量

1.解压nethogs tar -zxvpf nethogs_0.8.5.orig.tar.gz 2.直接make,这里报错,提示pcap.h,安装libpcap就可以了 3.如果已经安装,还是报错, ...