对DDS的深度认识

我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。本公众号作者ALIFPGA,多年FPGA开发经验,所有文章皆为多年学习和工作经验之总结。

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写,是一项关键的数字化技术。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

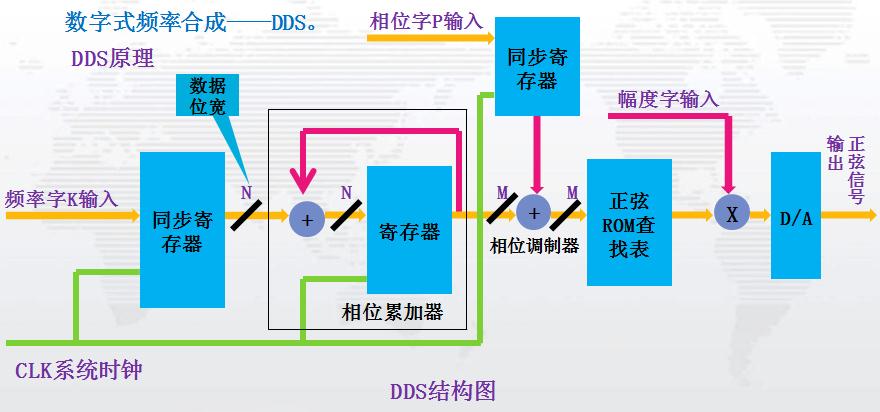

上图所示是一个基本的DDS结构,主要由相位累加器、相位调制器、正弦ROM 查找表和D /A 构成。图中的相位累加器、相位调制器、正弦ROM查找表是DDS结构中的数字部分, 由于具有数控频率合成的功能,又合称为NCO。

相位累加器是整个DDS系统的核心,在这里完成相位累加功能。相位累加器的输入是相位增量B∆θ=2N X fout /fclk,故相位累加器的输入又称为频率控制字,fclk为系统基准时钟,fout为输出的频率。频率控制字还经过一组寄存器, 该寄存器是同步的, 使得当频率控制字改变时不会干扰相位累加器的工作。

相位调制器接收相位累加器的相位输出, 在这里加上一个相位偏移值, 主要用于信号的相位调制,

如应用于通信方面的相移键控等, 不使用此部分时可以去掉, 或者将其设为一个常数输入。同样相位字

输入也要用同步寄存器保持同步。

正弦ROM查找表,完成fsin(B∆θ)的查找表转换,是相位到幅度的转换, 内部存有一个完整周期正弦波的

数字幅度信号,输入是ROM 的地址值, 输出送往D /A, 转化成模拟信号。

在参考时钟fclk控制下,频率控制字K与相位寄存器的输出反馈在相位累加器中完成加运算,存入寄存器,作为下一次加运算的一个输入值,相位累加器输出高位数据作为波形存储器的相位抽样地址值,查找波形存储器中相对应单元的电压幅值,得到波形二进制编码,实现相位到电压幅值的转变。波形二进制编码再通过D/A转换器,把数字信号转换成相应的模拟信号。

fout =K X fclk/ 2N

当K=l时,可得DDS的最小分辨率为:fout =fclk/ 2N

根据采样定理,K的最大值应小于2N/2。

累加器得到的相位是怎么去寻址正弦ROM的,对于N位的相位累加器对应2的N次方数量的相位累加值,如果正弦ROM中存储的点数也是2的N次方的话,对存储容量和资源的要求就比较高了,实际上在寻址正弦ROM表时,用的是相位累加值的高位,也就是说并不是每个时钟fc都从正弦ROM表中取一个数值,而是多个时钟取一个值,这样能保证相位累加器溢出时,从正弦ROM表中取出正好一个正弦周期的样点。因此,相位累加器每计数2的N次方次,对应一个正弦周期。而相位累加器1秒钟计数fc次,在k=1时,DDS输出的时钟频率就是频率分辨率。频率控制字K增加时,相位累加器溢出的频率增加,对应DDS输出的频率变为K倍的DDS频率分辨率。

深入剖析:

设定:ROM存储点数为1024,每个点是用8位二进制表示。即,ROM地址线宽度为10,数据线宽度为8。

根据上述条件可以知道,相位调制器位宽M=10,那么根据DDS原理,相位累加器位宽N=20。那么在相位调制器中与相位控制字进行累加时,应用相位累加器的高10位累加。

而相位累加器的低十位只与频率控制字累加。为什么是这样子?

我们以频率控制字K=1为例,相位累加器的低十位一直会加1,直到低十位溢出向高十位进位,此时ROM地址应该是0,也就是说,ROM的0地址中的数据被读了1024次,继续下去,ROM中的1024个点,每个点都将会被读1024次,最终输出的波形频率应该是参考时钟频率的1/1024。 fout =1 Xfclk/ 1024。反过来想,周期被扩大了1024 。同样当频率控制字为10时,相位累加器的低十位一直会加10,那么,相位累加器的低十位溢出的时间比上面会快十倍,则ROM中的每个点相比于上面会少读10次,所以最终输出频率是上述的10倍。fout =10 Xfclk/ 1024。这就是DDS。

DDS 最终输出的正弦波的幅值,必须都是ROM表中的正弦幅值。之前我们说根据采样定理,频率控制字K的最大值应小于2的N次幂除以2,这是有道理的,累加器数据位宽20位,ROM表地址位宽10位,在最终ROM表寻址时,用的是累加器的高10位,而低10位只用来进行累加。由于我们上述说DDS最终输出正弦波的赋值必须是ROM表中的幅值,也就是说,ROM表中的幅值必须都被用到,而不能跳过。以累加器位宽20位为例,它的一半是1024,当频率控制字以超过1024累加时,高十位输出累加值会超过1,也就是在寻址ROM表时跳过某些赋值。根据上述可以得出结论了,频率控制字K的最大值应小于2的N次幂除以2。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

对DDS的深度认识的更多相关文章

- ROM存储1/4周期正弦信号构造DDS

上周的时候,老师让编写一个简单的dds程序,本文说明了整个过程中我遇到问题以及一些个人的思考.初次接触FPGA,如有问题请多多指教~ 1.几个疑问,解决和没有解决的. 为何采用ROM而不是直接采用DD ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- 数字信号处理专题(1)——DDS函数发生器环路Demo

一.前言 会FPGA硬件描述语言.设计思想和接口协议,掌握些基本的算法是非常重要的,因此开设本专题探讨些基于AD DA数字信号处理系统的一些简单算法,在数字通信 信号分析与检测等领域都会或多或少有应用 ...

- 基于MATLAB搭建的DDS模型

基于MATLAB搭建的DDS模型 说明: 累加器输出ufix_16_6数据,通过cast切除小数部分,在累加的过程中,带小数进行运算最后对结果进行处理,这样提高了计算精度. 关于ROM的使用: 直接设 ...

- FPGA学习笔记. DDS

DDS原理 直接数字式频率合成器(Direct Digital Synthesizer) 频率计算公式 Fout = FW * Fclk / 2^N Fout 输出频率, Fw 频率控制字, N 位数 ...

- 基于FPGA(DDS)的正弦波发生器

记录背景:昨晚快下班时,与同事rk聊起怎么用FPGA实现正弦波的输出.我第一反应是利用高频的PWM波去滤波,但感觉这样的波形精度肯定很差:后来想起之前由看过怎么用FPGA产生正弦波的技术,但怎么都想不 ...

- 【小梅哥FPGA进阶教程】第十一章 四通道幅频相可调DDS信号发生器

十一.四通道幅频相可调DDS信号发生器 本文由山东大学研友袁卓贡献,特此感谢 实验目标 实现多通道可调信号发生器 实验平台 芯航线FPGA核心板.ADDA模块 实验现象 实现基于FPGA的多通道可调信 ...

- 基于FPGA的DDS任意波形发生器设计

一.简介 DDS技术最初是作为频率合成技术提出的,由于其易于控制,相位连续,输出频率稳定度高,分辨率高, 频率转换速度快等优点,现在被广泛应用于任意波形发生器(AWG).基于DDS技术的任 ...

- verilog 实现DDS

一.DDS的原理 直接数字频率合成器(DDS),功能是通过输入频率输入字从而实现改变输出信号的频率的功能,它所利用的原理就是虽然对于一段正弦信号来说其幅度值是非线性的,但是其相位的值却是线性增加的,如 ...

随机推荐

- scala学习手记21 - 传递变长参数

在Java中是可以使用变长参数的,如下面的方法: public void check(String ... args){ for(String tmp : args){ System.out.prin ...

- python 邮件发送实例

#!/usr/bin/env python # -*- coding: utf-8 -*- from email.header import Header from email.mime.text i ...

- 【总结】对异步处理的http接口进行性能测试

以前对接口做性能测试,接口都是同步处理的,请求之后等待响应结果就知道处理结果了,这样只要看这个接口是否异常,如果无异常无报错记录这个接口的响应时间.TPS等性能指标进行分析就可以了,最近在工作中遇到了 ...

- Linux文件的默认权限:umask

1. 文件的默认权限 Linux下当我们新建一个文件和目录时,该文件和目录的默认权限是什么? 通过umask命令来查看: $ umask0002 $ umask -Su=rwx,g=rwx,o=rx ...

- AWR报告分析解读

http://blog.csdn.net/weiwangsisoftstone/article/details/7614430 1.AWR报告头信息 DB Name :数据库名字 DBid: 数据库i ...

- oracle索引-二元高度

本文转载 作为数据库管理员来说,要在表上建立索引很简单.但是要知道这个索引是否合适.如何优化索引则就具有一定的难度.这项工作也是用来评价一个数据库管理员是否算得上专家的一个重要指标.那么为什么索引优化 ...

- 【spark】常用转换操作:keys 、values和mapValues

1.keys 功能: 返回所有键值对的key 示例 val list = List("hadoop","spark","hive",&quo ...

- 服务器(Ubuntu 12.04 LTS)上编译基于OpenCV的项目遇到的问题及解决方案

问题1:OpenCV编译安装时出错,错误信息中提到要打开-fPIC 选项重试. 解决方案:使用如下命令运行CMake cmake -DWITH_1394=OFF -DWITH_CUDA=OFF -DW ...

- java中的策略设计模式

本文主要讲java中的策略模式:一个可以根据不同的传入参数而具有不同行为的方法,就叫策略模式.概念可能有点不好理解,具体看下面代码: import java.util.Arrays; /** * 策略 ...

- 点击bindingNavigatorAddNewItem 关联的dataGridView不会新增一行

方法一. 在设计界面,修改bindingNavigator1的属性AddNewItem 为“(无)”: 方法二. 在设计器自动生成的代码中找到这一行: // bindingNa ...