EMIF接口与FPGA的互联(转)

reference: https://blog.csdn.net/ruby97/article/details/7539151

DSP6455的EMIFA模块

之前介绍了DSP6455的GPIO和中断部分。今天,继续介绍EMIFA模块。

关于C6000系列的GPIO,请参考:C6000系列DSP的GPIO模块

关于C6000系列的中断系统,请参考:C6000系列DSP的中断系统

背景

使用FPGA系统进行视频采集,DSP进行视频处理需要了解以下知识:

- 1. DSP-C6000系列的中断与GPIO系统

- 2. DSP-C6000系列的EMIFA模块

- 3. DSP-C6000系列的EDMA模块

- 4. FPGA的乒乓RAM

- 5. 一种视频格式(例如VGA,PAL等)

- 6. 视频处理算法

之前已经介绍了第一部分,今天介绍第二部分。

主题

EMIF是External Memory Interface的简称。个人认为它是DSP比较强大的地方之一。通过EMIF接口,使得DSP可以和FPGA很方便地进行大数据量的数据传输。

C6455的EMIFA可以访问多种外部存储器,比如:SRAM,ROM,FLASH等等。当然,也包括FPGA。本文的重点就是介绍使用EMIFA接口与FPGA建立无缝连接。

--------------------------------------------华丽分割------------------------------------------------

EMIFA

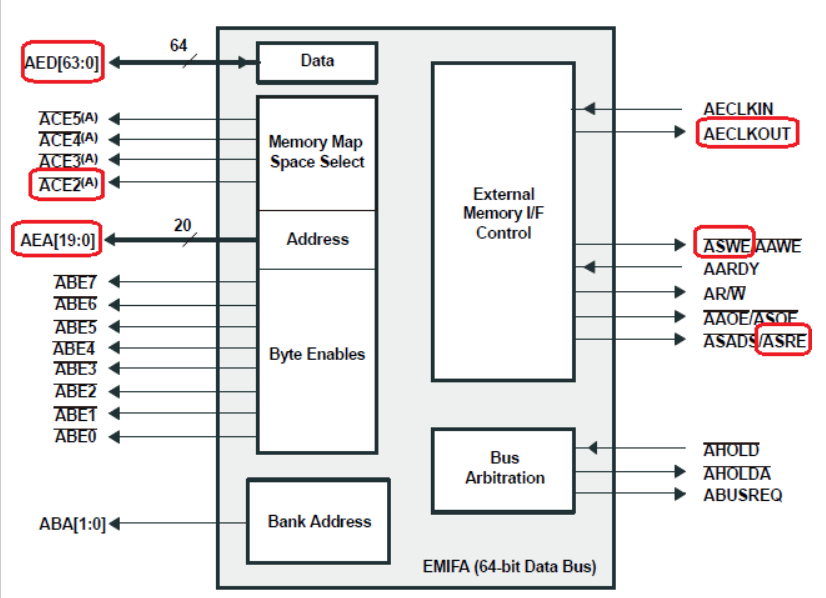

根据习惯,还是先贴图,框图总给人一目了然的感觉。

这是官方文档给出的EMIFA模块的接口示意图,乍一看,复杂的很。好多引脚而且还有好多复用。没关系,我们再贴一张,你就会感觉轻松很多了。

这一张图首先是把EMIFA模块的接口分了类,然和呢,我把在与FPGA通信场合下所需要使用的管脚使用红色框框标注了出来。是不是少了很多呢。归纳一下标注的管脚,如下:

- AED[63:0] 64位数据总线

- AEA[19:0] 20位地址总线(Optional)

- ACE2 片选信号(低有效)

- AECLKOUT 时钟信号

- ASWE 写使能(低有效)

- ASRE 读使能(低有效)

(注:应用场合是DSP读FPGA内部RAM中的图像数据,其他场合续根据情况调整)

由于FPGA的可编程性,使得一切从DSP看来简单了许多。因为DSP面对的“存储器”显得格外智能。甚至连地址线都可以不需要。

下面,我们来一一分析上述的信号。

- 首先,应该是片选信号CE。这里不得不提到DSP的地址空间。下图是DSP6455的EMIFA映射情况

- EMIFA共支持4个外部存储器,比如可以把CE2分配给FPGA,CE3分配给SRAM,CE4分配给FLASH等。

- 每个外部存储器的寻址空间大小是8MB。20根地址线即2的20次方,也就是1MB,此外由于数据总线是64位的,故对应的寻址空间是8MB

由于FPGA内部时序逻辑可以产生地址,所以我们可以不使用地址线。这样,下面的事情就简单了。只要把CE2管脚和FPGA的某一个通用IO口连上即可。

在读取FPGA内部RAM数据时告诉EDMA要读取的数据的基地址是0xA0000000,以及读取的数据的长度即可。

- 第二个信号,ECLKOUT,即时钟信号的。因为FPGA工作是需要时钟激励的,没有时钟信号怎么产生地址逻辑呢?此外,时钟频率不能过高,要考虑到FPGA芯片的能力。OK,因为有了同步时钟,所以EMIFA模块的工作模式也就确定了,即同步工作模式。

- 第三个信号,包括2个,即ASRE,ASWE。更熟悉的叫法是RE,WE。读使能和写使能。这个就不赘述了。

- 第四个信号,数据总线&地址总线。也不赘述了。

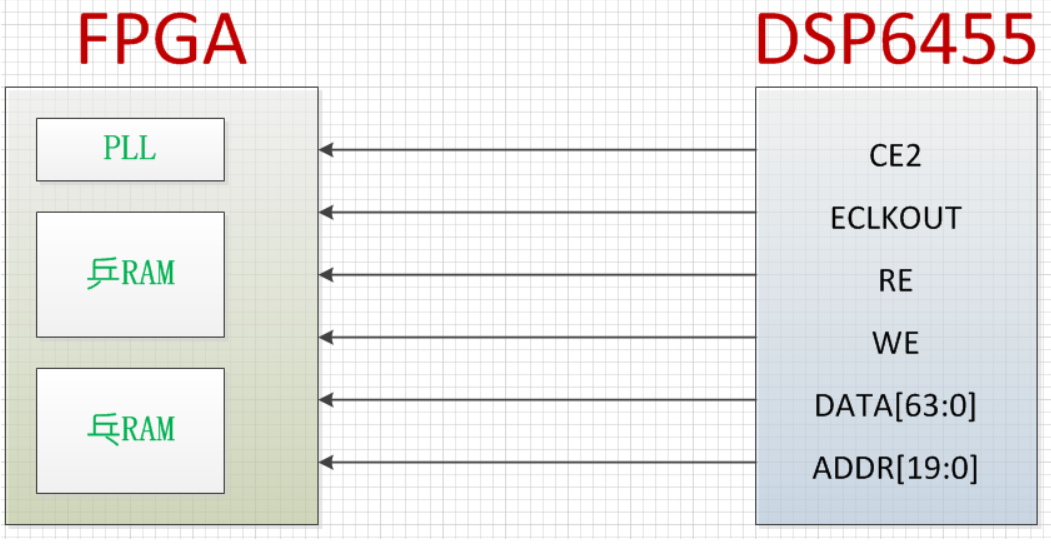

经过上面的分析,我们可以简要的画出FPGA与DSP的连接图:

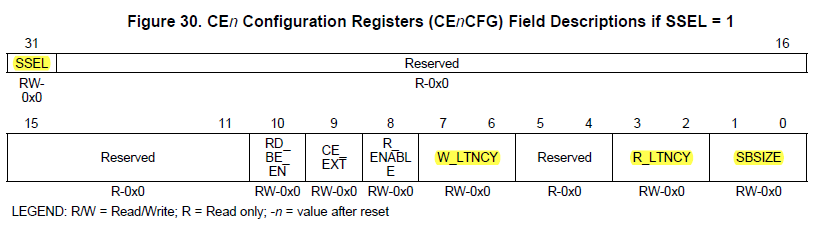

其实也就只有1个比较重要的寄存器,即CEnCFG。该寄存器有两套完全不同的配置。分别对应于同步存储器模式和异步存储器模式。由于FPGA内部RAM工作于同步模式,故我们来看一下同步模式下该寄存器的配置。

| R_ENABLE | 设置SRE/SADS管脚功能 |

| 值为 1 | 管脚功能为SRE,即Read Enable |

| 值为 0 | 管脚功能为SADS |

| W_LTNCY | 写延时周期 |

| 值为 00 | 0周期延时 |

| 值为 01 | 1周期延时 |

| 值为 10 | 2周期延时 |

| 值为 11 | 3周期延时 |

| R_LTNCY | 读延时周期 |

| 值为 01 | 1周期延时 |

| 值为 10 | 2周期延时 |

| 值为 11 | 3周期延时 |

读延时:当CE和RE同时为低电平后,表示DSP开始读FPGA的RAM,经过R_LTNCY个ECLKOUT周期后第一个数据出现在数据总线上

| SBSIZE | 数据位宽 |

| 值为 00 | 8位数据总线 |

| 值为 01 | 16位数据总线 |

| 值为 10 | 32位数据总线 |

| 值为 11 | 64位数据总线 |

EMIFA之CSL

使用CSL配置EMIFA模块时,主要的步骤如下:

- l 1. 使能设备EMIFA模块

- l 2. 配置CEnCFG寄存器

- l 3. 初始化EMIFA模块

- l 4. 打开EMIFA模块

- l 5. 把2中配置的参数设置到打开的EMIFA模块中

完整配置代码:(把EMIFA的CE2配置为以FPGA作为外部存储器,64位数据线,2个周期的读延时)

/*-----------------------------------------------------------------------------------

*

* 初始化EMIFA

*

-----------------------------------------------------------------------------------*/

#define EMIFA_MEMTYPE_ASYNC 0

#define EMIFA_MEMTYPE_SYNC 1

#define EMIFA_CE2_BASE_ADDR (0xA0000000)//地址空间基地址

#define CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER 2//读延时2周期

#define CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER 3//64位数据总线

#define CSL_EMIFA_SYNCCFG_READEN_PARAMETER 1//SRE

//CEnCFG寄存器参数宏

#define CSL_EMIFA_SYNCCFG_PARAMETER {\

(Uint8)CSL_EMIFA_SYNCCFG_READBYTEEN_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_CHIPENEXT_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_READEN_PARAMETER, \

(Uint8)CSL_EMIFA_SYNCCFG_WLTNCY_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER, \

(Uint8)CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER \

}

void Init_EMIF()

{

CSL_EmifaObj emifaObj;

CSL_Status status;

CSL_EmifaHwSetup hwSetup;

CSL_EmifaHandle hEmifa;

CSL_EmifaMemType syncVal;

CSL_EmifaSync syncMem = CSL_EMIFA_SYNCCFG_PARAMETER;

memset(&emifaObj, 0, sizeof(CSL_EmifaObj));

memset(&hwSetup, 0, sizeof(CSL_EmifaHwSetup));

//步骤1: 使能设备的EMIFA功能(不用先解锁外设寄存器)

CSL_FINST(((CSL_DevRegs*)CSL_DEV_REGS)->PERCFG1, DEV_PERCFG1_EMIFACTL, ENABLE);

//步骤2:配置CE2CFG寄存器

syncVal.ssel = EMIFA_MEMTYPE_SYNC;

syncVal.async = NULL;

syncVal.sync = &syncMem;

hwSetup.ceCfg[0] = &syncVal;

hwSetup.ceCfg[1] = NULL;

hwSetup.ceCfg[2] = NULL;

hwSetup.ceCfg[3] = NULL;

//步骤3:初始化EMIFA模块

status = CSL_emifaInit(NULL);

#ifdef SHOW_PRINTF

if (status != CSL_SOK) {

printf("EMIFA: Initialization error.\n");

printf("\tReason: CSL_emifaInit [status = 0x%x].\n", status);

return;

}

else {

printf("EMIFA: Module Initialized.\n");

}

#endif

//步骤4:打开EMIFA模块

hEmifa = CSL_emifaOpen(&emifaObj,CSL_EMIFA,NULL,&status);

#ifdef SHOW_PRINTF

if ((status != CSL_SOK) || (hEmifa == NULL)) {

printf("EMIFA: Error opening the instance. [status = 0x%x, hEmifa \

= 0x%x]\n", status, hEmifa);

return;

}

else {

printf("EMIFA: Module instance opened.\n");

}

#endif

//步骤5:把步骤2中配置的参数设置到打开的EMIFA模块中

status = CSL_emifaHwSetup(hEmifa,&hwSetup);

#ifdef SHOW_PRINTF

if (status != CSL_SOK) {

printf("EMIFA: Error in HW Setup.\n");

printf("Read write operation fails\n");

return;

}

else {

printf("EMIFA: Module Hardware setup is successful.\n");

}

#endif

}

EMIF接口与FPGA的互联(转)的更多相关文章

- AM5728通过GPMC接口与FPGA高速数据通信实现

硬件:AM5728开发板:Artix-7开发板软件:Linux am57xx-evm 4.4.19:Vivado 2015.2作者:杭州矢志信息科技有限公司邮箱:admin@sysjoint.com ...

- DM8168通过GPMC接口与FPGA高速数据通信实现

硬件:TI达芬奇TMS320DM8168(以下简称DSP).EP4CE6E22C8N(以下简称FPGA) 软件:linux-2.6.37 转载请注明出处- http://www.cnblogs.com ...

- VC709E 基于FMC接口的FPGA XC7VX690T PCIeX8 接口卡

一.板卡概述 本板卡基于Xilinx公司的FPGA XC7VX690T-FFG1761 芯片,支持PCIeX8.两组 64bit DDR3容量8GByte,HPC的FMC连接器,板卡支持各种FMC子卡 ...

- EMIF接口的寻址问题

2014年8月26日,一个网友提出了一个关于EMIF访问地址很典型的问题,在此我阐述一下我的个人理解. 一.提出问题 他问的问题没有这么简单,但是差不多就是这种意思,我在晚上找个典型事例,如下: DS ...

- spi master接口的fpga实现

前言 当你器件的引脚贼少的时候,需要主机和从机通信,spi就派上了用场,它可以一对多,但只是片选到的从机能和主机通信,其他的挂机. spi:serial peripheral interface 串行 ...

- spi slaver接口的fpga实现

前言 spi从机接口程序,数据位8bit,sck空闲时低电平,工作时第一个沿数据传输.只有一个从机,cs低电平片选,slaver开始工作. 流程: 接口定义: 编码实现:(版权所有,请勿用于商业用途, ...

- MIPI CSI2-TX接口基于FPGA实现

MIPI CSI2-TX用途: 跟海思的3559A芯片进行图像数据传输: MIPI CSI2-TX接口特性: xilinx 7系列芯片最大支持1.25Gbps: 最大支持lanes数量为4: 支持的图 ...

- SDI接口基于FPGA GTP实现

SDI采集和显示,基于xilinx 7系列器件进行实现,注意事项有如下几点: 1,如果多路SDI共用一个GTP Quad,或是SDI和PCIE在一个GTP Quad,时钟资源应该进行共享,既GTP c ...

- 嵌入式驱动开发之dsp fpga通信接口---spi串行外围接口、emif sram接口

-----------------------------------------author:pkf ------------------------------------------------ ...

随机推荐

- Backup and Recovery Types

Physical(Raw) and Logical Backup: 1.Physical backups consist of raw copies of the directories and fi ...

- 雷林鹏分享:XML 语法规则

XML 语法规则 XML 的语法规则很简单,且很有逻辑.这些规则很容易学习,也很容易使用. 所有的 XML 元素都必须有一个关闭标签 在 HTML 中,某些元素不必有一个关闭标签: This is a ...

- Spring Boot之默认连接池配置策略

注意:如果我们使用spring-boot-starter-jdbc 或 spring-boot-starter-data-jpa “starters”坐标,Spring Boot将自动配置Hikari ...

- 4.2 面向对象分析(二) CRC方法标识概念类

CRC 又称为CRC索引卡片:CRC card 每张卡片代表一个类 Each card represents one class 每张卡片上写出这个类承担的职责.与其合作交互的其他类名 ...

- 完整的Django入门指南学习笔记3

前言 在本节课中,我们将深入理解两个基本概念: URLs 和 Forms.在这个过程中,我们还将学习其它很多概念,如创建可重用模板和安装第三方库.同时我们还将编写大量单元测试. 如果你是从这个系列教程 ...

- Selenium-WebDriver驱动对照表

Chrome 对于chrome浏览器,有时候会有闪退的情况,也许是版本冲突的问题,我们要对照着这个表来对照查看是不是webdriver和chrome版本不对 chromedriver版本 支持的Chr ...

- 更改 Windows 软件默认安装位置教程

在打开的“运行”窗口中,输入命令regedit,然后点击确定按钮 计算机\HKEY_LOCAL_MACHINE\SOFTWARE\Microsoft\Windows\CurrentVersion 百度 ...

- 【Java】【5】List随机取值

//shuffle 打乱顺序 Collections.shuffle(list); //随机抽取1个值 System.out.println(list.get(0)); //随机抽取N个值 Syste ...

- stl中常用的排序算法

#include"iostream" #include"vector" using namespace std; #include"string&qu ...

- Oracle 聚合函数

聚合函数: SQL中提供的聚合函数可以用来统计.求和.求最值等等. 此处采用Oracle 11g中其他用户SCOTT中的EMP表,进行演示. –COUNT:统计行数量 COUNT(*)统计的是结果集的 ...