FPGA在AD采集中的应用

AD转换,也叫模数转换,是将模拟信号转换为数字信号。目前包括电脑CPU,ARM,FPGA,处理的信号都只能是数字信号,所以数据信号在进入处理芯片前必须要进行AD转换。

在高速的AD转换中,FPGA以其高速的处理能力,并行的运行结构,丰富的IO资源,往往承担者不可替代的作用。

下面给出一个实际的设计方案。

AD芯片的时钟为25M,FPGA内部系统时钟频率为100M,FPGA内部处理AD数据的处理模块需要8个时钟周期才能处理完一个数据。

根据上述给出的条件,我们可以知道。按正常思路设计方案,肯定会造成AD数据的丢失,为什么会丢失数据,试想一下,FPGA处理一个数据需要8个时钟周期,才能采集下一个数据,这样算下来AD需要的时钟是12.5M,而给定的AD时钟是25M,所以肯定会漏掉数据。

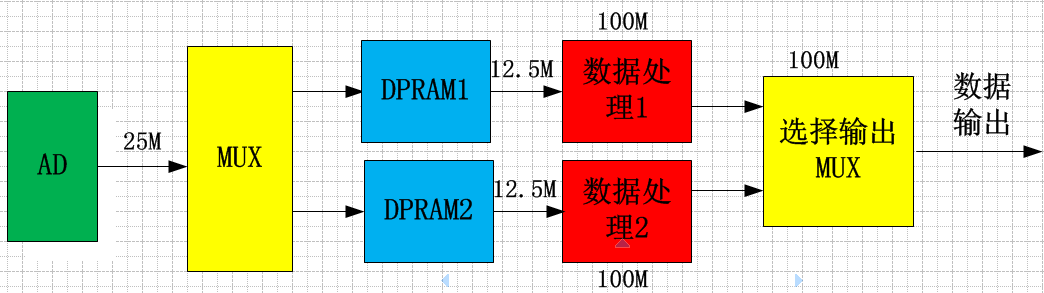

根据分析,可以采用乒乓操作通过缓存降低数据采样率。

乒乓操作如下图:

具体乒乓操作为什么能够降低数据速率,这里将不做详细介绍。

以上方案可以满足上述处理AD数据的需求。

紧接着继续增加需求条件,要求数据处理需要连续,不能打乱顺序,前面数据的处理会影响后续数据处理。这样乒乓操作将不适合,具体原因,读者可以自己想一下(乒乓操作会以数据块打乱数据顺序)。

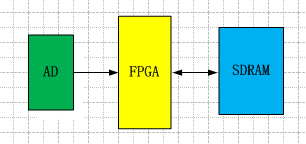

根据上述条件,设计方案需要修改。可以外加存储器,FPGA片上存储器资源有限。

添加SDRAM提高存储速度和存储量。

继续添加需求,如果AD数据连续不断,那么势必是造成SDRAM溢出。那么上述设计方案也不可采取了。

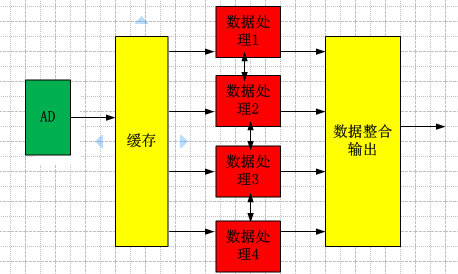

最后根据条件,数据需要连续处理,后面数据的处理要根据前面数据的处理状态决定,而且数据连续不断。

为了满足时序要求,并且不能遗漏数据,重新对方案进行设计。

将数据处理模块分成几个小的处理模块。不仅降低数据处理速率,同时个处理模块之间相互联系,后续数据处理能够知道前面数据处理的状态。最终将处理后的数据顺序输出即可。

文章来源:FPGA极客空间微信公众号

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:bbs.alifpga.com

扫描二维码关注FPGA极客空间。

FPGA在AD采集中的应用的更多相关文章

- 【转】AD转换中常用的十种数字滤波法

在AD采集中经常要用到数字滤波,而不同情况下又有不同的滤波需求,下面是10种经典的软件滤波方法的程序和优缺点分析: 限幅滤波法(又称程序判断滤波法) 中位值滤波法 算术平均滤波法 递推平均滤波法(又称 ...

- 关于74HC4051的逻辑真值表及延时的重要性/在AD测量中的校准

一 关于74HC4051: 在/E=0使能输出的条件下,S2S1S0的三个值,能选通Y0~Y7其中的一个通道从Z输出. 二:问题提出:在按照IC给出的真值表进行芯片操作时,输出逻辑完全对不上 三:分析 ...

- STM32F412应用开发笔记之三:SPI总线通讯与AD采集

本次我们在NUCLEO-F412ZG试验模拟量输入采集.我们的模拟量输入采用ADI公司的AD7705,是一片16位两路差分输入的AD采集芯片.具有SPI接口,我们将采用SPI接口与AD7705通讯.两 ...

- KL25的AD采集操作

飞思卡尔的KL25单片机AD做的是很不错的,SAR型能做到16位.不过数据手册就写得不怎么样了,简直可以说是坑爹,很难看懂.有的描述让人难以理解,你指望在别的地方对不理解的地方会有其他角度的描述,结果 ...

- AD采集问题

在调试AD采集时想问的一些问题 1.电路原理图中的VSS是什么意思? 2.电路原理图中的VDD是什么意思? 3.电路原理图中的VREF+和VREF-是什么意思? 4.电路原理图中的VBAT是用来干什么 ...

- AD设计中,三种大面积覆铜的区别

在AD设计中,主要有三种大面积覆铜方式,分别是Fill(铜皮) Polygon Pour(灌铜)和Plane(平面层),这三种方式刚开始的时候没有细细区分,现在分别应用了一下, 总结如下,欢迎指正 F ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- AD域中添加了一个策略导致的问题

AD域中添加了一个策略,导致浏览器报了一个错,点击下拉菜单选不了.查了资料说是添加信任站点就好,结果信任站点是置灰的,服务器有这个问题,本地是好的. 解决办法:本地服务器有个ie增强设置,关掉就好.

- TI 28335和AD采集

使用TI 28335和片外AD7606,一个AD有8个通道可以采集,激活AD采集: #define EXTADLZ0 *(int *)0x4200 // Zone 0, ADC data, ADCH1 ...

随机推荐

- asp.net mvc 4 项目升级到 asp.net mvc5

一.开始 1.打开或新建asp.net mvc 4项目 2.修改 global.asax文件 原: WebApiConfig.Register(GlobalConfiguration.Configur ...

- 美国站群服务器有利于SEO优化

美国服务器对于站群来说就是指站长为提升每个网站对搜索引擎的权重,更好的有利于seo优化,单独为该服务器下的多个网站分别配置不同的独立ip. 实际上,站群服务器跟其他服务器并没有多大差异,唯一的区别就是 ...

- Java学习记录:文件的输入输出流

Java中的输入.输出流中可以用于文件的读写,拷贝. 由于文件都是由字节组成的,可以将文件中的内容以字节的方式读取出来. 输入流还可以直接转换为图片来使用.其实ImageIcon提供了方法可以直接打开 ...

- 32位汇编第四讲,干货分享,汇编注入的实现,以及快速定位调用API的数量(OD查看)

32位汇编第四讲,干货分享,汇编注入的实现,以及快速定位调用API的数量(OD查看) 昨天,大家可能都看了代码了,不知道昨天有没有在汇编代码的基础上,实现注入计算器. 如果没有,今天则会讲解,不过建议 ...

- mysql初学,mysql修改,mysql查找,mysql删除,mysql基本命令

Mysql 下载地址https://dev.mysql.com/downloads/mysql/ 1.连接Mysql格式: mysql -h主机地址 -u用户名 -p用户密码 1.连接到本机上的MYS ...

- Jsp与beetl的比较

首先介绍一下模板引擎的概念,是为了使用户界面与业务数据分离而产生的,它可以生成特定格式的文档,用于网站的模板引擎,就会生成一个标准的html文档. Jsp全名是JavaServer Page,中文名叫 ...

- 201521123073 《Java程序设计》第1周学习总结

1.本章学习总结 你对于本章知识的学习总结 1.Java中使用Scanner处理输入,需要注意如下几个地方 程序开头必须import java.util.Scanner导入Scanner类. 使用Sc ...

- Python[小甲鱼-002用Python设计第一个游戏]

–Code——————————————————————- print("----------第一个小游戏----------") temp = input("猜一下我现在 ...

- 201521123117 《Java程序设计》第13周学习总结

1. 本周学习总结 2. 书面作业 1. 网络基础 1.1 比较ping www.baidu.com与ping cec.jmu.edu.cn,分析返回结果有何不同?为什么会有这样的不同? 分析结果:从 ...

- 201521123019 《Java程序设计》第10周学习总结

1. 本周学习总结 2. 书面作业 本次PTA作业题集异常.多线程 1.finally 题目4-2 1.1 截图你的提交结果(出现学号) 1.2 4-2中finally中捕获异常需要注意什么? 只有执 ...