数字逻辑实践2->Verilog编写规范

来源:数字逻辑与Verilog设计实验课讲解,个人做的笔记与整理。

00 规范的重要性

良好的编程风格有利于减少消耗的硬件资源,提高设计的工作频率 。

提高系统的可移植性和可维护性。

程序的格式化能体现程序员的基本素质和整个团队的风貌。

01 命名规则

有C语言基础的这部分可以简单略过,看看即可。无基础的可以跳过,有一定编程经验后再来总结提高。

01-00 命名字符集

用于命名的字符集为:字母A~Z和a~z, 数字0~9以及下划线组成。

例如:

1 data_bus

2 data_width

3 clk_48M

4 //使用用意义的名字,利于望文生义,便于维护

5

6 48M_clk//名称不能以数字开头

7 data__bus//不能连续使用下划线

8 data*bus//不能包含非字母符号

01-01 命名大小写规则

参数(parameter)、常量(constant)和块标号(block label)名必须一致采用大写;

而信号,变量和结构名(construct)以及实例标号(instance)必须一致采用小写。

有利于在仿真时,区分不变和变化的 数据。

例子:

1 module display_led( //模块标号小写

2 clk_48M, //时钟

3 ledout //LED输出

4 );

5 input clk_48M; //48M系统时钟

6 output [7:0]ledout;//LED输出控制

7 reg [22:0]count; //计数器

8 reg [7:0]led_reg; //LED输出缓存区

9 wire led_clk; //LED显示时钟控制

10 parameter COUNTER=100;

11 assign led_clk = count[22]; //LED显示时间控制

01-02 名字必须唯一

在不区分大小写的情况下,名字必须唯一。例如,名字state和State不能同时出现在同一设计中。因为有的EDA工具不区分大小写。

01-03 不同类型的信号的命名习惯

如果一个名字由多个字组成,则使用下划线连接,用以增加名字的可读性。

为了使信号的名字有意义,可以根据信号类型选取相应的后缀。

具体示例如下:

| 命名 | 信号类型 | 实例 |

|---|---|---|

| xx_r | 寄存器类型 | Data_out_r |

| xx_a | 异步信号 | Addr_strobe_a |

| xx_clk | 时钟信号 | Sys_clk |

| xx_nc | 不连续信号 | Stata_nc |

| xx_n | 低电平有效信号 | Reset_n |

| xx_pn | 有n个相位的信号 | Enable_p2 |

| xx_z | 三态信号 | Data_out_z |

| xx_next | 状态机信号 | Transmit_next |

| xx_test | 测试模式信号 | Parallel_clk_test |

| sys_xxx | 系统信号 | sys_dout,sys_din |

| clk_xxx | 时钟信号(也可这样写) | clk_768MHZ |

| rst_xxx reset_xxx | 复位信号 | |

| st_xxx set_xxx | 置位信号 |

01-04 多后缀的优先权

这个确实有点抽象...

顺序:

1 //例子

2 ram_1_clk_z_n

3 //结构

4 操作对象序号_数据类型(_clk/_next)_三态信号(_z)_低电平有效信号(_n)

01-05 模块命名习惯

将模块英文名称的各个单词的首字母组合起来,形成3~5个符号的缩写。

Arithmatic logical unit —— ALU

若模块的英文名只有一个单词,可取该单词的前3个字母

Decider —— DEC

01-06 模块间接口命名

所有的变量命名分为两个部分:

第一部分表明数据方向,其中数据发出方在前,数据接收方在后;

第一部分全部大写,

第二部分为数据名称。

第二部分中所有具有明确意义的英文名全部拼写或者缩写的第一个字母大写,其余部分小写。

两个部分用下划线隔离开。

例:CPUMMU_WrReq (CPU发送给MMU的写请求信号)

01-07 模块内部信号

模块内部的信号由几个单词连接而成,缩写要求能基本表明本单词的含义。

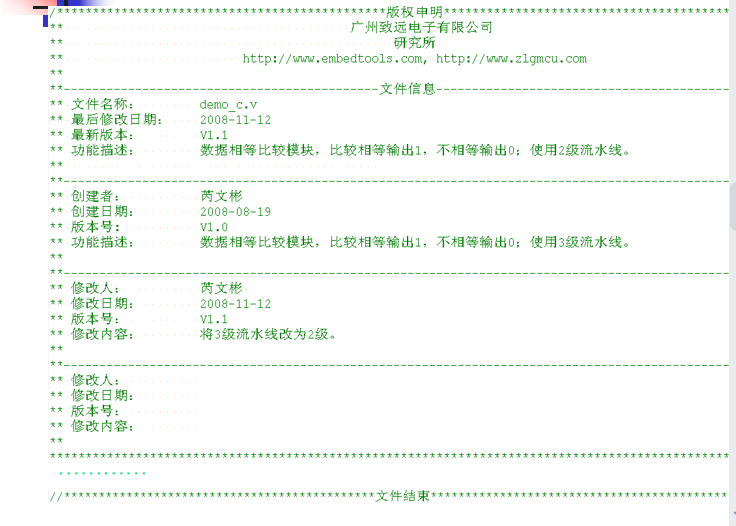

02 注释

主要有三点:

普通描述注释“//”就可以

文件头注释有一点麻烦,但是显得很标准。

模块之间(always)的注释参照文件头注释

1 //****************************************

2 //模块名称:

3 //功能描述:

4 //****************************************

03 代码格式

03-00 端口

1 module buzzer (

2 clk_48M, //时钟输入

3 beep, //蜂鸣器控制输出

4 key, //按键输入

5 ledout //LED显示控制信号

6 );

7 //个人感觉对于复杂电路比较有用,而实验代码就不必如此,直接类似函数参数一样声明即可。可配注释理解。

03-01 连线

1 input clk_48M;

2 input rst;

3 output lcd_en;

4 output [7:0]data_bus;

5 wire clk_lcd;

6 //紧跟module声明,一个Tab键

7 //标准要求是一行声明一个端口

03-02 正文

正文书写要求与C语言类似。

03-03 其他

用四个空格代替TAB键;因为不同的编辑系统的Tab制表符间距可能不同。

每行只有一个Verilog语句;对于长的语句可以使用回车和缩进方法,表示成连续的语句行。

避免使用硬编码;建议使用宏或则参数来定义常数,避免使用硬编码数值。例如:

1 //硬编码方式:

2 input [31:0] data_a; // 输入比较数据A

3 input [31:0] data_b; // 输入比较数据B

4

5 //参数定义方式:

6 parameter DATA_WIDTH = 32; //总线数据宽度

7 input [DATA_WIDTH-1:0] data_a;

8 // 输入比较数据A

9 input [DATA_WIDTH-1:0] data_b;

10 // 输入比较数据B下面是更多出于美观的考虑:

各节之间加1行或者多行空格

不同变量,变量与符号,变量与括号之间都应该保留一个空格 alwaya @ ( … )

逻辑运算符、算术运算符、比较运算符等运算符两侧各留一个空格。(单数操作运算符例外)

使用”//” 注释时,在”//”后应当有一个空格

数字逻辑实践2->Verilog编写规范的更多相关文章

- Verilog 编写规范

在学习Python时,作者有一句话对我影响很大.作者希望我们在学习编写程序的时候注意一些业内约定的规范.在内行人眼中,你的编写格式,就已经暴露了你的程度.学习verilog也是一样的道理,一段好的ve ...

- 数字逻辑实践6-> 从数字逻辑到计算机组成 | 逻辑元件总结与注意事项

00 一些前言 数字逻辑是计算机组成与体系结构的前导课,但是在两者的衔接之间并没有那么流畅,比如对面向硬件电路的设计思路缺乏.这篇总结是在数字逻辑和计组体系结构的衔接阶段进行的. 虽然这篇文是两门课的 ...

- 数字逻辑实践4->面向硬件电路的设计思维--FPGA设计总述

本文是对实验课上讲解的"面向硬件电路的设计思维"的总结,结合数字逻辑课本,进行提炼和整理. 主要来源是课件与本人整理,部分参考了网络大佬的博客. 本文主要介绍不同于之前软件设计思维 ...

- 数字逻辑实践5->Verilog语法 | wire 与 reg 的选择与特性

问题起因:最初学习数字逻辑设计理论的时候还没有注意到,在实验课上写代码的时候发现了一个问题: 对于源码模块的变量定义,何时定义为reg.何时定义为wire?它们各自又有什么特性和物理意义? 1. wi ...

- 数字逻辑实践3->EDA技术与Verilog设计

本文属于EDA技术概述类文章 1 EDA技术及其发展 概念 EDA(Electronic Design Automation),指的是以计算机为工作平台,以EDA软件工具为开发环境,以PLD期间或者A ...

- css编写规范最佳实践

最初,在编写CSS的时候,我们往往想到哪儿就写到哪儿,它们之间的关联性和有序性并不在考虑之中.但随着代码量的增加,亦或是多人共同开发,CSS的编写规范变得重要起来了.本文通过三个方面,总结出CSS编写 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- 代码编写规范说明书(c#.net与asp.net)

代码编写规范说明书(c#.net与asp.net) 目 录1 目的2 范围3 注释规范3.1 概述3.2 自建代码文件注释3.3 模块(类)注释3.4 类属性注释3.5 方法注释3.6 代码间注释4 ...

- 【转】python编写规范——中标软件有限公司测试中心

[转]python编写规范 一.说明 二.内容 1. 代码布局 1.1 缩进 1.2 表达式和语句中的空格 1.3 行的最大长度 1.4 空行... 1.5 编码... 2. 语句... 2.1 标准 ...

随机推荐

- VS 调试 提示 Lc.exe已退出 代码为-1问题解决方法

找到程序项目下Properties文件夹licenses.licx文件,然后右键选择删除就可以了,调试运行正常了 https://jingyan.baidu.com/article/b24f6c822 ...

- 容器化之路Docker网络核心知识小结,理清楚了吗?

Docker网络是容器化中最难理解的一点也是整个容器化中最容易出问题又难以排查的地方,加上使用Kubernets后大部分人即使是专业运维如果没有扎实的网络知识也很难定位容器网络问题,因此这里就容器网络 ...

- 02Prism WPF 入门实战 - 建项

1.概要 Prism介绍 Github: https://github.com/PrismLibrary/Prism 开发文档:https://prismlibrary.com/docs/ Prism ...

- VMware Tanzu社区版初体验

VMware Tanzu社区版 VMware Tanzu Community Edition 是一个功能齐全.易于管理的 Kubernetes 平台,供学习者和用户使用. 它是一个免费的.社区支持的. ...

- 初始HTML04

HTML 列表标签 无序列表 默认用实心圆点标识列表项 1 <ul> 2 <li>list item 列表项</li> 3 <li>list item ...

- Python设置Excel样式

前面已经详细讲解过使用Python对Excel表格进行读.写操作,本文主要讲解下使用Python设置Excel表格的样式. 深入学习请参考openpyxl官方文档: https://openpyxl. ...

- [对对子队]会议记录5.14(Scrum Meeting1)

今天已完成的工作 何瑞 工作内容:初步完成循环指令系统 相关issue:实现循环语句系统的逻辑 相关签入:feat:循环语句的指令编辑系统初步完成 吴昭邦 工作内容:将流水线系统和循环 ...

- Prometheus的单机部署

Prometheus的单机部署 一.什么是Prometheus 二.Prometheus的特性 三.支持的指标类型 1.Counter 计数器 2.Gauge 仪表盘 3.Histogram 直方图 ...

- 你知道怎么从jar包里获取一个文件的内容吗

目录 背景 报错的代码 原先的写法 编写测试类 找原因 最终代码 背景 项目里需要获取一个excle文件,然后对其里的内容进行修改,这个文件在jar包里,怎么尝试都读取不成功,但是觉得肯定可以做到,因 ...

- xmake v2.5.9 发布,改进 C++20 模块,并支持 Nim, Keil MDK 和 Unity Build

xmake 是一个基于 Lua 的轻量级跨平台构建工具,使用 xmake.lua 维护项目构建,相比 makefile/CMakeLists.txt,配置语法更加简洁直观,对新手非常友好,短时间内就能 ...