关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量

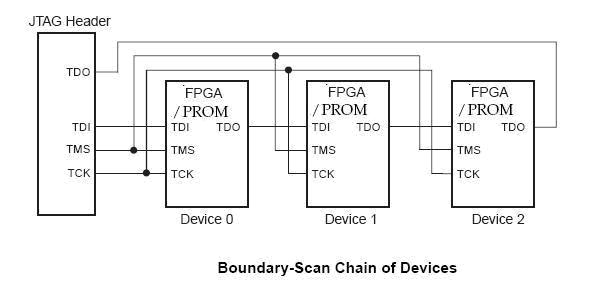

当一个系统中含有多片(2片以上)Xilinx FPGA、CPLD或PROM(FLASH)时,可采用单一JTAG口以菊花链(Daisy Chain)形式将所有芯片串联起来实现下载编程,如下图所示。这样做有两个好处:(1)可以节省多个JTAG口所占用的PCB空间,特别适合空间有限的嵌入式系统,如小型工业摄像机等;(2)嵌入式系统处于封闭环境中,有时需要对系统中的FPGA程序进行在线或远程升级,必须将JTAG口引到机箱外,显然这种单JTAG口的菊花链结构是最佳选择。

1、关于链路中的芯片数量

Xilinx的UG380:“Spartan-6 FPGA Configuration User Guide”的第58页“JTAG Signal Routing”一节有如下描述:

The TCK and TMS signals go to all devices in the chain; consequently, their signal quality

is important. For example, TCK should transition monotonically at all receivers to ensure

proper JTAG functionality and must be properly terminated. The quality of TCK can limit

the maximum frequency for reliable JTAG configuration.

Additionally, if the chain is large (three devices or more), TMS and TCK should be buffered

to ensure that they have sufficient drive strength at all receivers, and the voltage at logic

High must be compatible with all devices in the chain.

由于TCK和TMS两个信号是连接到菊花链中的所有芯片,因此这两个信号的质量(完整性)非常重要!特别是时钟信号TCK,任何毛刺干扰和边沿抖动都会导致下载失败。

当菊花链中的芯片(或设备)在3个以上时,TMS和TCK必须加缓冲(如74LVC245),以增加其驱动能力,对于一些驱动能力差的国产下载器尤其重要。每个驱动门所在分支链路中的芯片(或设备)数量取决于缓冲器的驱动能力,一般74LVC245(8缓冲)的一个缓冲门可驱动3~4个负载(芯片)。在TCK的缓冲器输出端串接一个20~30Ω的电阻,设备端并接一个100~1000p的电容到地,可明显降低边沿抖动、减少毛刺干扰。

TMS是一个模式选择开关信号,TCK是时钟脉冲信号,缺省频率为6MHz,当负载较多时,不加缓冲适当降低TCK的频率也可提高信号完整性。

JTAG协议规定TCK下降沿输出TDI数据有效,并在TCK上升沿采集TDO数据,因此,在整个JTAG链中必须保证TDI至TDO的贯通延时(Propagation Delay)TCPD必须小于TCK的1/2周期TCLK/2,即△T=TCLK/2 –TCPD>0。也就是说,在增加缓冲驱动的情况下,JTAG链路中的芯片总数与每个芯片的TDO延时TDOV(FPGA为TTCKTDO)和TCK频率有关。在芯片总数确定以后,为保证△T>0,只有降低TCK的频率。

下面举一个实例:假设一个封闭嵌入式系统中有三个模块(或电路板):B1、B2、B3,其中B1、B2的JTAG分支都含1片XCF16P PROM、1片V5 FPGA;B3的JTAG分支含1片XCF16P PROM、1片V5 FPGA、1片S6 FPGA外挂1片8M SPI FPASH。 三个模块的TDI、TDO按B1→B2→B3顺序串接;外部接1个JTAG口,其TCK、TMS在母板上经3路缓冲驱动(74LVC1T45)分别至每个模块,TCK串接22Ω电阻。整个JTAG链上串联7个芯片(不算SPI),其中3个XCF16P、3个V5、1个S6,总的TCPD=3×22+3×6+6.5=85.5ns。考虑到缓冲器和线路延时,TCPD >100ns,因此TCK频率取3MHz最合适,其TCLK/2 =167ns。

2、如何设置JTAG的TCK频率

启动Xilinx FPGA/PEROM下载工具iMpact,点击“Output | Cable Setup…”,下拉“Tck Speed/Baud Rate:”设置频率,缺省值为6MHz,如下图所示:

转载自:http://emesjx.spaces.eepw.com.cn/articles/article/item/104293

关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量的更多相关文章

- Xilinx FPGA引脚txt文件导入excel中

需求 为了把xilinx FPGA的官方引脚文件txt转成excel文件(实际官网中有对应的csv文件就是excel文件了...) xilinx FPGA引脚地址:https://china.xili ...

- [原创]FPGA JTAG工具设计(一)

先来看不同JTAG方案,下载配置QSPI Flash所耗时间 基于FTDI方案,JTAG下载时间为494sec JTAG chain configuration ------------------- ...

- Xilinx FPGA 的PCIE 设计

写在前面 近两年来和几个单位接触下来,发现PCIe还是一个比较常用的,有些难度的案例,主要是涉及面比较广,需要了解逻辑设计.高速总线.Linux和Windows的驱动设计等相关知识. 这篇文章主要针对 ...

- SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力.边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据. SoC ...

- Quartus 11.0 的AS 下载方式和JTAG下载jic文件的方式

FPGA下载的三种方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式: AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EP ...

- Xilinx FPGA LVDS应用

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用.Xilinx FPGA中,主要通过原语实现差分信号的收发:OBUFDS(差分输出BUF),IBUFDS(差分输入BUF). 注意在分 ...

- 基于Xilinx FPGA的视频图像采集系统

本篇要分享的是基于Xilinx FPGA的视频图像采集系统,使用摄像头采集图像数据,并没有用到SDRAM/DDR.这个工程使用的是OV7670 30w像素摄像头,用双口RAM做存储,显示窗口为320x ...

- Digilent Xilinx USB Jtag cable

Digilent Xilinx USB Jtag cable 安装环境 操作系统:fedora 20 64bit 源链接:https://wiki.gentoo.org/wiki/Xilinx_USB ...

- Xilinx FPGA复位逻辑处理小结(转)

Xilinx FPGA复位逻辑处理小结 1. 为什么要复位呢? (1)FPGA上电的时候对设计进行初始化: (2)使用一个外部管脚来实现全局复位,复位作为一个同步信号将所有存储单元设置为一个已知的状态 ...

随机推荐

- HDOJ 5693 D Game

众所周知,度度熊喜欢的字符只有两个:B 和D. 今天,它发明了一个游戏:D游戏. 度度熊的英文并不是很高明,所以这里的D,没什么高深的含义,只是代指等差数列[(等差数列百科)](http://baik ...

- HDOJ 2582 f(n)

Discription This time I need you to calculate the f(n) . (3<=n<=1000000) f(n)= Gcd(3)+Gcd(4)+… ...

- python的编码程序例题

有一段python的编码程序如下:urllib.quote(line.decode("gbk").encode("utf-16")),请问经过该编码的字符串的解 ...

- JNI之数据类型

1. JNIEnv 作用 JNIEnv 概念 : 是一个线程相关的结构体, 该结构体代表了 Java 在本线程的运行环境 ; JNIEnv 与 JavaVM : 注意区分这两个概念; -- JavaV ...

- Java下String逗号数组和List<String>的互相转换

说明:很遗憾,组装的时候只能遍历. 方法: public static String listToString(List<String> list){ if(list==null){ re ...

- [Lync]lync同步通讯簿

概述 在客户现场部署lync的时候,突然发现新安装的lync客户端,搜索联系人功能无法使用,而将lync客户端安装后,隔一段时间后,又可以查询了,发现可能是数据没有同步的原因. 解决方案 客户端地址簿 ...

- t-sql 笔记(1)

Toad-for-SQL-Server-Freeware 1.查询哪些数据库对象使用了某个表 SELECT b.[name], a.[definition] FROM sys.all_sql_modu ...

- C#调用页面中的窗体中的方法,获取窗体的元素。

页面中的窗体 <div class="div_width" style="width: 100%; height: 95%;"> <ifram ...

- iOS:Xcode7下创建 .a静态库 和 .framework静态库

Xcode7 中创建静态库:.a 和 .framework 一.简单介绍 1.什么是库? 库是程序代码的集合,是共享程序代码的一种方式 2.库的分类 根据源代码的公开情况,库可以分为2种类型 (1)开 ...

- 基于CentOS与VmwareStation10搭建Oracle11G RAC 64集群环境:3.安装Oracle RAC-3.2.安装 cvuqdisk 软件包

3.2.安装 cvuqdisk 软件包 3.2.1. 准备Oracle Grid安装包 上传Grid .Oracle 安装文件: sftp> put E:\Software\linux.x64 ...