DDR工作原理(转)

源:DDR工作原理

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。DDR SDRAM在原有的SDRAM的基础上改进而来。也正因为如此,DDR能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流。本文只着重讲讲DDR的原理和DDR SDRAM相对于传统SDRAM(又称SDR SDRAM)的不同。

DDR的核心频率、时钟频率和数据传输频率:

核心频率就是内存的工作频率;DDR1内存的核心频率是和时钟频率相同的,到了DDR2和DDR3时才有了时钟频率的概念,就是将核心频率通过倍频技术得到的一个频率。数据传输频率就是传输数据的频率。DDR1预读取是2位,DDR2预读取是4位,DDR3预读取是8位。

DDR1在传输数据的时候在时钟脉冲的上升沿和下降沿都传输一次,所以数据传输频率就是核心频率的2倍。DDR2内存将核心频率倍频2倍所以时钟频率就是核心频率的2倍了,同样还是上升边和下降边各传输一次数据,所以数据传输频率就是核心频率的4倍。

DDR3内存的时钟频率是核心频率的4倍,所以数据传输频率就是核心频率的8倍了。

一、DDR的基本原理

有很多文章都在探讨DDR的原理,但似乎也不得要领,甚至还带出一些错误的观点。首先我们看看一张DDR正规的时序图。

从中可以发现它多了两个信号: CLK#与DQS,CLK#与正常CLK时钟相位相反,形成差分时钟信号。而数据的传输在CLK与CLK#的交叉点进行,可见在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现DDR。在此,我们可以说通过差分信号达到了DDR的目的,甚至讲CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现DDR,还要从其内部的改进说起。

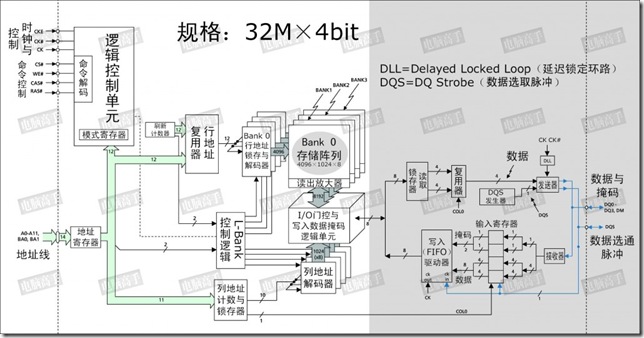

DDR内存芯片的内部结构图

这是一颗128Mbit的内存芯片,从图中可以看出来,白色区域内与SDRAM的结构基本相同,但请注意灰色区域,这是与SDRAM的不同之处。首先就是内部的L-Bank规格。SDRAM中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解SDRAM时 “芯片位宽=存储单元容量” 的公式了。也因此,真正的行、列地址数量也与同规格SDRAM不一样了。

以本芯片为例,在读取时,L-Bank在内部时钟信号的触发下一次传送8bit的数据给读取锁存器,再分成两路4bit数据传给复用器,由后者将它们合并为一路4bit数据流,然后由发送器在DQS的控制下在外部时钟上升与下降沿分两次传输4bit的数据给北桥。这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz。

现在大家基本明白DDR SDRAM的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片I/O总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。

二、DDR SDRAM与SDRAM的不同

DDR SDRAM与SDRAM的不同主要体现在以下几个方面。

DDR SDRAM与SDRAM的主要不同对比表

DDR SDRAM与SDRAM一样,在开机时也要进行MRS,不过由于操作功能的增多,DDR SDRAM在MRS之前还多了一EMRS阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着DLL的有效/禁止、输出驱动强度、QFC 有效/无效等。

由于EMRS与MRS的操作方法与SDRAM的MRS大同小异,在此就不再列出具体的模式表了,有兴趣的话可查看相关的DDR内存资料。下面我们就着重说说DDR SDRAM的新设计与新功能。

1、 差分时钟

差分时钟(参见上文“DDR SDRAM读操作时序图”)是DDR的一个必要设计,但CK#的作用,并不能理解为第二个触发时钟(你可以在讲述DDR原理时简单地这么比喻),而是起到触发时钟校准的作用。由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用(CK上升快下降慢,CK# 则是上升慢下降快)。而由于上下沿触发的原因,也使CL=1.5和2.5成为可能,并容易实现。与CK反相的CK#保证了触发时机的准确性。

2、 数据选取脉冲(DQS)

总结DQS:它是双向信号;读内存时,由内存产生,DQS的沿和数据的沿对齐;写入内存时,由外部产生,DQS的中间对应数据的沿,即此时DQS的沿对应数据最稳定的中间时刻。

DQS是DDR SDRAM中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与 CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为 tAC。注意,这与SDRAM中的tAC的不同。实际上,DQS生成时,芯片内部的预取已经完毕了,tAC是指上文结构图中灰色部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。由于是并行传输,DDR内存对tAC也有一定的要求,对于 DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,有关它们的时序图示见前文,其中CL里包含了一段DQS的导入期。

前文已经说了DQS是为了保证接收方的选择数据, DQS在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?不,如果以DQS的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为DQS的上/下沿。

3、 写入延迟

在上面的DQS写入时序图中,可以发现写入延迟已经不是0了,在发出写入命令后,DQS与写入数据要等一段时间才会送达。这个周期被称为DQS相对于写入命令的延迟时间(tDQSS, WRITE Command to the first corresponding rising edge of DQS),对于这个时间大家应该很好理解了。

为什么要有这样的延迟设计呢?原因也在于同步,毕竟一个时钟周期两次传送,需要很高的控制精度,它必须要等接收方做好充分的准备才行。tDQSS是DDR内存写入操作的一个重要参数,太短的话恐怕接受有误,太长则会造成总线空闲。tDQSS最短不能小于0.75个时钟周期,最长不能超过1.25个时钟周期。有人可能会说,如果这样,DQS不就与芯片内的时钟不同步了吗?对,正常情况下,tDQSS是一个时钟周期,但写入时接受方的时钟只用来控制命令信号的同步,而数据的接受则完全依靠DQS进行同步,所以 DQS与时钟不同步也无所谓。不过,tDQSS产生了一个不利影响——读后写操作延迟的增加,如果CL=2.5,还要在tDQSS基础上加入半个时钟周期,因为命令都要在CK的上升沿发出。

当CL=2.5时,读后写的延迟将为tDQSS+0.5个时钟周期(图中BL=2)

另外,DDR内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)也明显延长,一般在3个时钟周期左右,而在DDR-Ⅱ规范中更是将tWR列为模式寄存器的一项,可见它的重要性。

4、 突发长度与写入掩码

在DDR SDRAM中,突发长度只有2、4、8三种选择,没有了随机存取的操作(突发长度为1)和全页式突发。这是为什么呢?因为L-Bank一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?而全页式突发事实证明在PC内存中是很难用得上的,所以被取消也不希奇。

但是,突发长度的定义也与SDRAM的不一样了(见本章节最前那幅DDR简示图),它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。对于突发写入,如果其中有不想存入的数据,仍可以运用DM信号进行屏蔽。DM信号和数据信号同时发出,接收方在DQS的上升与下降沿来判断DM的状态,如果DM为高电平,那么之前从DQS 中部选取的数据就被屏蔽了。有人可能会觉得,DM是输入信号,意味着芯片不能发出DM信号给北桥作为屏蔽读取数据的参考。其实,该读哪个数据也是由北桥芯片决定的,所以芯片也无需参与北桥的工作,哪个数据是有用的就留给北桥自己去选吧。

5、 延迟锁定回路(DLL)

DDR SDRAM对时钟的精确性有着很高的要求,而DDR SDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDR SDRAM这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM也内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。DDR SDRAM的tAC就是因为内部时钟与外部时钟有偏差而引起的,它很可能造成因数据不同步而产生错误的恶果。实际上,不同步就是一种正/负延迟,如果延迟不可避免,那么若是设定一个延迟值,如一个时钟周期,那么内外时钟的上升与下降沿还是同步的。鉴于外部时钟周期也不会绝对统一,所以需要根据外部时钟动态修正内部时钟的延迟来实现与外部时钟的同步,这就是DLL的任务。

DLL不同于主板上的PLL,它不涉及频率与电压转换,而是生成一个延迟量给内部时钟。目前DLL有两种实现方法,一个是时钟频率测量法(CFM,Clock Frequency Measurement),一个是时钟比较法(CC,Clock Comparator)。

CFM是测量外部时钟的频率周期,然后以此周期为延迟值控制内部时钟,这样内外时钟正好就相差了一个时钟周期,从而实现同步。DLL就这样反复测量反复控制延迟值,使内部时钟与外部时钟保持同步。

CFM式DLL工作示意图

CC的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到下一个内部时钟周期里,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延迟从下一个内部时钟中刨除,如此往复,最终使内外时钟同步。

CC式DLL工作示意图

CFM与CC各有优缺点,CFM的校正速度快,仅用两个时钟周期,但容易受到噪音干扰,并且如果测量失误,则内部的延迟就永远错下去了。CC的优点则是更稳定可靠,如果比较失败,延迟受影响的只是一个数据(而且不会太严重),不会涉及到后面的延迟修正,但它的修正时间要比CFM长。DLL功能在DDR SDRAM中可以被禁止,但仅限于除错与评估操作,正常工作状态是自动有效的。

转自一些论坛:

|

1.并行匹配主要是考虑到负载过重,属于信号完整性的问题;如果接口下就1~2片DDR可以考虑串阻匹配的 2.由于DDR2的电平HSTL电平的,也就是时钟是伪差分的方式,没必要按3W做,等长是必要的,最好做VTT |

理论上3W,指两线中心间距=3*线到地平面距离

一般的3W原则,采用的是,两线中心间距=3*线宽

根据JEDEC[1]建议DDR2的最高工作电压是1.9V,并且建议对于要求内存稳定使用的环境绝不能超过此值(例如服务器或其他任务关键设备)。此外,JEDEC规定内存模块必须在受到永久损害前承受2.3V的电压。

DDR工作原理(转)的更多相关文章

- DDR工作原理

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”.DDR SDRAM在原有的SDRAM的基础上改进而来.也正因为如此,DDR能够凭借着转产成本优势 ...

- 菜鸟学Struts2——Struts工作原理

在完成Struts2的HelloWorld后,对Struts2的工作原理进行学习.Struts2框架可以按照模块来划分为Servlet Filters,Struts核心模块,拦截器和用户实现部分,其中 ...

- 【夯实Nginx基础】Nginx工作原理和优化、漏洞

本文地址 原文地址 本文提纲: 1. Nginx的模块与工作原理 2. Nginx的进程模型 3 . NginxFastCGI运行原理 3.1 什么是 FastCGI ...

- HashMap的工作原理

HashMap的工作原理 HashMap的工作原理是近年来常见的Java面试题.几乎每个Java程序员都知道HashMap,都知道哪里要用HashMap,知道HashTable和HashMap之间 ...

- 【Oracle 集群】ORACLE DATABASE 11G RAC 知识图文详细教程之RAC 工作原理和相关组件(三)

RAC 工作原理和相关组件(三) 概述:写下本文档的初衷和动力,来源于上篇的<oracle基本操作手册>.oracle基本操作手册是作者研一假期对oracle基础知识学习的汇总.然后形成体 ...

- ThreadLocal 工作原理、部分源码分析

1.大概去哪里看 ThreadLocal 其根本实现方法,是在Thread里面,有一个ThreadLocal.ThreadLocalMap属性 ThreadLocal.ThreadLocalMap t ...

- Servlet的生命周期及工作原理

Servlet生命周期分为三个阶段: 1,初始化阶段 调用init()方法 2,响应客户请求阶段 调用service()方法 3,终止阶段 调用destroy()方法 Servlet初始化阶段: 在 ...

- 代码管理工具 --- git的学习笔记二《git的工作原理》

通过几个问题来学习代码管理工具之git 一.git是什么?为什么要用它?使用它的好处?它与svn的区别,在Mac上,比较好用的git图形界面客户端有 git 是分布式的代码管理工具,使用它是因为,它便 ...

- 【原】Learning Spark (Python版) 学习笔记(三)----工作原理、调优与Spark SQL

周末的任务是更新Learning Spark系列第三篇,以为自己写不完了,但为了改正拖延症,还是得完成给自己定的任务啊 = =.这三章主要讲Spark的运行过程(本地+集群),性能调优以及Spark ...

随机推荐

- cfedu/A/求和

题目连接 思路: 用数组直接标记2^n,n属于(0~~31);用LL或者INT都可以,不会爆.但是ans要用LL. #include <set> #include <map> ...

- DrawerLayout和ActionBarDrawerToggle

说明:DrawerLayout的作用就是左侧滑出.右侧滑出菜单.需要和ActionBarDrawerToggle来配合使用.如果对ActionBar不理解,请先熟悉ActionBar. 1.首先配置D ...

- #ifndef 和 #endif

文件中的#ifndef 头件的中的#ifndef,这是一个很关键的东西.比如你有两个C文件,这两个C文件都include了同一个头文件.而编译时,这两个C文件要一同编译成一个可运行文件,于是问题来了, ...

- Python -- Web -- 使用框架

Python的web框架有很多: Flask,Django,Zope2,Web.py,Web2py,Pyramid,Bottle, Tornado... Flask 轻量级,比较简单 from fla ...

- 4D(DRG、DLG、DOM、DEM)数据 概念

抱歉原文链接未知 Technorati 标签: DRG,DLG,DOM,DEM 以下有不同的说法,但是意思都很相近. 一. DOM (数字正射影像图):利用数字高程模型对扫描处理的数字化的航空相片.遥 ...

- 转:Selenium2.0 click()不生效的解决办法

除了http://573301735.com/?p=5126讲的,昨天又发现一个让我1个小时生不如死的问题,就是使用两个不同的配置文件来初始化driver,findelement方法获取到的坐标居然不 ...

- Windows API 之 CreateThread、WaitForSingleObject(未完)

WaitForSingleObject Waits until the specified object is in the signaled state or the time-out interv ...

- 【PDF单页转化为图片输出 注意:英文或图片类的PDF可转化,中文抛异常】

public static void main(String[] args) throws IOException { /** * PDF单页转化为图片输出 注意:英文或图片类的PDF可转化,中文抛异 ...

- hdu_2544_最短路(spfa版子)

题目连接:hdu_2544_最短路 存个自己写的SPFA的板子 #include<cstdio> #include<cstring> #define mst(a,b) mems ...

- OSPF的基本配置及DR /BDR选举的实验

OSPF的基本配置及DR /BDR选举的实验 实验拓扑: 实验目的:掌握OSPF的基本配置 掌握手工指定RID 掌握如何修改OSPF的接口优先级 观察DR BDR选举的过程 实验要求:R3当选为DR ...