stm32寄存器版学习笔记03 外部中断

stm32的每个I/O口都可以作为中断输入,要把I/O口设置为外部中断输入,必须将I/O口设置为上拉/下拉输入 或 浮空输入(但浮空的时候外部一定要带上拉或下拉电阻,否则可能导致 中断不停的触发),干扰大时,上拉/下拉输入模式也建议使用外部上拉/下拉电阻。

1.设置外部中断 的步骤

①初始化I/O口为输入

②开启I/O口复用时钟, 设置I/O口与中断线的映射关系

这一步在函数void Ex_NVIC_Config(u8 GPIOx,u8 BITx,u8 TRIM) 中已经封装好可直接调用。(有详细说明 在第2点)

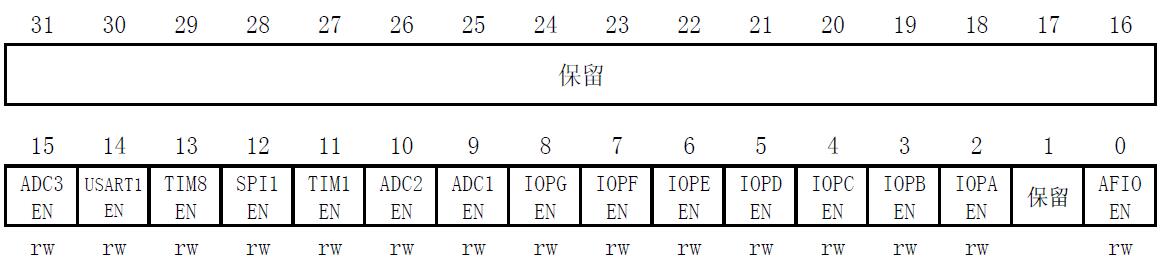

关于I/O口时钟复用

APB2外设时钟使能寄存器(RCC_APB2ENR)

0位 I/O复用时钟使能

Eg:RCC->APB2ENR|=0x01;//使能io复用时钟(已封装在Ex_NVIC_Config函数中)

③开启与该I/O口相对的线上中断/事件,设置触发条件

stm32可以配置成上升沿触发、下降沿触发或任意电平变化触发。

这一步封装在函数void Ex_NVIC_Config(u8 GPIOx,u8 BITx,u8 TRIM) 中,可以直接调用。(有详细说明 在第2点)

typedef struct

{

__IO uint32_t IMR; //中断屏蔽寄存器

__IO uint32_t EMR; //事件屏蔽寄存器

__IO uint32_t RTSR; //上升沿触发选择寄存器

__IO uint32_t FTSR; //下降沿触发选择寄存器

__IO uint32_t SWIER; //软件中断事件寄存器

__IO uint32_t PR; //挂起寄存器

} EXTI_TypeDef;

Eg:Ex_NVIC_Config(GPIO_A,0,RTIR); //设置PA0上升沿触发

Ex_NVIC_Config(GPIO _C,13,FTIR);//设置PC13下降沿触发

可以同时设置上升沿触发和下降沿触发,即任意电平变化触发

④配置中断分组(NVIC),并使能中断

只有配置了NVIC的设置并开启才能被执行,否则不执行到中断服务函数中去。

这一步封装在函数void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group) 里面可以直接调用。 (在第3点 详细介绍)

EG:MY_NVIC_Init(2,2,EXTI0_IRQn,2); //抢占2,子优先级2,组2

MY_NVIC_Init(2,1,EXTI9_5_IRQn,2); //抢占2,子优先级1,组2

注意:stm32的外部中断0-4都有单独的中断服务函数,但是从5开始就没有单独的服务函数了,而是多个中断共用一个服务函数,比如外部中断5-9的中断服务函数为void EXTI9_5_IRQHandler(void),外部中断10-15的中断服务函数为void EXTI15_10_IRQHandler(void).

每一位对应中断 from stm32f10x.h

每一位对应中断 from stm32f10x.h

⑤编写中断服务函数

Eg://外部中断9~5服务程序

void EXTI9_5_IRQHandler(void)

{

//add your code

EXTI->PR=1<<5; //清除LINE5上的中断标志位

}

2. 关于void Ex_NVIC_Config(u8 GPIOx,u8 BITx,u8 TRIM)函数

//外部中断配置函数

//只针对GPIOA~G;不包括PVD,RTC和USB唤醒这三个

//参数:

//GPIOx:0~6,代表GPIOA~G

//BITx:需要使能的位;

//TRIM:触发模式,1,下升沿;2,上降沿;3,任意电平触发

//该函数一次只能配置1个IO口,多个IO口,需多次调用

//该函数会自动开启对应中断,以及屏蔽线

void Ex_NVIC_Config(u8 GPIOx,u8 BITx,u8 TRIM)

{

u8 EXTADDR;

u8 EXTOFFSET;

EXTADDR=BITx/;//得到中断寄存器组的编号

EXTOFFSET=(BITx%)*;

RCC->APB2ENR|=0x01;//使能io复用时钟

AFIO->EXTICR[EXTADDR]&=~(0x000F<<EXTOFFSET);//清除原来设置!!!

AFIO->EXTICR[EXTADDR]|=GPIOx<<EXTOFFSET;//EXTI.BITx映射到GPIOx.BITx

//自动设置

EXTI->IMR|=<<BITx;// 开启line BITx上的中断

//EXTI->EMR|=1<<BITx;//不屏蔽line BITx上的事件 (如果不屏蔽这句,在硬件上是可以的,但是在软件仿真的时候无法进入中断!)

if(TRIM&0x01)EXTI->FTSR|=<<BITx;//line BITx上事件下降沿触发

if(TRIM&0x02)EXTI->RTSR|=<<BITx;//line BITx上事件上升降沿触发

}

① EXTADDR 为计算的中段寄存器组号。AFIO->EXTICR[EXTADDR]。

EXTOFFSET 为偏移地址,就是设置配置寄存器的第几位。

外部中断配置寄存器1(AFIO_EXTICR1)

外部中断配置寄存器2(AFIO_EXTICR2)

外部中断配置寄存器3(AFIO_EXTICR3)

外部中断配置寄存器4(AFIO_EXTICR4)

②中断屏蔽寄存器(EXTI_IMR)

Eg:EXTI->IMR|=1<<BITx;// 开启line BITx上的中断

关于 line x

事件屏蔽寄存器(EXTI_EMR)

③

上升沿触发选择寄存器(EXTI_RTSR)

下降沿触发选择寄存器(EXTI_FTSR)

Eg://TRIM:触发模式,1,下升沿;2,上降沿;3,任意电平触发

if(TRIM&0x01)EXTI->FTSR|=1<<BITx;//line BITx上事件下降沿触发

if(TRIM&0x02)EXTI->RTSR|=1<<BITx;//line BITx上事件上升降沿触发 TRIM = 3,即同时设置上升沿和下降沿触发,即任意电平变化触发。

软件中断事件寄存器(EXTI_SWIER)

挂起寄存器(EXTI_PR)

3. 关于void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group) 函数

//设置向量表偏移地址

//NVIC_VectTab:基址

//Offset:偏移量

void MY_NVIC_SetVectorTable(u32 NVIC_VectTab, u32 Offset)

{

SCB->VTOR = NVIC_VectTab|(Offset & (u32)0x1FFFFF80);//设置NVIC的向量表偏移寄存器

//用于标识向量表是在CODE区还是在RAM区

}

//设置NVIC分组

//NVIC_Group:NVIC分组 0~4 总共5组

void MY_NVIC_PriorityGroupConfig(u8 NVIC_Group)

{

u32 temp,temp1;

temp1=(~NVIC_Group)&0x07;//取后三位

temp1<<=;

temp=SCB->AIRCR; //读取先前的设置

temp&=0X0000F8FF; //清空先前分组

temp|=0X05FA0000; //写入钥匙

temp|=temp1;

SCB->AIRCR=temp; //设置分组

}

//设置NVIC

//NVIC_PreemptionPriority:抢占优先级

//NVIC_SubPriority :响应优先级

//NVIC_Channel :中断编号

//NVIC_Group :中断分组 0~4

//注意优先级不能超过设定的组的范围!否则会有意想不到的错误

//组划分:

//组0:0位抢占优先级,4位响应优先级

//组1:1位抢占优先级,3位响应优先级

//组2:2位抢占优先级,2位响应优先级

//组3:3位抢占优先级,1位响应优先级

//组4:4位抢占优先级,0位响应优先级

//NVIC_SubPriority和NVIC_PreemptionPriority的原则是,数值越小,越优先

void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group)

{

u32 temp;

MY_NVIC_PriorityGroupConfig(NVIC_Group);//设置分组

temp=NVIC_PreemptionPriority<<(-NVIC_Group);

temp|=NVIC_SubPriority&(0x0f>>NVIC_Group);

temp&=0xf;//取低四位

NVIC->ISER[NVIC_Channel/]|=(<<NVIC_Channel%);//使能中断位(要清除的话,相反操作就OK)

NVIC->IP[NVIC_Channel]|=temp<<;//设置响应优先级和抢断优先级

}

在Cortex-M3内核支持256个中断(16个内核中断,240外部中断),并且具有256级的可编程中断设置。stm32并没有使用Cortex-M3内核全部配设。stm32有84个中断(16个内核中断,68可屏蔽中断),具有16级可编程的中断优先级。68可屏蔽中断在stm32f103系列上只有60个。

/* memory mapping struct for Nested Vectored Interrupt Controller (NVIC) */

typedef struct

{ __IO uint32_t ISER[]; /*!< Interrupt Set Enable Register */

uint32_t RESERVED0[];

__IO uint32_t ICER[]; /*!< Interrupt Clear Enable Register */

uint32_t RSERVED1[];

__IO uint32_t ISPR[]; /*!< Interrupt Set Pending Register */

uint32_t RESERVED2[];

__IO uint32_t ICPR[]; /*!< Interrupt Clear Pending Register */

uint32_t RESERVED3[];

__IO uint32_t IABR[]; /*!< Interrupt Active bit Register */

uint32_t RESERVED4[];

__IO uint8_t IP[]; /*!< Interrupt Priority Register, 8Bit wide */

uint32_t RESERVED5[];

__O uint32_t STIR; /*!< Software Trigger Interrupt Register */ } NVIC_Type;

中断的使能与除能

ISER[8]:Interrupt Set-Enable Registers 中断使能寄存器

Cortex-M3内核支持256个中断,8个32位寄存器控制。stm32只用了前68位。ISER[0]的bit0~31对于中断0~31,ISER[1]的bit0~31对于中断32~63,ISER[2]的bit0~3对应中断64~67;要使能某个中断,必须设置相应的ISER位为1,是该中断被使能。

typedef enum IRQn

{

/****** Cortex-M3 Processor Exceptions Numbers ***************************************************/

NonMaskableInt_IRQn = -, /*!< 2 Non Maskable Interrupt */

MemoryManagement_IRQn = -, /*!< 4 Cortex-M3 Memory Management Interrupt */

BusFault_IRQn = -, /*!< 5 Cortex-M3 Bus Fault Interrupt */

UsageFault_IRQn = -, /*!< 6 Cortex-M3 Usage Fault Interrupt */

SVCall_IRQn = -, /*!< 11 Cortex-M3 SV Call Interrupt */

DebugMonitor_IRQn = -, /*!< 12 Cortex-M3 Debug Monitor Interrupt */

PendSV_IRQn = -, /*!< 14 Cortex-M3 Pend SV Interrupt */

SysTick_IRQn = -, /*!< 15 Cortex-M3 System Tick Interrupt */ /****** STM32 specific Interrupt Numbers *********************************************************/

WWDG_IRQn = , /*!< Window WatchDog Interrupt */

PVD_IRQn = , /*!< PVD through EXTI Line detection Interrupt */

TAMPER_IRQn = , /*!< Tamper Interrupt */

RTC_IRQn = , /*!< RTC global Interrupt */

FLASH_IRQn = , /*!< FLASH global Interrupt */

RCC_IRQn = , /*!< RCC global Interrupt */

EXTI0_IRQn = , /*!< EXTI Line0 Interrupt */

EXTI1_IRQn = , /*!< EXTI Line1 Interrupt */

EXTI2_IRQn = , /*!< EXTI Line2 Interrupt */

EXTI3_IRQn = , /*!< EXTI Line3 Interrupt */

EXTI4_IRQn = , /*!< EXTI Line4 Interrupt */

DMA1_Channel1_IRQn = , /*!< DMA1 Channel 1 global Interrupt */

DMA1_Channel2_IRQn = , /*!< DMA1 Channel 2 global Interrupt */

DMA1_Channel3_IRQn = , /*!< DMA1 Channel 3 global Interrupt */

DMA1_Channel4_IRQn = , /*!< DMA1 Channel 4 global Interrupt */

DMA1_Channel5_IRQn = , /*!< DMA1 Channel 5 global Interrupt */

DMA1_Channel6_IRQn = , /*!< DMA1 Channel 6 global Interrupt */

DMA1_Channel7_IRQn = , /*!< DMA1 Channel 7 global Interrupt */ #ifdef STM32F10X_LD

ADC1_2_IRQn = , /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = , /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = , /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = , /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = , /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = , /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = , /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = , /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

#endif /* STM32F10X_LD */ #ifdef STM32F10X_LD_VL

ADC1_IRQn = , /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = , /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = , /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = , /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = , /*!< HDMI-CEC Interrupt */

TIM6_DAC_IRQn = , /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = /*!< TIM7 Interrupt */

#endif /* STM32F10X_LD_VL */ #ifdef STM32F10X_MD

ADC1_2_IRQn = , /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = , /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = , /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = , /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = , /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = , /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = , /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = , /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

#endif /* STM32F10X_MD */ #ifdef STM32F10X_MD_VL

ADC1_IRQn = , /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = , /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = , /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = , /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = , /*!< HDMI-CEC Interrupt */

TIM6_DAC_IRQn = , /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = /*!< TIM7 Interrupt */

#endif /* STM32F10X_MD_VL */ #ifdef STM32F10X_HD

ADC1_2_IRQn = , /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = , /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = , /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = , /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = , /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = , /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = , /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = , /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = , /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

TIM8_BRK_IRQn = , /*!< TIM8 Break Interrupt */

TIM8_UP_IRQn = , /*!< TIM8 Update Interrupt */

TIM8_TRG_COM_IRQn = , /*!< TIM8 Trigger and Commutation Interrupt */

TIM8_CC_IRQn = , /*!< TIM8 Capture Compare Interrupt */

ADC3_IRQn = , /*!< ADC3 global Interrupt */

FSMC_IRQn = , /*!< FSMC global Interrupt */

SDIO_IRQn = , /*!< SDIO global Interrupt */

TIM5_IRQn = , /*!< TIM5 global Interrupt */

SPI3_IRQn = , /*!< SPI3 global Interrupt */

UART4_IRQn = , /*!< UART4 global Interrupt */

UART5_IRQn = , /*!< UART5 global Interrupt */

TIM6_IRQn = , /*!< TIM6 global Interrupt */

TIM7_IRQn = , /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = , /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = , /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = , /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

#endif /* STM32F10X_HD */ #ifdef STM32F10X_HD_VL

ADC1_IRQn = , /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = , /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = , /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = , /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = , /*!< HDMI-CEC Interrupt */

TIM12_IRQn = , /*!< TIM12 global Interrupt */

TIM13_IRQn = , /*!< TIM13 global Interrupt */

TIM14_IRQn = , /*!< TIM14 global Interrupt */

TIM5_IRQn = , /*!< TIM5 global Interrupt */

SPI3_IRQn = , /*!< SPI3 global Interrupt */

UART4_IRQn = , /*!< UART4 global Interrupt */

UART5_IRQn = , /*!< UART5 global Interrupt */

TIM6_DAC_IRQn = , /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = , /*!< TIM7 Interrupt */

DMA2_Channel1_IRQn = , /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = , /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = , /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = , /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

DMA2_Channel5_IRQn = /*!< DMA2 Channel 5 global Interrupt (DMA2 Channel 5 is

mapped at position 60 only if the MISC_REMAP bit in

the AFIO_MAPR2 register is set) */

#endif /* STM32F10X_HD_VL */ #ifdef STM32F10X_XL

ADC1_2_IRQn = , /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = , /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = , /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = , /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = , /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = , /*!< TIM1 Break Interrupt and TIM9 global Interrupt */

TIM1_UP_TIM10_IRQn = , /*!< TIM1 Update Interrupt and TIM10 global Interrupt */

TIM1_TRG_COM_TIM11_IRQn = , /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = , /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

TIM8_BRK_TIM12_IRQn = , /*!< TIM8 Break Interrupt and TIM12 global Interrupt */

TIM8_UP_TIM13_IRQn = , /*!< TIM8 Update Interrupt and TIM13 global Interrupt */

TIM8_TRG_COM_TIM14_IRQn = , /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

TIM8_CC_IRQn = , /*!< TIM8 Capture Compare Interrupt */

ADC3_IRQn = , /*!< ADC3 global Interrupt */

FSMC_IRQn = , /*!< FSMC global Interrupt */

SDIO_IRQn = , /*!< SDIO global Interrupt */

TIM5_IRQn = , /*!< TIM5 global Interrupt */

SPI3_IRQn = , /*!< SPI3 global Interrupt */

UART4_IRQn = , /*!< UART4 global Interrupt */

UART5_IRQn = , /*!< UART5 global Interrupt */

TIM6_IRQn = , /*!< TIM6 global Interrupt */

TIM7_IRQn = , /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = , /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = , /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = , /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

#endif /* STM32F10X_XL */ #ifdef STM32F10X_CL

ADC1_2_IRQn = , /*!< ADC1 and ADC2 global Interrupt */

CAN1_TX_IRQn = , /*!< USB Device High Priority or CAN1 TX Interrupts */

CAN1_RX0_IRQn = , /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = , /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = , /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = , /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = , /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = , /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = , /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = , /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = , /*!< TIM2 global Interrupt */

TIM3_IRQn = , /*!< TIM3 global Interrupt */

TIM4_IRQn = , /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = , /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = , /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = , /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = , /*!< I2C2 Error Interrupt */

SPI1_IRQn = , /*!< SPI1 global Interrupt */

SPI2_IRQn = , /*!< SPI2 global Interrupt */

USART1_IRQn = , /*!< USART1 global Interrupt */

USART2_IRQn = , /*!< USART2 global Interrupt */

USART3_IRQn = , /*!< USART3 global Interrupt */

EXTI15_10_IRQn = , /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = , /*!< RTC Alarm through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = , /*!< USB OTG FS WakeUp from suspend through EXTI Line Interrupt */

TIM5_IRQn = , /*!< TIM5 global Interrupt */

SPI3_IRQn = , /*!< SPI3 global Interrupt */

UART4_IRQn = , /*!< UART4 global Interrupt */

UART5_IRQn = , /*!< UART5 global Interrupt */

TIM6_IRQn = , /*!< TIM6 global Interrupt */

TIM7_IRQn = , /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = , /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = , /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = , /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_IRQn = , /*!< DMA2 Channel 4 global Interrupt */

DMA2_Channel5_IRQn = , /*!< DMA2 Channel 5 global Interrupt */

ETH_IRQn = , /*!< Ethernet global Interrupt */

ETH_WKUP_IRQn = , /*!< Ethernet Wakeup through EXTI line Interrupt */

CAN2_TX_IRQn = , /*!< CAN2 TX Interrupt */

CAN2_RX0_IRQn = , /*!< CAN2 RX0 Interrupt */

CAN2_RX1_IRQn = , /*!< CAN2 RX1 Interrupt */

CAN2_SCE_IRQn = , /*!< CAN2 SCE Interrupt */

OTG_FS_IRQn = /*!< USB OTG FS global Interrupt */

#endif /* STM32F10X_CL */

} IRQn_Type;

每一位对应中断 from stm32f10x.h

ICER[8]: Interrupt Clear-Enable Registers 中断除能寄存器

专门设置一个ICER来清除中断位,而不是向ISER写0来清除,是因为NVIC的这些寄存器都是写1有效,写0无效。

中断的悬起与解悬

ISPR[8]: Interrupt Set-Pending Registers 中断挂起控制寄存器

通过置1可以将正在进行的中断挂起,而执行同级,或更高级别的中断,写0无效。

ICPR[8]: Interrupt Clear-Pending Registers 中断解挂控制寄存器

通过置1可以将挂起的中断解挂,写0无效。

IABR[8]: Interrupt Active Bit Registers 中断激活标志位寄存器

对应位代表和ISER一样,如果为1,代表中断正在被执行。只读寄存器,通过读取它知道当前在执行的中断是哪个。中断执行完由硬件清0。

IP[240]: Interrupt Priority Registers 中断优先级控制寄存器

IP[67]~IP[0]分别对应中断67~0,每个可屏蔽中断占用8bit的高4位。这4位分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各站几个位根据SCB->AIRCR中的中断分组设置来决定。

Eg:组设置为3,那么此时所有68个中断的每个中断的中断优先寄存器的高4位中最高3位是抢占优先级,低1位是响应优先级。每个中断可以设置抢占优先级0~7,响应优先级为0或1。数值越小,优先级越高。

高优先级的抢占优先级是可以打断正在进行的低优先级中断的;而抢占优先级相同的中断,高优先级的响应中断不可以打断低响应优先级的中断。

//设置NVIC分组

//NVIC_Group:NVIC分组 0~4 总共5组

void MY_NVIC_PriorityGroupConfig(u8 NVIC_Group)

{

u32 temp,temp1;

temp1=(~NVIC_Group)&0x07;//取后三位

temp1<<=;

temp=SCB->AIRCR; //读取先前的设置

temp&=0X0000F8FF; //清空先前分组

temp|=0X05FA0000; //写入钥匙

temp|=temp1;

SCB->AIRCR=temp; //设置分组

}

设置NVIC分组

//设置NVIC

//NVIC_PreemptionPriority:抢占优先级

//NVIC_SubPriority :响应优先级

//NVIC_Channel :中断编号

//NVIC_Group :中断分组 0~4

//注意优先级不能超过设定的组的范围!否则会有意想不到的错误

//组划分:

//组0:0位抢占优先级,4位响应优先级

//组1:1位抢占优先级,3位响应优先级

//组2:2位抢占优先级,2位响应优先级

//组3:3位抢占优先级,1位响应优先级

//组4:4位抢占优先级,0位响应优先级

//NVIC_SubPriority和NVIC_PreemptionPriority的原则是,数值越小,越优先

void MY_NVIC_Init(u8 NVIC_PreemptionPriority,u8 NVIC_SubPriority,u8 NVIC_Channel,u8 NVIC_Group)

{

u32 temp;

MY_NVIC_PriorityGroupConfig(NVIC_Group);//设置分组

temp=NVIC_PreemptionPriority<<(-NVIC_Group);

temp|=NVIC_SubPriority&(0x0f>>NVIC_Group);

temp&=0xf;//取低四位

NVIC->ISER[NVIC_Channel/]|=(<<NVIC_Channel%);//使能中断位(要清除的话,相反操作就OK)

NVIC->IP[NVIC_Channel]|=temp<<;//设置响应优先级和抢断优先级

}

设置NVIC MY_NVIC_Init

根据中断分组情况来设置 中断优先级控制寄存器IP 其高四位。

用MY_NVIC_PriorityGroupConfig函数分组

开启中断,在ISER相应位置1

4.外部中断的应用

//key--->led 外部中断

//外部中断0服务程序

void EXTI0_IRQHandler(void)

{

delay_ms(); //消抖

if(WK_UP==) //WK_UP按键

{

LED0=!LED0;

LED1=!LED1;

}

EXTI->PR=<<; //清除LINE0上的中断标志位

}

//外部中断9~5服务程序

void EXTI9_5_IRQHandler(void)

{

delay_ms(); //消抖

if(KEY0==) //按键0

{

LED0=!LED0;

}

EXTI->PR=<<; //清除LINE5上的中断标志位

}

//外部中断15~10服务程序

void EXTI15_10_IRQHandler(void)

{

delay_ms(); //消抖

if(KEY1==) //按键1

{

LED1=!LED1;

}

EXTI->PR=<<; //清除LINE15上的中断标志位

}

//外部中断初始化程序

//初始化PA0,PC5,PA15为中断输入.

void EXTI_Init(void)

{

KEY_Init();

Ex_NVIC_Config(GPIO_A,,RTIR); //上升沿触发

Ex_NVIC_Config(GPIO_C,,FTIR); //下降沿触发

Ex_NVIC_Config(GPIO_A,,FTIR); //下降沿触发 MY_NVIC_Init(,,EXTI0_IRQn,); //抢占2,子优先级2,组2

MY_NVIC_Init(,,EXTI9_5_IRQn,); //抢占2,子优先级1,组2

MY_NVIC_Init(,,EXTI15_10_IRQn,); //抢占2,子优先级0,组2

}

stm32寄存器版学习笔记03 外部中断的更多相关文章

- stm32寄存器版学习笔记07 ADC

STM32F103RCT有3个ADC,12位主逼近型模拟数字转换器,有18个通道,可测量16个外部和2个内部信号源.各通道的A/D转换可以单次.连续.扫描或间断模式执行. 1.通道选择 stm32把A ...

- stm32寄存器版学习笔记06 输入捕获(ETR脉冲计数)

STM32外部脉冲ETR引脚:TIM1-->PA12;TIMER2-->PA0:TIMER3-->PD2;TIMER4-->PE0… 1.TIM2 PA0计数 配置步骤 ①开启 ...

- stm32寄存器版学习笔记05 PWM

STM32除TIM6和TIM7外都可以产生PWM输出.高级定时器TIM1和TIM8可以同时产生7路PWM,通用定时器可以产生4路PWM输出. 1.TIM1 CH1输出PWM配置步骤 ①开启TIM1时钟 ...

- stm32寄存器版学习笔记04 定时计数器中断

STM32共有8个定时计数器,其中TIME1和TIME8是高级定时器,TIME2~TIME5是通用定时器,TIME6和TIME7是基本定时器.以TIME3为例总结定时计数器的基本用法. 1.TIM3的 ...

- stm32寄存器版学习笔记08 DMA

DMA(Direct Memory Access),直接存储器访问.DMA传输方式无需CPU直接控制传输,通过硬件为RAM与I/O设备开辟一条直接传送数据的通路,使CPU效率大大提高.stm32f10 ...

- stm32寄存器版学习笔记02 串口通信

stm32F103RCT6提供5路串口.串口的使用,只要开启串口时钟,设置相应的I/O口的模式,然后配置下波特率.数据位长度.奇偶校验等信息,即可使用. 1.串口的配置步骤 ①串口时钟使能 APB2外 ...

- stm32寄存器版学习笔记01 GPIO口的配置(LED、按键)

STM32的I/O口可以由软件配置成如下8种模式:输入浮空.输入上拉.输入下拉.模拟输入.开漏输出.推挽输出.推挽式复用功能及开漏复用功能.每个I/O口由7个寄存器来控制:配置模式的端口配置寄存器CR ...

- stm32寄存器版学习笔记10 SPI

SPI(Serial Peripheral Interface),串行外围设备接口.SPI是一种高速的.全双工.同步的通信总线. SPI接口一般使用4条线通信: MISO 主设备数据输入,从设备数据输 ...

- stm32寄存器版学习笔记09 IIC

I²C(Inter-Integrated Circuit)总线是一种两线式串行总线,用于连接微控制器及其外设,是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据. IIC总线在传送数据过程中 ...

随机推荐

- docker shipyard 问题

安装 docker shipyard curl -s https://shipyard-project.com/deploy | bash -s docker machine 创建的虚拟机无法直接运 ...

- Gogeos安装

环境要求: Windows64,Go,minGW(统一64位) 1.安装geos 下载GEOS 3.3.8源码,解压后,按readme文件编译(基于VS2010的64位编译工具执行的nmake编译命令 ...

- Nginx 与 tomcat 部署网站

http://www.blogjava.net/libin2722/articles/355631.html http://congpeixue.iteye.com/blog/255011 keepa ...

- hibernate:inverse、cascade,一对多、多对多详解

1.到底在哪用cascade="..."? cascade属性并不是多对多关系一定要用的,有了它只是让我们在插入或删除对像时更方便一些,只要在cascade的源头上插入或是删除,所 ...

- 定时模块app_timer用法及常见问题—nRF5 SDK模块系列二

app_timer是大家经常用到的一个库,app_timer的功能就是定时,也就是说,你在某一时刻启动一个app timer并设定超时时间,超时时间一到,app_timer就会回调timeout ha ...

- python基础方法

一.忽略大小写相等upper(),lower() def cmp(str1,str2): return str1.upper()==str2.upper() list1 = 'MAC' list2 = ...

- 格雷码C++实现

格雷码C++实现 题目 给定一个整数n,请返回n位的格雷码,顺序从0开始,要求递归实现. 格雷码: 在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code ...

- 设计模式--单例模式C++实现

单例模式C++实现 1描述: 单例模式,又称单件模式. 定义:确保某一个类只有一个实例,而且自行实例化并向整个系统提供这个实例. 2具体类图描述: 2.1 StartUML内部生成模式类图 该类图由S ...

- zookeeper常见错误

1.在注册中心找不到对应的服务 这种错误是服务层代码没有成功注册到注册中心导致,请检查一下你的服务层代码是否添加了@service注解,并且该注解的包一定是com.alibaba.dubbo.conf ...

- 玲珑oj 1117 线段树+离线+离散化,laz大法

1117 - RE:从零开始的异世界生活 Time Limit:1s Memory Limit:256MByte Submissions:438Solved:68 DESCRIPTION 486到了异 ...