zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的。

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

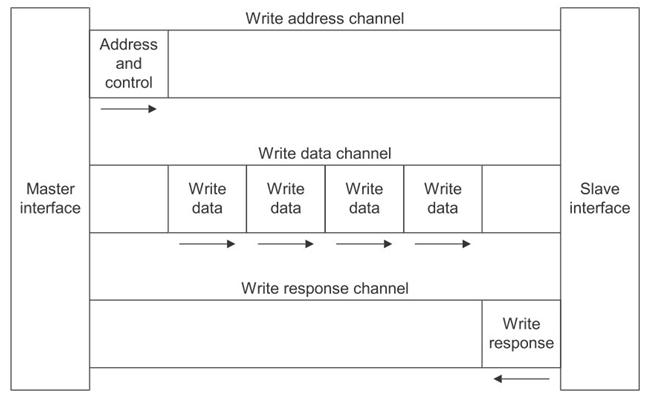

AXI总线是一种基于burst的传输总线,分为5个通道:read address, read data, write address, write data, write response。

- read data channel是一种从slave到master的传输,在一个读操作中,response与read data同一通道,分别为transfer返回response

- write data channel是一种从master到slave的传输,在一个写操作中,返回一个整体的response。

- AXI中的每个通道都包含一个信息信号和一个双路的VALD、READY握手机制。信息源通过VALID信号来指示通道中的数据和控制信息什么时候有效。目地源用READY信号来表示何时能够接收数据。读数据和写数据通道都包括一个LAST信号,用来指明一个事物传输的最后一个数据。

- 写数据通路传送着主机向设备的写数据。每八个数据都会有一个byte lane ,用来指明数据总线上面的哪些byte有效。写响应通道提供了设备响应写事务的一种方式。这完成信号每一次突发式读写会产生一个。

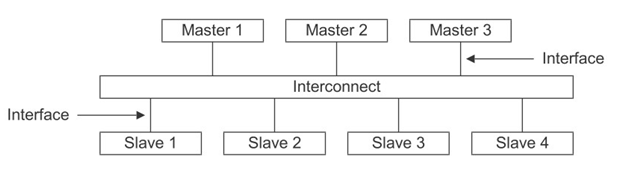

- 主机和设备的接口和互联图如下:

- 传输地址信息和数据都是在VALID和READY同时为高时有效。

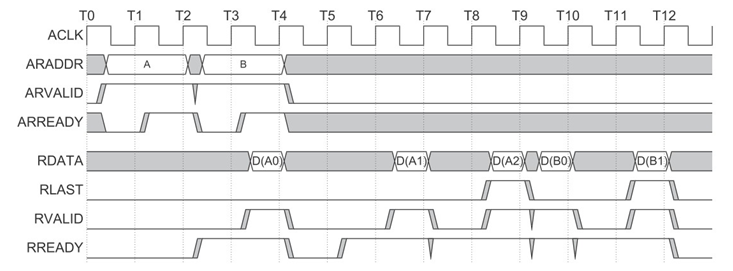

- 突发式读的时序图如下:

当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备保持VALID为低直到读数据有效。为了表明一次突发式读写的完成,设备用RLAST信号来表示最后一个被传输的数据。

- 重叠突发式读时序图如下:

设备会在第一次突发式读完成后处理第二次突发式读数据。也就意味着,主机一开始传送了两个地址给设备。设备在完全处理完第一个地址的数据之后才开始处理第二个地址的数据。

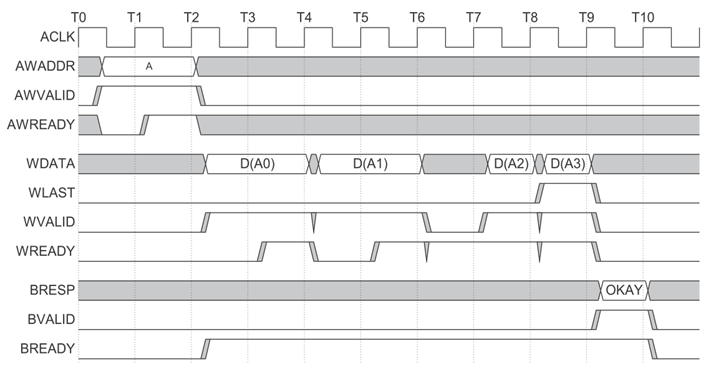

- 突发式写时序图如下:

这一过程的开始时,主机发送地址和控制信息到写地址通道中,然后主机发送每一个写数据到写数据通道中。当主机发送最后一个数据时,WLAST信号就变为高。当设备接收完所有数据之后他将一个写响应发送回主机来表明写事务完成。

- AXI协议支持乱序传输。他给每一个通过接口的事务一个IDtag。协议要求相同ID tag的事务必须有序完成,而不同ID tag可以乱序完成。

信号说明:

1、全局信号

|

信号 |

源 |

描述 |

|

ACLK |

Clock source |

全局时钟信号 |

|

ARESETn |

Reset source |

全局复位信号,低电平有效 |

2、写地址通道信号

|

信号 |

源 |

描述 |

|

AWID[3:0] |

主机 |

写地址ID,这个信号是写地址信号组的ID tag。 |

|

AWADDR[31:0] |

主机 |

写地址。 |

|

AWLEN[3:0] |

主机 |

突发式写的长度。此长度决定突发式写所传输的数据的个数。 |

|

AWSIZE[2:0] |

主机 |

突发式写的大小。 |

|

AWBURST[1:0] |

主机 |

突发式写的类型。 |

|

AWLOCK[1:0] |

主机 |

锁类型。 |

|

AWCACHE[3:0] |

主机 |

Cache类型。这信号指明事务的bufferable、cacheable、write-through、write-back、allocate attributes信息。 |

|

AWPROT[2:0] |

主机 |

保护类型。 |

|

AWVALID |

主机 |

写地址有效。 1 = 地址和控制信息有效 0 = 地址和控制信息无效 这个信号会一直保持,直到AWREADY变为高。 |

|

AWREADY |

设备 |

写地址准备好。这个信号用来指明设备已经准备好接受地址和控制信息了。 1 = 设备准备好 0 = 设备没准备好 |

3、写数据通道信号

|

信号 |

源 |

描述 |

|

WID[3:0] |

主机 |

写ID tag,WID的值必须与AWID的值匹配 |

|

WDATA[31:0] |

主机 |

写的数据。 |

|

WSTRB[3:0] |

主机 |

写阀门。WSTRB[n]标示的区间为WDATA[(8*n)+7:(8*n)] |

|

WLAST |

主机 |

写的最后一个数据。 |

|

WVALID |

主机 |

写有效 1 = 写数据和阀门有效 0 = 写数据和阀门无效 |

|

WREADY |

设备 |

写就绪。指明设备已经准备好接受数据了 1 = 设备就绪 0 = 设备未就绪 |

4、写响应通道信号

|

信号 |

源 |

描述 |

|

BID[3:0] |

设备 |

响应ID , 这个数值必须与AWID的数值匹配。 |

|

BRESP[1:0] |

设备 |

写响应。这个信号指明写事务的状态。可能有的响应:OKAY、EXOKAY、SLVERR、DECERR。 |

|

BVALID |

设备 |

写响应有效。 1 = 写响应有效 0 = 写响应无效 |

|

BREADY |

主机 |

接受响应就绪。该信号表示主机已经能够接受响应信息。 1 = 主机就绪 0 = 主机未就绪 |

5、读地址通道信号

|

信号 |

源 |

描述 |

|

ARID[3:0] |

主机 |

读地址ID。 |

|

ARADDR[31:0] |

主机 |

读地址。 |

|

ARLEN[3:0] |

主机 |

突发式读长度。 |

|

ARSIZE[2:0] |

主机 |

突发式读大小。 |

|

ARBURST[1:0] |

主机 |

突发式读类型。 |

|

ARLOCK[1:0] |

主机 |

锁类型。 |

|

ARCACHE[3:0] |

主机 |

Cache类型。 |

|

ARPROT[2:0] |

主机 |

保护类型。 |

|

ARVALID |

主机 |

读地址有效。信号一直保持,直到ARREADY为高。 1 = 地址和控制信息有效 0 = 地址和控制信息无效 |

|

ARREADY |

设备 |

读地址就绪。指明设备已经准备好接受数据了。 1 = 设备就绪 0 = 设备未就绪 |

6、读数据通道信号

|

信号 |

源 |

描述 |

|

RID[3:0] |

设备 |

读ID tag。RID的数值必须与ARID的数值匹配。 |

|

RDATA[31:0] |

设备 |

读数据。 |

|

RRESP[1:0] |

设备 |

读响应。这个信号指明读传输的状态:OKAY、EXOKAY、SLVERR、DECERR。 |

|

RLAST |

设备 |

读事务传送的最后一个数据。 |

|

RVALID |

设备 |

读数据有效。 1 = 读数据有效。 0 = 读数据无效。 |

|

RREADY |

主机 |

读数据就绪。 1 = 主机就绪 0 = 主机未就绪 |

7、低功耗接口信号

|

信号 |

源 |

描述 |

|

CSYSREQ |

CLOCK controller |

系统低功耗请求。此信号来自系统时钟控制器,使外围设备进入低功耗状态。 |

|

CSYSACK |

外围设备 |

低功耗请求应答。 |

|

CACTIVE |

外围设备 |

Clock active 1 = 外围设备时钟请求 0 = 外围设备时钟无请求 |

zedboard如何从PL端控制DDR读写(二)——AXI总线的更多相关文章

- zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

之前的项目和培训中,都只用到了AXI-Lite或者AXI-Stream,对于AXI-FULL知之甚少,主要是每次一看到那么多接口信号就望而却步了. 现在为了调试DDR,痛下决心要把AXI-FULL弄懂 ...

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

- zedboard如何从PL端控制DDR读写(五)

有了前面的一堆铺垫.现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK. 一.首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就 ...

- zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码.其实很简单,上一节已经分析了地址停留在000 ...

- zedboard如何从PL端控制DDR读写(四)

PS-PL之间的AXI 接口分为三种:• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信.接口是透传的不带缓冲.总共有四个通 ...

- zedboard如何从PL端控制DDR读写(一)

看了一段时间的DDR手册,感觉大体有一点了解了,想要实际上板调试,然而实验室可用的开发板不多,拿了一块zynq板看了看,DDR确实有,但是已经集成了控制器,而且控制器还放到了PS端,PL只能通过AXI ...

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- MIG IP控制DDR3读写测试

本文设计思想采用明德扬至简设计法.在高速信号处理场合下,很短时间内就要缓存大量的数据,这时片内存储资源已经远远不够了.DDR SDRAM因其极高的性价比几乎是每一款中高档FPGA开发板的首选外部存储芯 ...

随机推荐

- Codeforces Round #365 (Div. 2) Chris and Road

Chris and Road 题意: 给一个n个顶点的多边形的车,有速度v,人从0走到对面的w,人速度u,问人最快到w的时间是多少,车如果挡到人,人就不能走. 题解: 这题当时以为计算几何,所以就没做 ...

- Linux查看程序端口占用情况(转载)

From:http://www.cnblogs.com/benio/archive/2010/09/15/1826728.html 今天发现服务器上Tomcat 8080端口起不来,老提示端口已经被占 ...

- MySql 存储过程实例(附完整注释)

将下面的语句复制粘贴可以一次性执行完,我已经测试过,没有问题! MySql存储过程简单实例: ...

- WebBrowserControl

Before navigating the URL, write meta into webbrowser's documenttext property as follows: //Setting ...

- 使用matplot绘图 @python

1. 使用csv 模块读取数据 2. 定义label 3. 绘图,调参 #!/usr/bin/env python # coding=utf-8 import sys import matplotli ...

- [Java] 将标准字符流写入到文件中(通过控制台写一个html程序,并保存)

package test.stream; import java.io.BufferedReader; import java.io.BufferedWriter; import java.io.Fi ...

- 用Java开发gRPC服务的例子分析

本文的代码例子来自:https://github.com/grpc/grpc-java 定义服务 这一步与其他语言完全一样,需要定义gRPC的服务.方法.request和response的类型. 完 ...

- Node.js上传文件

var formidable = require('formidable'); var util = require('util'); exports.upload = function(req,re ...

- Hadoop有关的网站

软件下载: http://archive.apache.org hbase对Hadoop的支持矩阵: https://hbase.apache.org/book.html#configuration

- apk重新签名

re-sign.jar中后自动去除签名这个方法,经试验不可用! 1.去除准备重新签名SinaVoice.apk软件本身的签名 将apk文件后缀改为.zip,然后从winrar中删除META-INF文件 ...