FPGA中的时序分析(二)

使用Timequest

笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解。

Timequest分析时序的核心,也就是在于延迟因数的计算。那么建立约束文件,去告诉timequest,哪个地方有什么样的约束,该怎么进行约束。

之所以要建立相关网表的概念,是因为我们在利用quartus ii 中的timequest 时,大致的流程是:建立网表----建立SDC文件----更新网表;

2.1 SDC网表

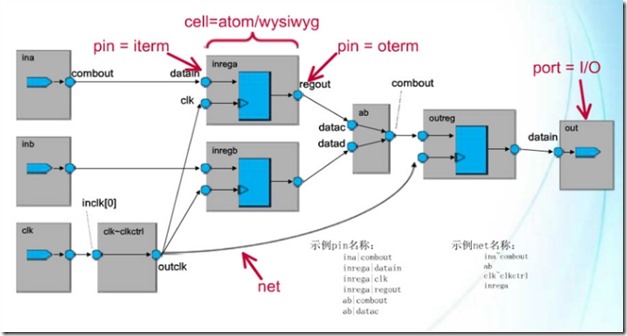

SDC网表包括:端口(port),引脚(pin),单元(cell),网(net),下图可以解释各个部分的概念。

那么接下来我们要使用timequest,同使用signaltap ii一样,在使用之前先建立一个SDC文件,文件名可以任意取,建议和模块名一样吧。然后另存为你所命名的名字。

2.2 建立 timing netlist

然后 在使用timequest之前,先要编译一下源文件,建立好适配文件才可以,请注意!!!

然后点击timequest按钮进入到timequest中,如下面所示,

上述三个命令是比较重要的命令,第一个是创建网表,开始布线,建立硬模型,第二个是读SDC文件,第三个是更新网表,每当有所改动,需要更新一次。

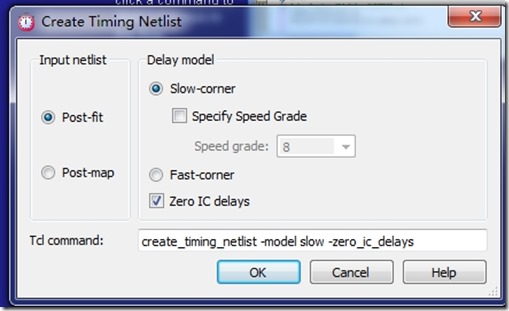

图16.5 适配情况

上面的post-fit,更接近物理模型,经过优化之后的,

上面的post-map,是没有经过优化的,更接近与原型。

会无视一些网表基本单位的延时。

会无视一些网表基本单位的延时。

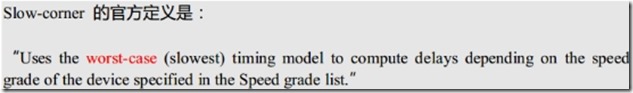

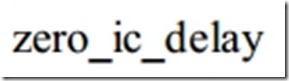

关于是适配较好的情况还是适配较差的情况,这个根据设计去设定,一般最差情况能够通过,那么较好的情况也一定能够通过。

一般按照图16.5就够用了。这也是双击 产生的结果。当然也可以自己手动去设定,那就是

产生的结果。当然也可以自己手动去设定,那就是 即可。

即可。

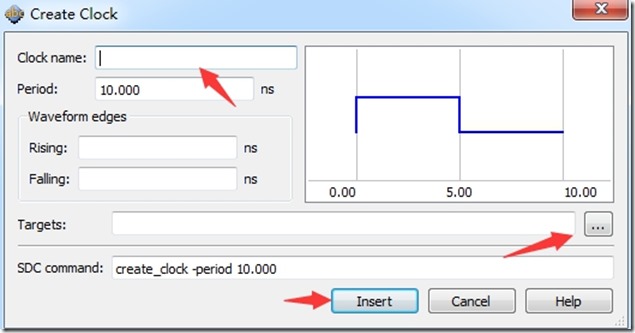

2.3 建立 SDC文件

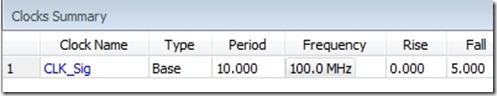

注意上述的clock name是和全局时钟网络的名字是一致的,targets这里选择你所设定的全局时钟网络。

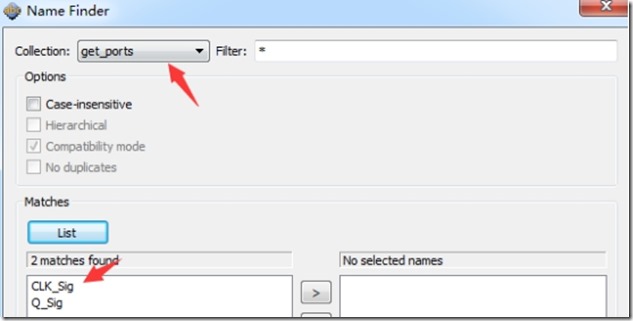

选择get_ports,点击list按钮,选择时钟信号。要约束其他信号方法一样。

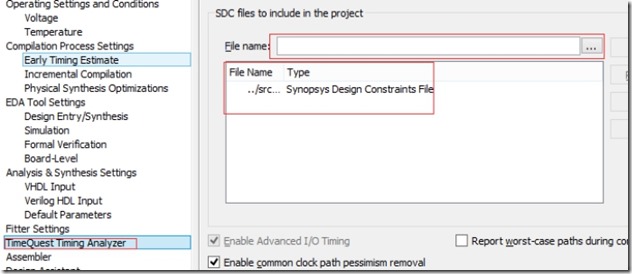

建立完约束之后,开始读取SDC文件,关于读取SDC有两种方法,(1)可以在setting中进行设置,如下图所示。

(2)也可以在timequest中进行文件的读取,在timequest界面下点击constraints----read sdc file 即可,如下图所示。

2.4 更新网表别列出时序图

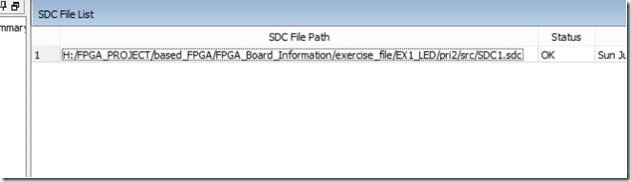

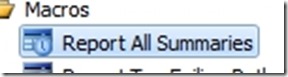

更新网表文件。然后 双击,就可以看到我们的约束内容

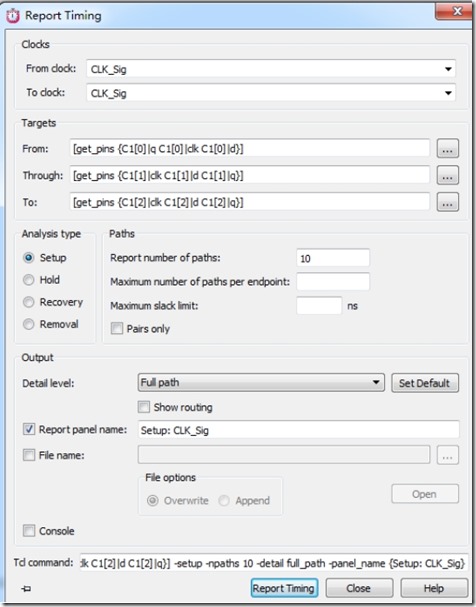

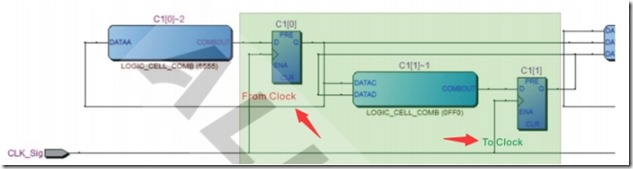

双击,就可以看到我们的约束内容 在此信号上,点击右键,就可以report timing,图16.6是报告时序的界面,第一个从源时钟到目的时钟,这个见图16.7,都会把与之相关联的寄存器节点牵扯进来。

在此信号上,点击右键,就可以report timing,图16.6是报告时序的界面,第一个从源时钟到目的时钟,这个见图16.7,都会把与之相关联的寄存器节点牵扯进来。

图16.6 操作界面

对于上图中的from clock和 to clock ,只要给定一个参数即可,就会把与之时钟相关连的牵扯进来。

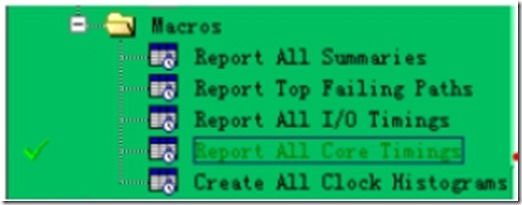

同时也需要注意,这里的路径数目,如果节点数比较多,那么需要改动这里的路径数目,去分析各路径数目之间的关系。或者也可以双击下图所示的命令,

同时也需要注意,这里的路径数目,如果节点数比较多,那么需要改动这里的路径数目,去分析各路径数目之间的关系。或者也可以双击下图所示的命令,

不过此方法只能实现1000个路径的分析,如果想要更改,还需手动去更改TCL脚本文件,

将1000改成比较大的数,以便完成更多的路径分析。

图 16.7 寄存器相关节点图

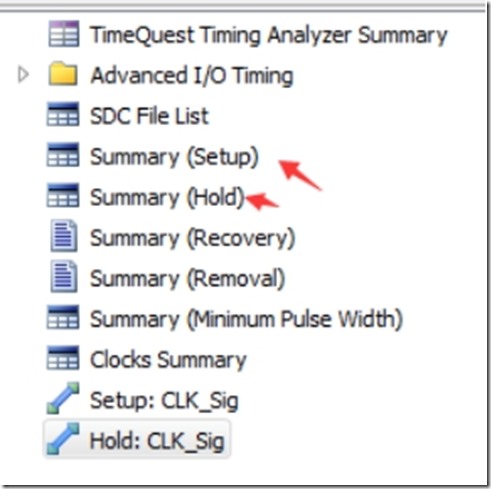

在这里可以去查看建立和保持余量是否符合要求,如下图16.8所示。

图16.8 余量查看

那么timequest的目的是告诉硬件,让你对某个信号加以约束,对于给定的不同的网表形式,所给的余量也是不同的,最坏情况比给最好情况给定的余量较多。Fmax,最高频率,此频率大小是评估走线最长情况的时钟,也是延迟最大的走线,所能够达到的最大频率,一般希望Fmax越大越好。

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

FPGA中的时序分析(二)的更多相关文章

- FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获.笔者 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- FPGA中的时序分析(五)

时序约束实例详解 本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例.本实例以VGA实验为基础,介绍如何去做时序约束. 首先VGA这种情况属 ...

- FPGA中的时序分析(三)

验证公式正确性 前两篇博客提及了关于时序的建立余量和保持余量的计算.结合实际情况,验证公式的运算正确性.结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格. 建立余量 图1是最大时钟 ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- FPGA学习笔记(二)——FPGA学习路线及开发流程

###### [该随笔部分内容转载自小梅哥] ######### 一.FPGA学习路线 工具使用 -> 语法学习 -> 逻辑设计 -> IP使用 ->接口设计 -& ...

- FPGA中RAM使用探索

FPGA中RAM的使用探索.以4bitX4为例,数据位宽为4为,深度为4. 第一种方式,直接调用4bitX4的RAM.编写控制逻辑对齐进行读写. quartus ii 下的编译,资源消耗情况. 85C ...

- FPGA中计数器设计探索

FPGA中计数器设计探索,以计数器为32位为例: 第一种方式,直接定义32位计数器. reg [31:0]count; quartus ii 下的编译,资源消耗情况. 85C模型下的时钟频率. 0C模 ...

随机推荐

- tips:解决bootstrap-switch 在jqgrid中动态加载不显示的问题

bootstrapo-switch 是一个十分好用的插件,用来关闭开启再好不过了,适合状态类型只有两种的情况下可以进行切换 在使用中,在jqgrid动态加载的时候出现不能加载的问题 原因是html代码 ...

- numpy数组-标准化数据

标准化数据的公式: (数据值 - 平均数) / 标准差 import numpy as np employment = np.array([ 55.70000076, 51.40000153, 50. ...

- (原创)c++11改进我们的模式之改进命令模式

模式虽然精妙,却难完美,比如观察者模式中观察者生命周期的问题:比如访问者模式中循环依赖的问题等等:其它很多模式也存在这样那样的一些不足之处,如使用场景受限.实现复杂.不够简洁.不够通用等.但我觉得不足 ...

- C++11 构造函数的改动

一.继承构造函数 继承构造函数的引入原因:如果基类的构造函数很多,那么子类的构造函数想要实现同样多的构造接口,必须一一调用基类的构造函数,有点麻烦. 于是乎:C++11引入继承构造函数,子类可以通过使 ...

- MyBean-关于plugMap共享对象

plugMap实现了对象的存储,使用setObject,和getObject来对对象进行存储 内部其实是一个列表,而且他会在释放的时候会情况尝试释放所有的对象,所以如果你共享的对象提前进行了释放, ...

- ExecutorService-10个要诀和技巧【转】

http://ifeve.com/executorservice-10-tips-and-tricks/

- 【delphi】delphi操作sqlite3

SQLite SQLite是一个老牌的轻量级别的本地文件数据库,完全免费且开源,不需要安装,无须任何配置,当然,这样管理功能就不是很强大了,但是它的主要应用也是在本地数据库,可以说是最简单好用的嵌入式 ...

- shell快捷方式总结

Linux使用Shell时总是有各种不太方便,需要对输入的命令行做编辑.跳转.这里整理下我遇到的Shell下快捷键. 注意下文中所有的ctrl表示键盘中的控制按键,所有的ctrl + x的格式都是同时 ...

- visual c++中预定义的宏

一.主要目标 (由于visual studio通常包含很多开发环境,通常将其中c/c++的ide称为visual c++ 20xx) 整理下visual c++ 2010下预定义的宏.做一下备忘和了解 ...

- html5 class

指向样式表中的类比如<span class="left_menu important">...</span>表示这个span的样式,由样式表中的left_m ...