奇分频电路如何实现? 负沿触发&非负沿触发

请设计一个奇分频电路,占空比为50%?

以下给出解答:

1、带负沿触发

module div //带负沿触发

#(parameter N = 5) //定义分频参数

(

input sys_clk ,

input sys_rst_n ,

output div_clk

); // 核心:在上下边沿的计数器 计数至 N/2 翻转 计数至 N-1 再翻转

// 上下边沿脉冲信号 或运算 即可得到最终的 奇分频结果 占空比50%

reg clk_pose ; //上升沿

reg clk_nege ; //下降沿

reg [N:0] cnt_pose ; //上升沿计数

reg [N:0] cnt_nege ; //下降沿计数 always@(posedge sys_clk or negedge sys_rst_n) begin //在上升沿计数

if(!sys_rst_n)

cnt_pose<='d0;

else if(cnt_pose==N-1)

cnt_pose<='d0;

else

cnt_pose<=cnt_pose+'d1;

end

always@(negedge sys_clk or negedge sys_rst_n) begin //在下升沿计数

if(!sys_rst_n)

cnt_nege<=1'b0;

else if(cnt_nege==N-1)

cnt_nege<='d0;

else

cnt_nege<=cnt_nege+'d1;

end always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_pose<=1'b0;

else if(cnt_pose==N/2)

clk_pose<=~clk_pose;

else if(cnt_pose==N-1)

clk_pose<=~clk_pose;

else

clk_pose<=clk_pose;

end

always@(negedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_nege<=1'b0;

else if(cnt_nege==N/2)

clk_nege<=~clk_nege;

else if(cnt_nege==N-1)

clk_nege<=~clk_nege;

else

clk_nege<=clk_nege;

end assign div_clk= clk_nege |clk_pose ; //上升沿 和下降沿 或运算 得到 奇分频 endmodule

`timescale 1ns/1ns

module tb_div();

reg sys_clk ;

reg sys_rst_n ;

wire div_clk ; initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end always #10 sys_clk<=~sys_clk; div #(.N()) //可自己定义想要的分频参数

div_inst(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.div_clk (div_clk)

); endmodule

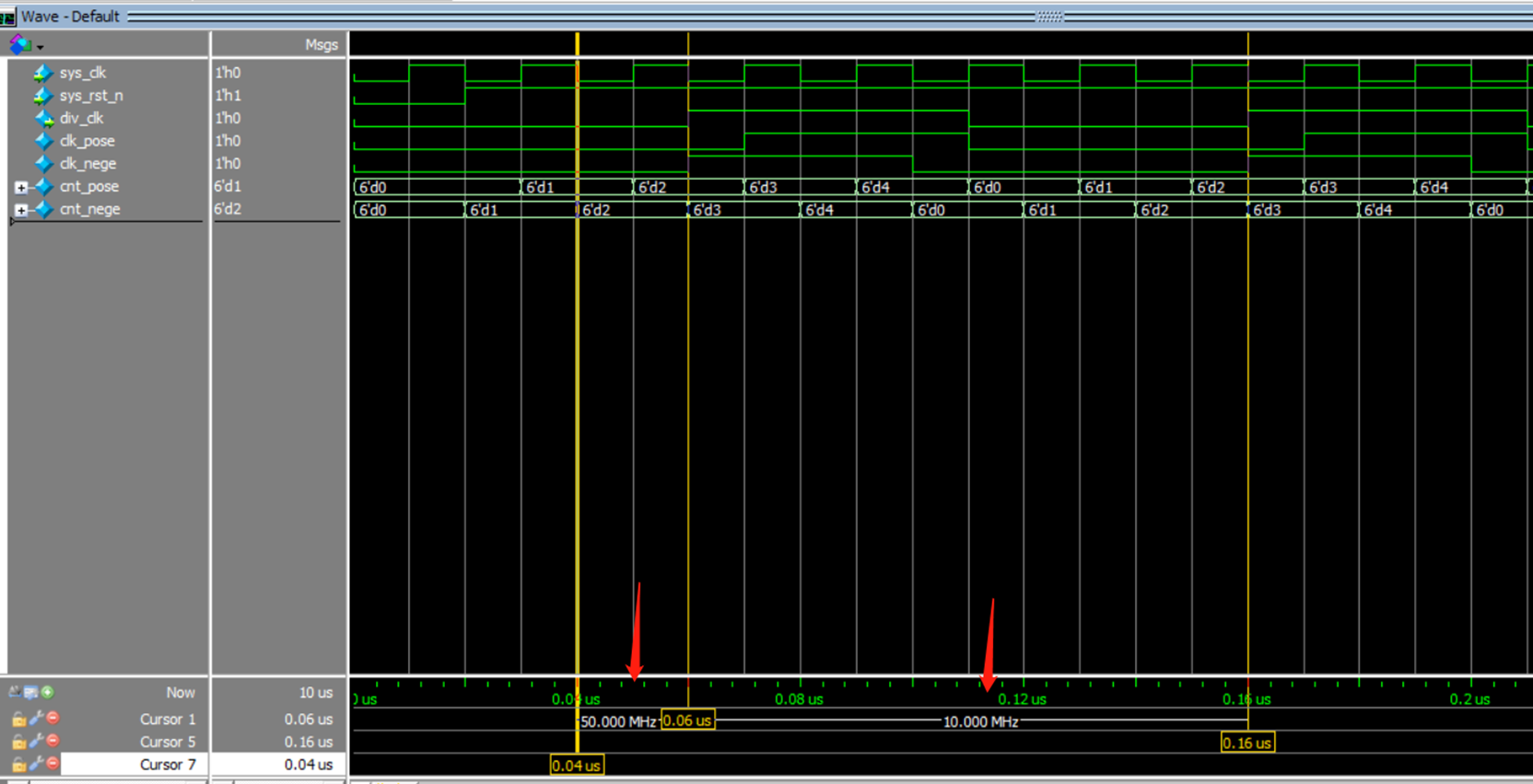

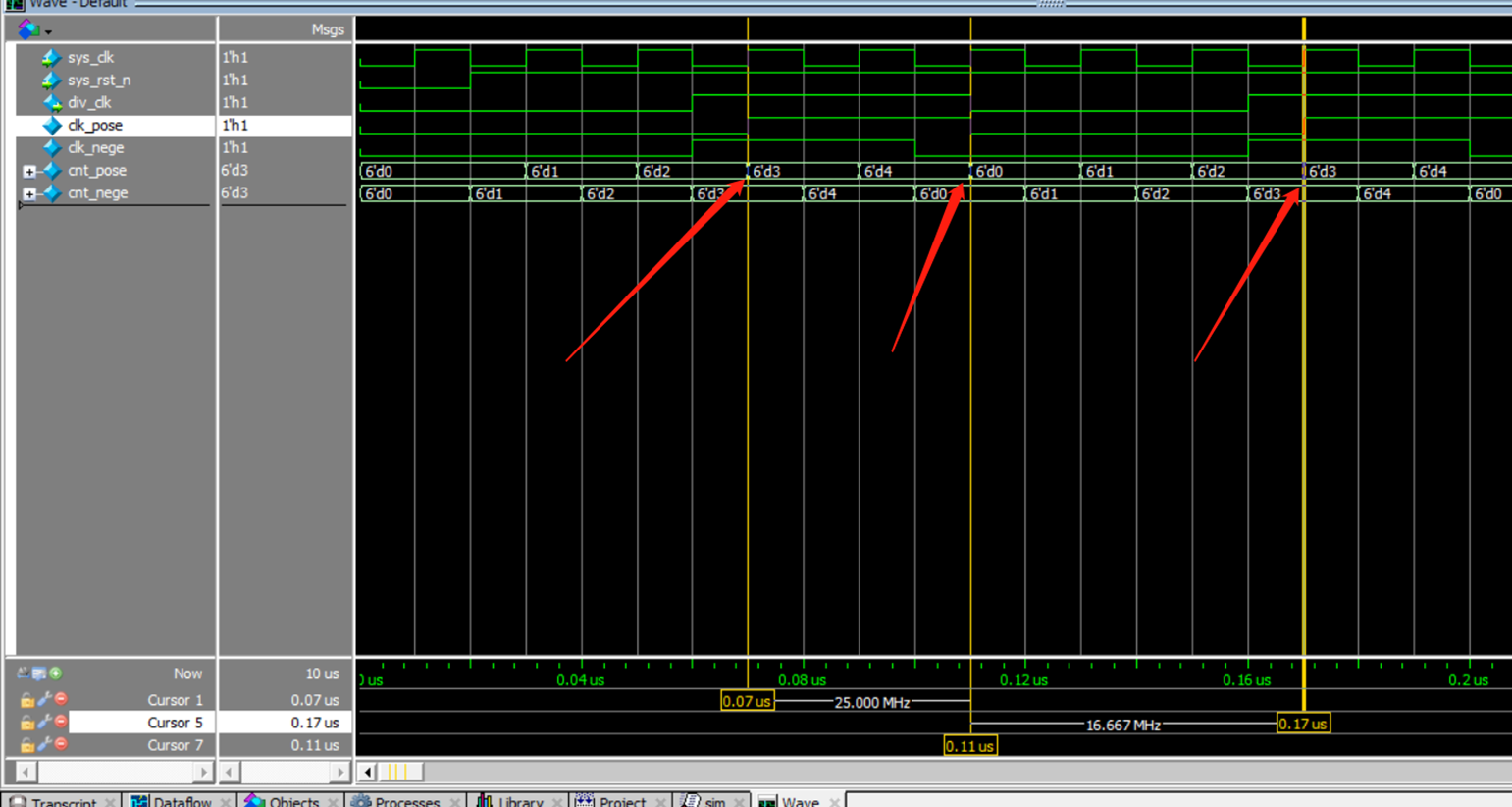

波形图如下

2、不带负沿触发

module div //不带负边沿触发

#(parameter N = 5) //定义分频参数

(

input sys_clk ,

input sys_rst_n ,

output div_clk

); // 核心:构造一个与时钟相反的新时钟 在原时钟域下 在前N/2 时钟周期保持0 后面 N/2+1 ~N-1 翻转

// 在新时钟域下 在原时钟域下 在前N/2 时钟周期保持0 后面 N/2+1 ~N-1 翻转

//在新时钟域下 对分频寄存器打拍一拍

//对两个时钟域下的分频时钟寄存器想或 得到 奇分频结果 占空比50%

reg clk_0 ; //原时钟域

reg clk_1 ; //新时钟域下

reg clk_2 ; //新时钟域下

reg [N:0] cnt ; //原时钟域上升沿计数

wire sys_clk_0 ; //构造的新时钟域 assign sys_clk_0=~sys_clk ; always@(posedge sys_clk or negedge sys_rst_n) begin //在上升沿计数

if(!sys_rst_n)

cnt<='d0;

else if(cnt==N-1)

cnt<='d0;

else

cnt<=cnt+'d1;

end always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_0<=1'b0;

else if(cnt<=N/2)

clk_0<=1'b0;

else

clk_0<=1'b1;

end always@(posedge sys_clk_0 or negedge sys_rst_n) begin

if(!sys_rst_n) begin

clk_1<=1'b0;

clk_2<=1'b0;

end

else if(cnt<=N/2) begin

clk_1<=1'b0;

clk_2<=clk_1;

end

else begin

clk_1<=1'b1;

clk_2<=clk_1;

end

end assign div_clk= clk_0 |clk_2 ; //对两个时钟域下的分频时钟寄存器想或 得到 奇分频结果占空比50% endmodule

`timescale 1ns/1ns

module tb_div();

reg sys_clk ;

reg sys_rst_n ;

wire div_clk ; initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end always #10 sys_clk<=~sys_clk; div #(.N()) //可自己定义想要的分频参数

div_inst(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.div_clk (div_clk)

); endmodule

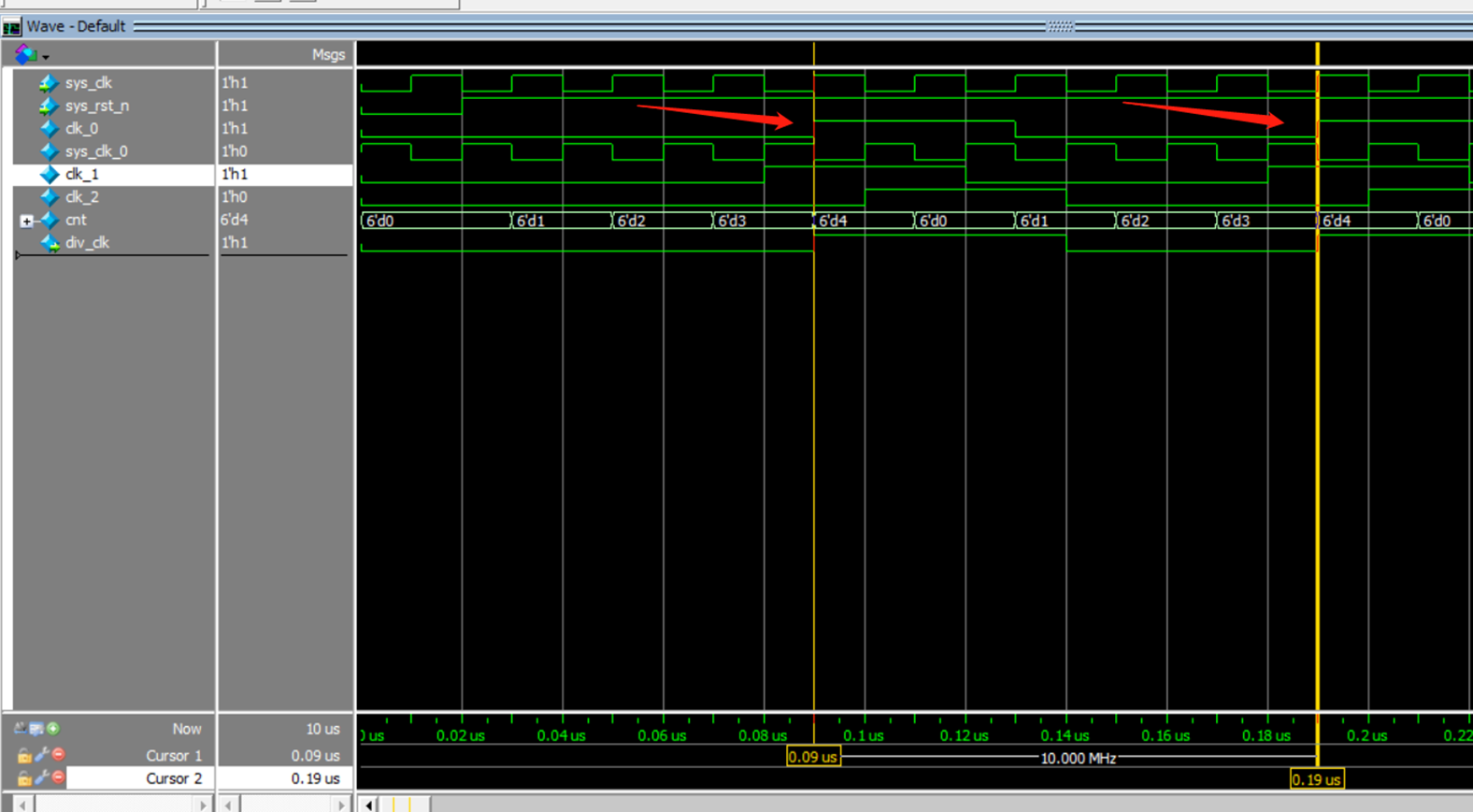

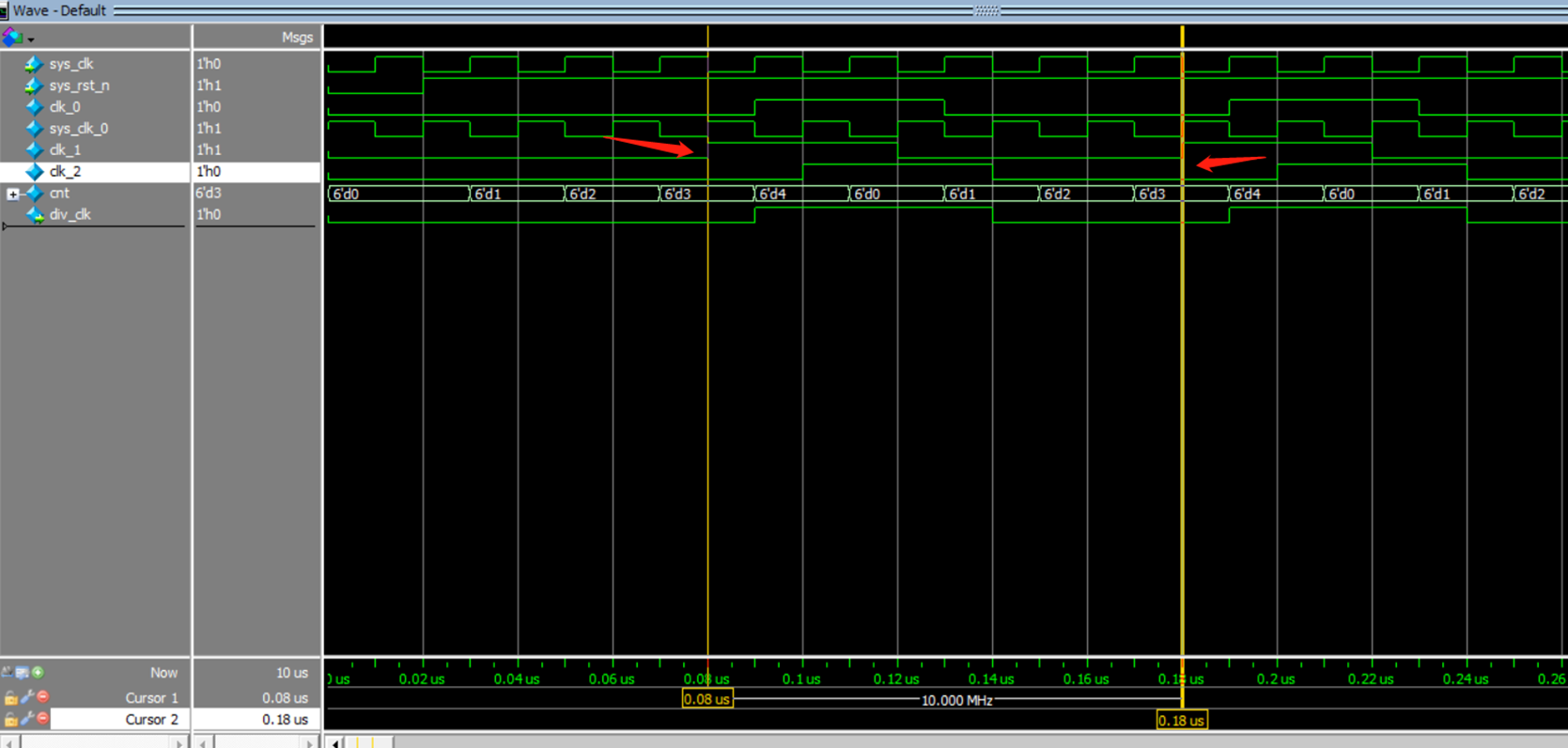

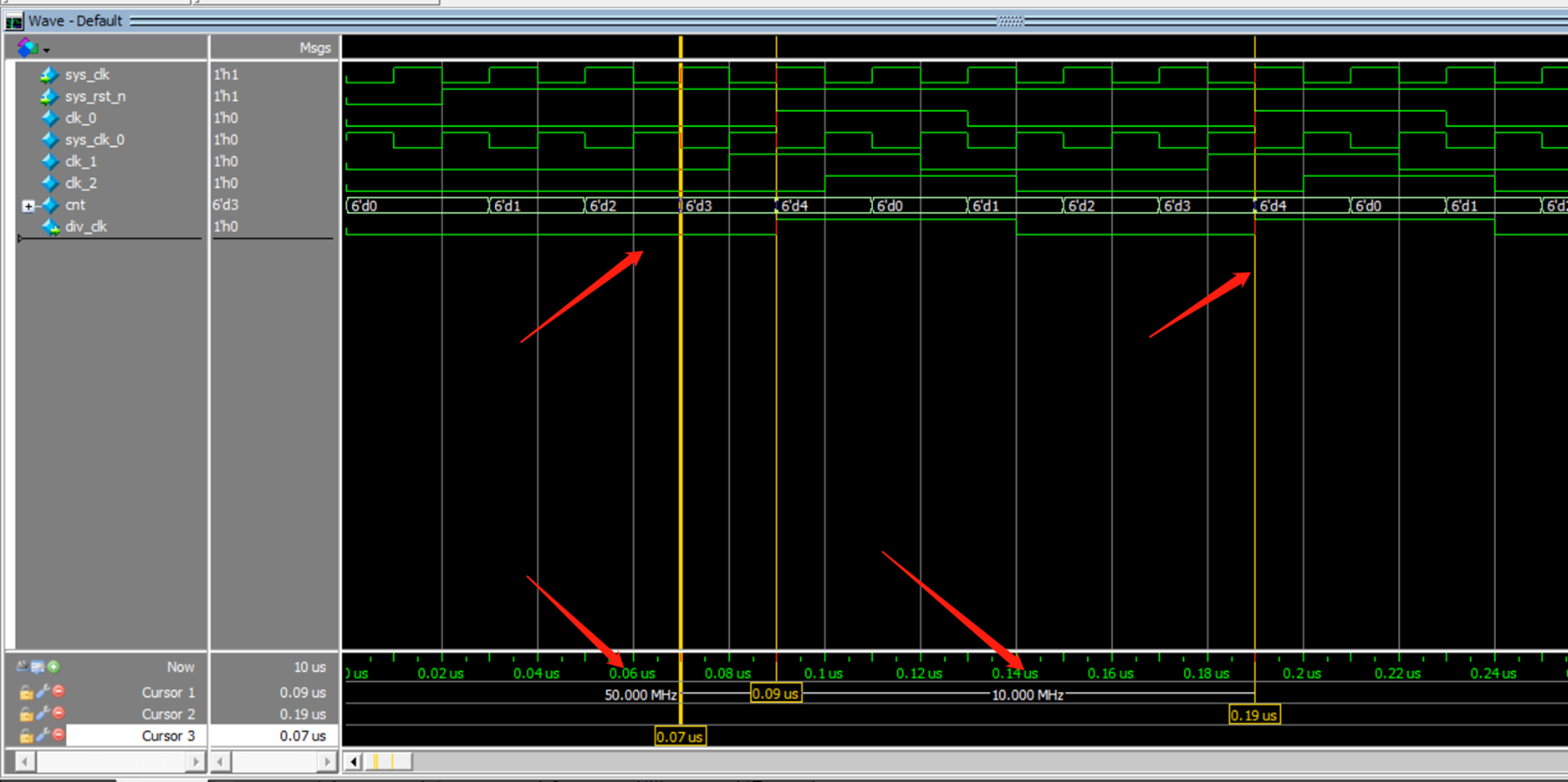

波形图如下:

以上是本人对奇分频电路的总结,若有不对的地方,敬请指正,万分感谢。

参考资料:

1、奇数分频--不使用负边沿触发verilog实现(占空比50%) - 影-fish - 博客园 (cnblogs.com)

奇分频电路如何实现? 负沿触发&非负沿触发的更多相关文章

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- 背水一战 Windows 10 (24) - MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令

[源码下载] 背水一战 Windows 10 (24) - MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令 作者:webabcd ...

- 实例浅析epoll的水平触发和边缘触发,以及边缘触发为什么要使用非阻塞IO

一.基本概念 我们通俗一点讲: Level_triggered(水平触发):当被监控的 ...

- MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令

介绍背水一战 Windows 10 之 MVVM(Model-View-ViewModel) 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令 ...

- epoll的水平触发和边缘触发,以及边缘触发为什么要使用非阻塞IO

转自:http://www.cnblogs.com/yuuyuu/p/5103744.html 一.基本概念 ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- 条件触发和边缘触发 及 epoll 的长处

条件触发: 仅仅要输入缓冲有数据就会一直通知该事件 边缘触发: 输入缓冲收到数据时仅注冊1次该事件.即使输入缓冲中还留有数据,也不会再进行注冊 水平触发(level-triggered.也被称为条件触 ...

- jenkins 判断是手动触发还是定时器触发

根据变量BUILD_CAUSE的值可以判断本次触发是手动触发还是定时器触发 手动触发:MANUALTRIGGER 定时器触发:TIMERTRIGGER

- epoll的边缘触发与水平触发

epoll的边缘触发与水平触发 Tcp连接是双向的,内核为每个socket维护两个缓冲区,读缓冲区与写缓冲区,内核会一个关注这两个缓冲区,当采用水平触发时,对于写缓冲区而言,如果有多余空间可写,对于读 ...

- 如何用代码而非事件触发PBO

通常我们通过抛出事件触发PBO,但若没有事件发生时,我们其实也可以用代码强制发出命令. 写法如下: CL_GUI_CFW=>SET_NEW_OK_CODE( NEW_CODE = <uco ...

随机推荐

- DVWA文件上传

Low安全级别: <?php @eval($_POST['cmd']);?> 文本编辑器写入一句话木马,保存并改为php文件. 上传 成功上传,并返回路径 打开菜刀客户端连接 成功连接 反 ...

- vue中让嵌入的iframe完美自适应宽度、高度

涉及到系统集成的时候,前端我们经常会用到iframe嵌入,但是嵌入的时候经常有不适应的情况,太长或太宽.滚动条... 下面的方法可以做到使嵌入的iframe自适应宽度.高度, 1.嵌入iframe,加 ...

- react之todoList基础小项目

1.项目最终成品和项目目录快照如图: 2.context.js文件 // 使用context进行多级传递数据 // 1. createContext 创建一个可以多级传递的context数据 // 2 ...

- 2023-01-10:智能机器人要坐专用电梯把货物送到指定地点, 整栋楼只有一部电梯,并且由于容量限制智能机器人只能放下一件货物, 给定K个货物,每个货物都有所在楼层(from)和目的楼层(to),

2023-01-10:智能机器人要坐专用电梯把货物送到指定地点, 整栋楼只有一部电梯,并且由于容量限制智能机器人只能放下一件货物, 给定K个货物,每个货物都有所在楼层(from)和目的楼层(to), ...

- 2021-04-19:手写代码:最小生成树算法之Kruskal。

2021-04-19:手写代码:最小生成树算法之Kruskal. 福大大 答案2021-04-19: 并查集.边从小到大,找最小边,无环. 代码用golang编写.代码如下: package main ...

- hasattr()、getattr()、setattr()函数简介

hasattr(object, name) 判断object对象中是否存在name属性,当然对于python的对象而言,属性包含变量和方法:有则返回True,没有则返回False:需要注意的是name ...

- 【GiraKoo】安装Visual Assist失败,提示“此扩展已经安装到所有适用的产品”

[问题解决]安装Visual Assist失败,提示"此扩展已经安装到所有适用的产品" 在安装Visual Assist插件时,提示错误. 点击下一步之后,进入插件安装界面.插件安 ...

- 数据库SQL复习

数据库SQL介绍 Def:SQL是一种极其高效的数据库系统语言:可以实现对数据库中的数据进行增删改查等操作 增加操作:使用create命令: 可以create table 可以create View ...

- 尤雨溪创立 Vue.js 的心路历程纪录片

Show More 本文分享自微信公众号 - 生信科技爱好者(bioitee).如有侵权,请联系 support@oschina.cn 删除.本文参与"OSC源创计划",欢迎正在阅 ...

- 【python基础】循环语句-break关键字

1.break关键字 break关键字,其作用是在循环中的代码块遇到此关键字,立刻跳出整个循环,执行循环外的下一条语句. 其在while和for循环中的作用示意图如下: 1.1break在while循 ...