Verilog手绘FVH信号

Verilog手绘FVH信号

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/09/17 13:20:06

// Design Name:

// Module Name: ntsc_fvh

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module ntsc_fvh( input wire clk, //27MHz

input wire rst,

input wire enable, output wire hsout,

output wire vsout,

output wire oeout ); parameter THSOUT = ; //2.4us

parameter H_TOTAL = ; //64us

parameter V_TOTAL = ; wire hsout_falling; //------------------------------------------------- reg [:]hsout_cnt = ;

always @(posedge clk or posedge rst)

begin

if(rst)

hsout_cnt <= ; else if(enable)

begin

if(hsout_cnt == H_TOTAL)

hsout_cnt <= ;

else

hsout_cnt <= hsout_cnt + 'b1;

end else

hsout_cnt <= ; end //------------------------------------------------- reg hsout_reg = 'b1 ;

always @(posedge clk or posedge rst)

begin

if(rst)

hsout_reg <= 'b1; else if(enable)

begin

if(hsout_cnt <= THSOUT - || hsout_cnt == H_TOTAL)

hsout_reg <= 'b0;

else if(hsout_cnt >= THSOUT && hsout_cnt <= H_TOTAL - )

hsout_reg <= 'b1;

end else

hsout_reg <= 'b1;

end //------------------------------------------------- reg hsout_reg_delay = 'b1;

always @(posedge clk or posedge rst)

begin

if(rst)

hsout_reg_delay <= 'b1; else if(enable)

hsout_reg_delay <= hsout_reg; else

hsout_reg_delay <= 'b1; end //------------------------------------------------- reg [:] hsout_falling_cnt = ;

always @(posedge clk or posedge rst)

begin

if(rst)

hsout_falling_cnt <= ; else if(enable)

begin if(hsout_falling_cnt == V_TOTAL)

begin

hsout_falling_cnt <= V_TOTAL;

if(hsout_falling)

hsout_falling_cnt <= ;

end else if(hsout_falling)

hsout_falling_cnt <= hsout_falling_cnt + 'b1;

end else

hsout_falling_cnt <= 'b0; end //------------------------------------------------- reg vsout_reg = 'b1;

reg oeout_reg = 'b0;

always @(posedge clk or posedge rst)

begin

if(rst)

begin

vsout_reg <= 'b1;

oeout_reg <= 'b0;

end else if(enable)

begin if(hsout_falling_cnt < || (hsout_falling_cnt == && hsout_cnt < && hsout_cnt >))

begin

vsout_reg <= 'b1;

oeout_reg <= 'b0;

end else if(hsout_falling_cnt == && hsout_cnt == )

begin

vsout_reg <= 'b0;

oeout_reg <= 'b1;

end else if(hsout_falling_cnt == && hsout_cnt == )

vsout_reg <= 'b1; else if(hsout_falling_cnt == && hsout_cnt == )

begin

vsout_reg <= 'b0;

oeout_reg <= 'b0;

end else if(hsout_falling_cnt == && hsout_cnt == )

vsout_reg <= 'b1; else

begin

vsout_reg <= vsout_reg;

oeout_reg <= oeout_reg;

end

end

end //------------------------------------------------- assign hsout_falling = hsout_reg_delay && (!hsout_reg);

assign hsout = hsout_reg;

assign vsout = vsout_reg;

assign oeout = oeout_reg; endmodule /* add_force {/ntsc_fvh/clk} -radix hex {1 0ns} {0 25000ps} -repeat_every 50000ps

add_force {/ntsc_fvh/rst} -radix hex {1 0ns} {0 100ns}

add_force {/ntsc_fvh/enable} -radix hex {1 0ns} */

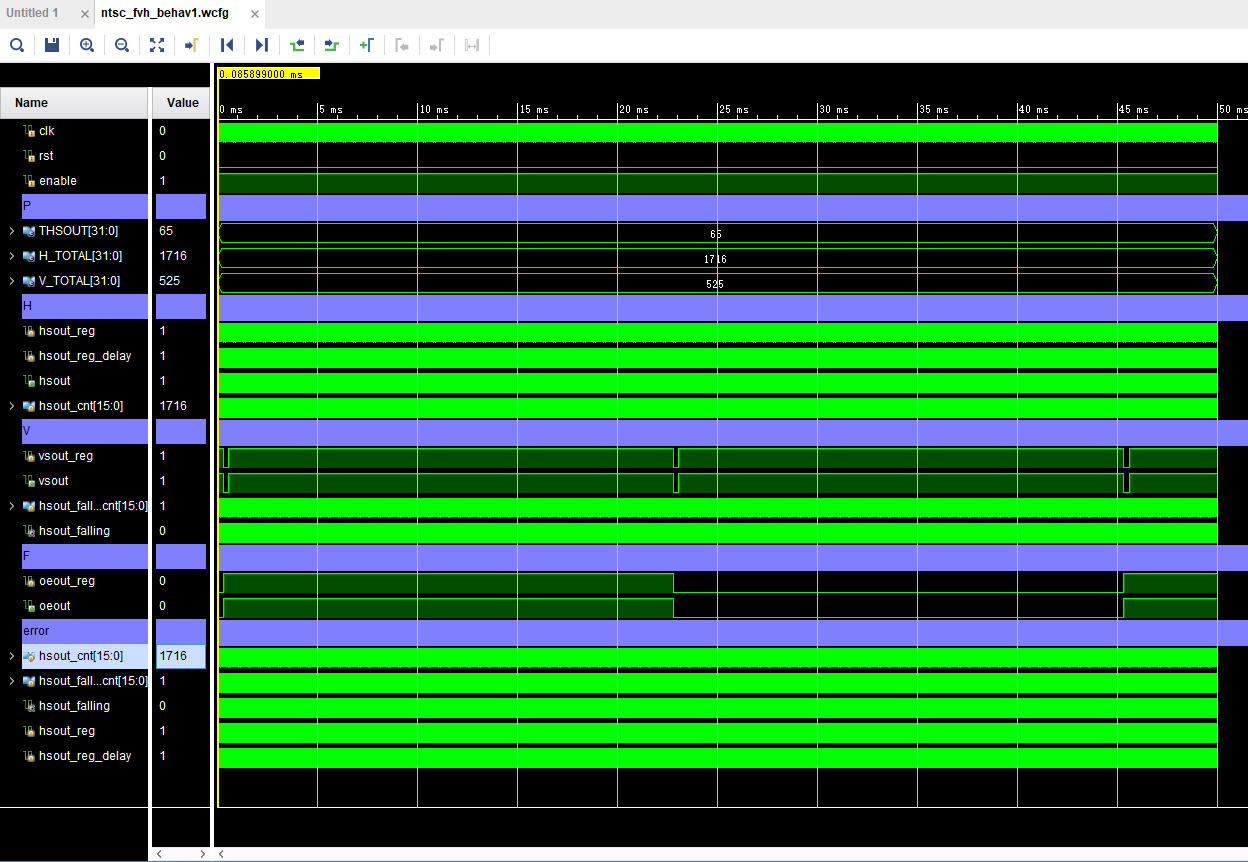

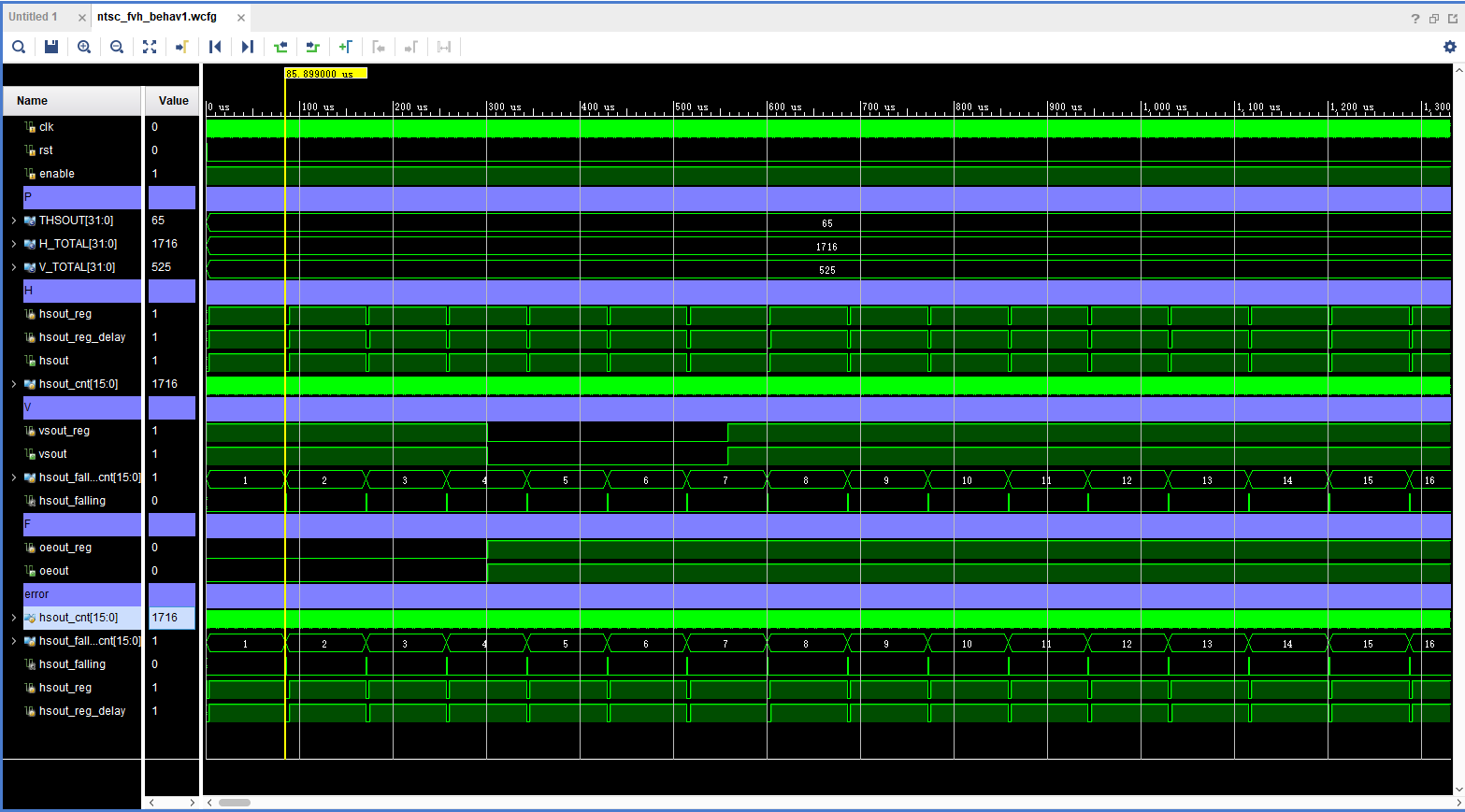

仿真结果:

Verilog手绘FVH信号的更多相关文章

- JointBoost+CRF+GraphCut做手绘草图的分割

研究生做的稍微有点水平的就这两个项目了:一个是利用SVM做手绘草图的分类,另一个是利用JointBoost+CRF做手绘草图的分割.总结得出的经验是做研究的方法就是将别人大神的代码看懂然后改成适合自己 ...

- Android基于mAppWidget实现手绘地图(一)--简介

http://lemberg.github.io/mappwidget/user_guide.html 最近在看一些导游类应用,发现一些景区的导览图使用的完全是自定义地图,也就是手绘地图.这种小范围使 ...

- EDIUS手绘遮罩功能如何用

学了这么久的EDIUS视频编辑软件,你们学的怎么样了呢?你们知道EIDUS手绘遮罩的用法么,会熟练地使用它么?如果你们还没有学到这一知识点的话也不要着急,因为你们看完下面这篇文章就会明白了.事不宜迟, ...

- 免费下载:320+ 手绘风格 Apple iOS7 图标

Themify 图标是一套用在网页设计和应用程序的图标,包括 320+ 手工制作的像素完美的苹果 iOS7 图标中汲取灵感.这些图标完全免费,您可以用于任何目的,无论是个人或商业. 您可能感兴趣的相 ...

- IOS 手绘地图导航

手绘地图导航 第三方库 NAMapKit, 1)支持在手绘图上标记.缩放 2)支持在单张图片 3)支持瓦片小图片 思路 前提:美工已经切好手绘图,并告知我们当前的缩放级别. 1)确定好手绘图左上角点在 ...

- 基于mAppWidget实现手绘地图(十五)–如何控制放大缩小

一般来说,可以使用以下几种方式来控制地图的放大/缩小 : 使用控件底部的缩放按钮 双击控件 pinch手势 物理按键 :I键标识缩小 :O键表示放大.(只有设备具有物理按键才行) 当然, ...

- 基于mAppWidget实现手绘地图--索引&DEMO

文章翻译完了,梳理一下,附Demo下载 基于mAppWidget实现手绘地图(一)–简介 基于mAppWidget实现手绘地图(二)–概要 基于mAppWidget实现手绘地图(三)–环境搭建 基于m ...

- UWP 手绘视频创作工具 “来画Pro” 技术分享系列

开篇先来说一下我和来画的故事,以及写这篇文章的初衷. 今年年初时,我还在北京,在 Face++,做着人脸识别技术的 Windows 和 Android 端,做着人工智能终将实现世间所有美好的梦.这时的 ...

- UWP 手绘视频创作工具技术分享系列

开篇先来说一下写这篇文章的初衷. 初到来画,通读了来画 UWP App 的代码,发现里面确实有很多比较高深的技术点,同时也是有很多问题的,扩展性,耦合,性能,功能等等.于是我们决定从头重构这个产品,做 ...

随机推荐

- spyder常用功能

最近和同学讨论到spyder的使用技巧,所以就结合之前在网上看到网友的总结( https://blog.csdn.net/peiwang245/article/details/78528098)和自己 ...

- git bash + gitee

使用Git Bash从Gitee上下载代码到本地以及上传代码到码云Git: https://www.cnblogs.com/babysbreath/p/7274195.html 指定克隆远端分支 ht ...

- hive防止数据被误删除

1.HDFS层面开启trash功能(fs.trash.interval) 被删除的数据在HDFS中的/user/$USER/.Trash目录中,开启这个功能秩序要将配置属性fs.trash.inter ...

- ElementUI - Table 表头排序

ElementUI - Table 表头自带排序功能,和排序事件,但是目前只是对当前界面的数据进行排序. 项目需求: 点击表头排序的时候,对所有数据进行排序. 初步方案: 在点击排序按钮的时,在排序事 ...

- 团队合作one

一.项目介绍 为生活在长大的学生提供方快捷的生活服务,通过帖子发现自己志同道合的朋友,记录自己在长大点滴.本项目的意义在于锻炼团队的scrum能力,加强团队合作能力.确定本项目采用的技术方向:本项目整 ...

- phpstorm快捷键总结

如果映射的是eclipse的快捷键,又同时安装了英特尔的GPU软件,那么会有这个快捷键冲突 就是快速复制快捷键:ctrl+alt+方向键 会调用英特尔旋转屏幕,禁用掉即可 PhPStorm 是 Je ...

- win11.2.0.4lsnrctl status hang

以前听客户说监听日志大于4G,监听出现问题.本次另一个客户也出现这个问题,表现为监听lsnrctl start,status长久hang住 匹配mos WINDOWS: Listener Hangs ...

- Zedboard搭建Linux嵌入式环境

ZYNQ是ARM硬核和PL软核的结合体,Xillybus官方为他开发了驱动套件Xillinux,赶快将开发板投入使用吧! 本随笔参考了众多博主和官方教程:(基本上就是把官方教程翻译了一遍,呵呵:)) ...

- C#经典面试题及答案

1.请你说说.net 中类和结构的区别? 答:结构和类具有大体的语法,但是结构受到的限制比类多.结构不能声明默认的的构造函数,为结构的副本是编译器创建和销毁的,所以不需要默认的构造函数和析构函数,结构 ...

- POJ - 1830:开关问题 (开关问题-高斯消元-自由元)

pro:有N个相同的开关,每个开关都与某些开关有着联系,每当你打开或者关闭某个开关的时候,其他的与此开关相关联的开关也会相应地发生变化,即这些相联系的开关的状态如果原来为开就变为关,如果为关就变为开. ...