【心得】Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)

背景

下边的内容,适合初次使用Lattice的、具备FPGA开发经验的同学。

1、初次使用,还真遇到不少的坑,Lattice的工具也有不少优缺点,通过总结,希望能缩短熟悉的时间。

2、具体问题,欢迎留言交流。

DDR3 IP例化

LEF5UM器件,应用DDR3控制器IP。主要分几步:IP获取,安装,例化。

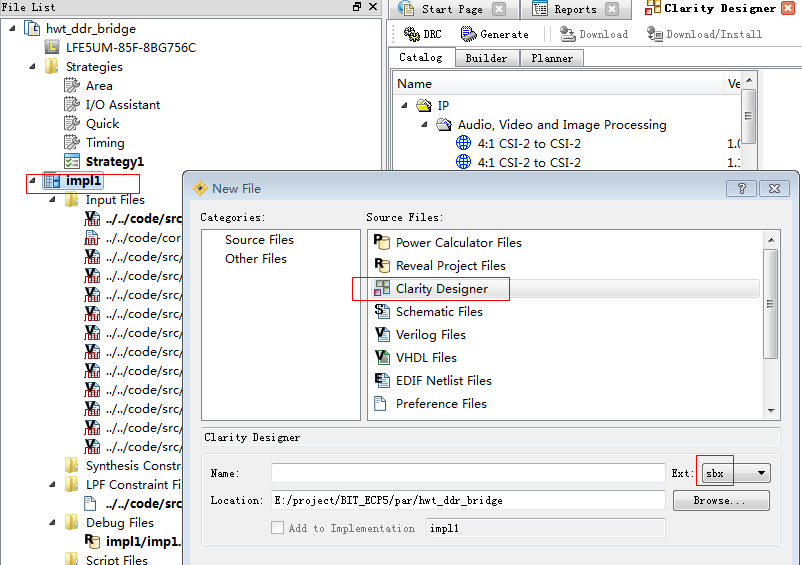

1、先在impl1目录下,右键,新建sbx文件,即Clarity Designer,通过该文件,进行IP的例化管理。

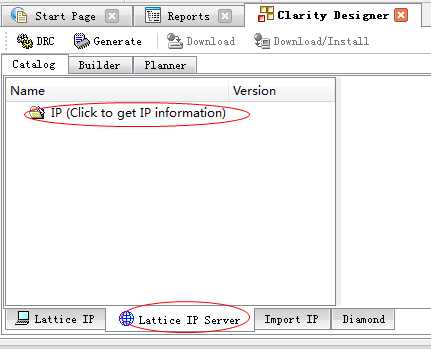

2、打开sbx,在选项卡“Lattice IP Server”里点击IP联网获取IP列表。

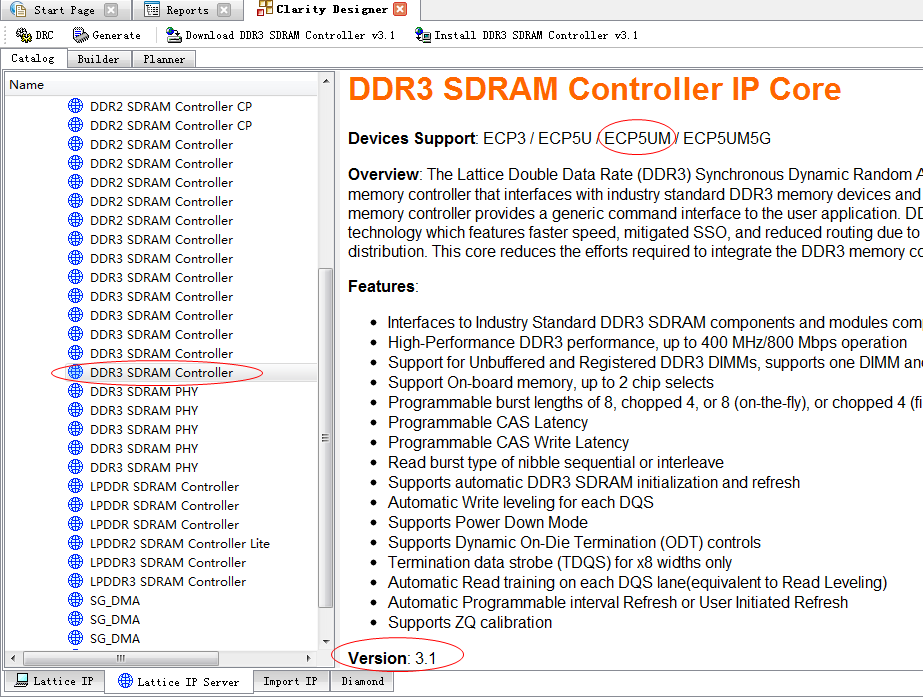

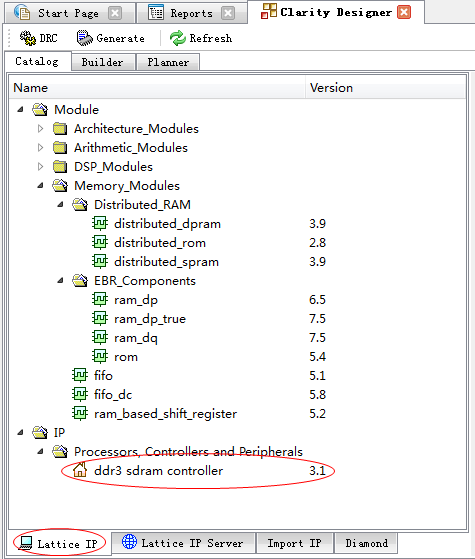

3、选择“DDR3 SDRAM Controller”,目前(18年12月)最新版本3.1,下载(格式exe)后安装到指定目录(如:C:\LatticeCore\ddr3_sdram_common_v3.1),这样可以在选项卡“Lattice IP”中看到“ddr3 sdram controller 3.1”。

4、打开ip,GUI界面如下,在本项目中,参考时钟(RefClock)来自单板晶振产生的100M,ddr的工作频率400M,双沿也就800M。Memory Type选择On-board Memroy,总线宽度16,配置x16,时钟宽度1。Data_rdy to Write Data Delay选择2,表示data_rdy有效之后必须在第2拍送数据。

注意:这里涉及时序收敛上的编码技巧。通常,用户逻辑数据先存入fifo,再送给ddr3控制器,再加上控制器要求2拍给数据,这样,fifo跟ddr3控制器之间时序就比较难收敛(如果很好收敛,那说明你在设计上已经关注到了这点),我的办法很简单,就是对fifo进行预读操作,在读使能送出之前,先预读3拍出来,等ddr发出读使能时,数据就不是从fifo到DDR3了,而是在这之间插入了几拍的寄存器,从而缓解了时序压力。

DDR3仿真

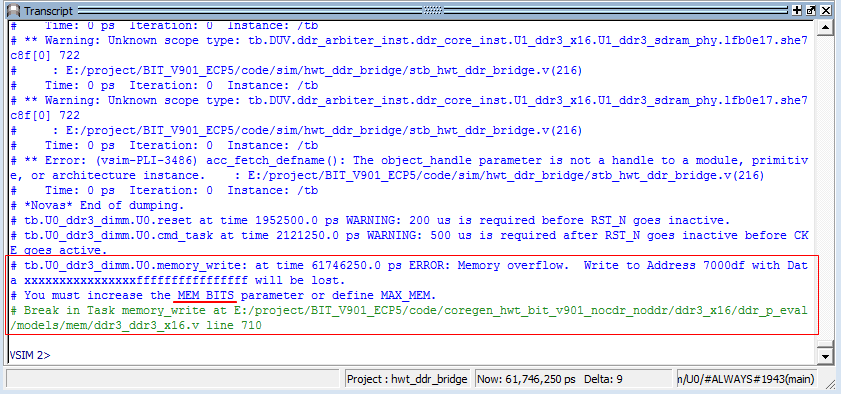

仿真脚本我会单独介绍,其实IP工程给出了仿真脚本,借用过来修改修改就可以使用。这里只提一个导致仿真只运行60多us就提前终止的小问题。

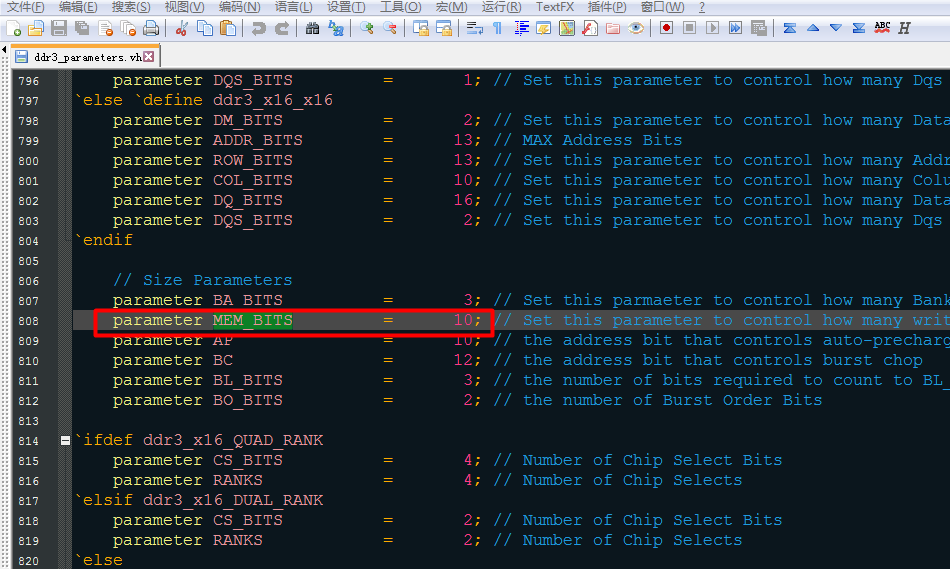

解决办法,请仔细阅读仿真工具的告警,工具明确说了,是Memory overflow,建议增加MEM_BITS参数或者定义MAX_MEM。绿色文字也给出了文件路径的指示,在ddr3_ddr3_x16.v中,include有参数文件

ddr3_parameters.vh,就是同一目录下,打开vh文件,搜索MEM_BITS,默认为10,修改为16即可。

小结:遇到问题先不慌张,认真阅读工具给出的提示信息,通常会有解决思路。有同学说英文不好咋办,那就复制粘贴到网上的翻译软件呗,不然还能凉拌?

bit/mcs烧录

Lattice工具一个不好用的地方,就是mcs烧录得讲究顺序,否则会报错。烧录mcs的步骤:

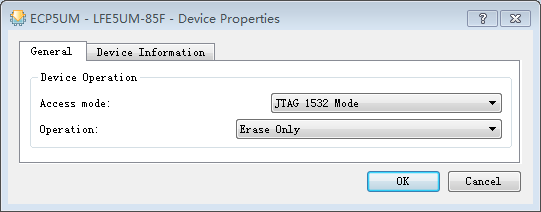

A、JTAG模式下,选择Erase Only。

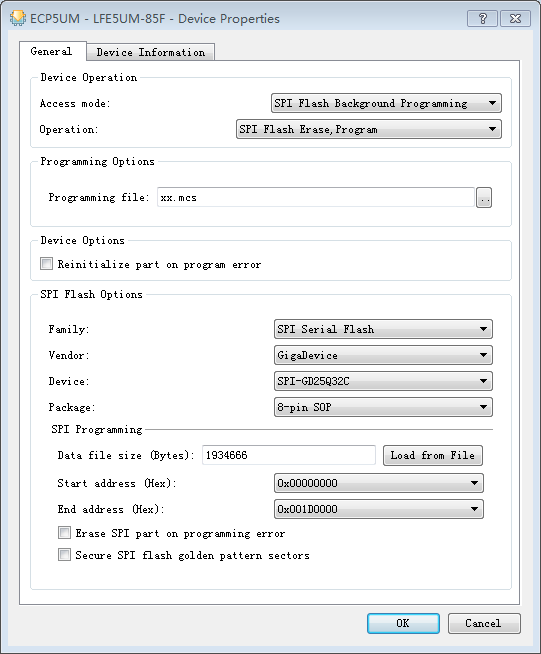

B、选择SPI Flash,操作时可以不用verify,如下。

Reveal逻辑分析仪

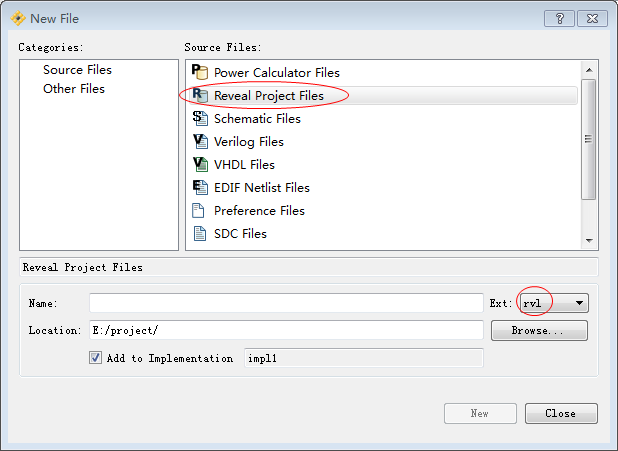

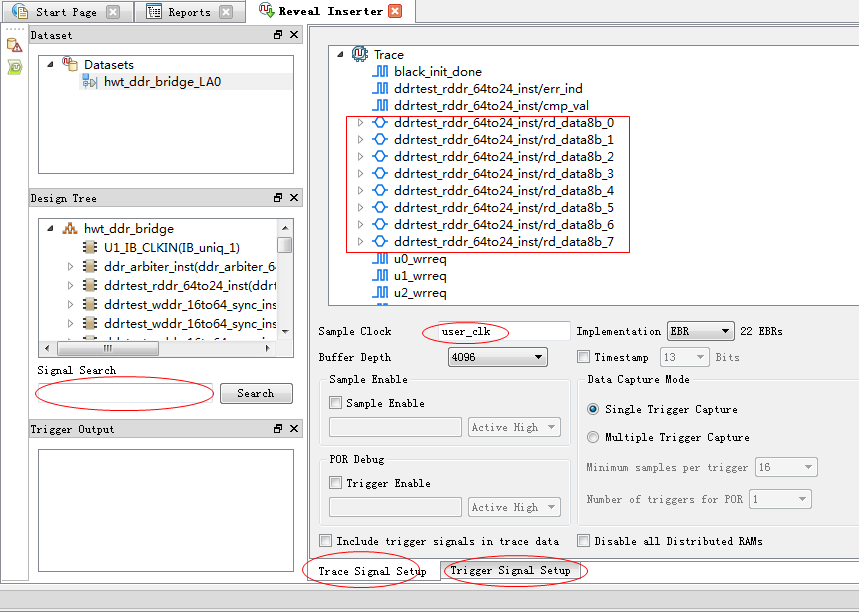

FPGA厂家都会提供内嵌逻辑分析仪,Xilinx叫chipscope,Lattice的叫reveal,可以单独安装reveal程序,也可以在diamond工程中打开。在“File List”的“Debug Files”里,右键,点击Reveal Project Files,可新建*.rvl文件,相对Xilinx,这个rvl比较好用,复制veriog代码信号名,只要没被优化,就可以很快找到。

添加信号时,除了在trace signal setup里选择时钟和观察信号之外,另外还需要在trigger signal里设置,这点比Xilinx稍微麻烦点。

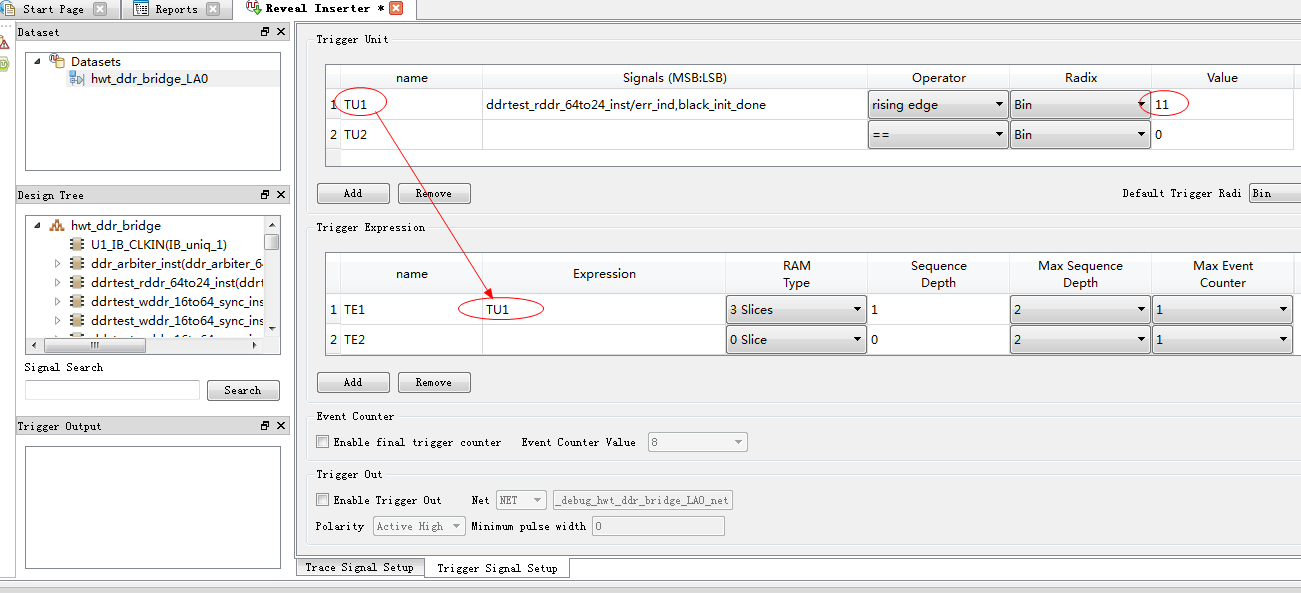

trigger设置也有套路。第一步,在trigger unit中拉入信号,可以在一个条件里,也可以分开,operator可以不用管,到时抓波形时可以修改的。第二步,在trigger exprssion里,直接把unit的name复制下来就好。

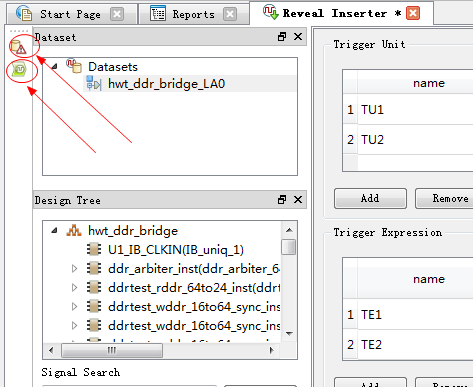

以上操作完毕,记得点击design rule check(下图靠上的图标),检查是否有错,然后点击insert debug,让逻辑分析的时钟自动添加到后端约束lpf文件里(在约束的首行)。

抓波形的其他技巧

- 若要保留抓波形的相关文件,需要复制*.bit,*.rvl和*.rvs文件,同时,对*.rvs文件内容的第一行进行修改,确保指向确定的文件。

- 出于测试目的,临时添加的信号,为防止被优化掉,可使用 reg signal_name/* synthesis syn_keep=1 */; 直接让信号保留,记住,完成综合之后,要手工点击design fresh,这样才能在rvl文件中查找到该添加的测试信号。

后端约束lpf

不正确的约束,或者遗漏的约束,会导致跑的结果不符合预期。约束时,记得下边几个方面不要遗漏。

1、位置约束,这个和具体硬件相关,对照硬件PCB文件找到相应管脚即可,并添加IO的电平属性,也可通过ALLPORTS设置默认的电平。

LOCATE COMP "DDR_CLK_I" SITE "AD1" ;

IOBUF ALLPORTS IO_TYPE=LVCMOS33 ;

IOBUF PORT "CLK_27M_I" IO_TYPE=LVCMOS33 ;

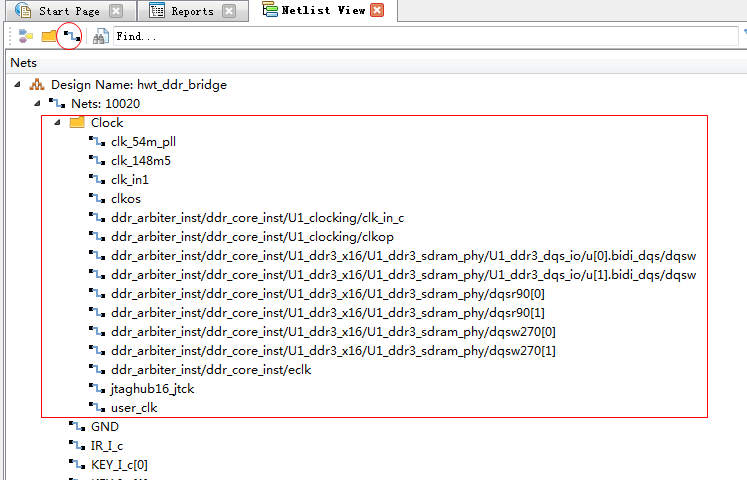

2、时钟约束,在【tool--netlist view】下边,点net图标,点开clock可看到整个项目里的时钟信号,然后逐一确认时钟频率并添加约束。

1 FREQUENCY NET "ddr_arbiter_inst/ddr_core_inst/U1_clocking/clk_in_c" 100.0 MHz PAR_ADJ 5.0 ;

2 FREQUENCY NET "user_clk" 200.0 MHz PAR_ADJ 40.0 ;

3 FREQUENCY NET "*/U1_clocking/clkop" 400.0 MHz PAR_ADJ 80.0 ;

3、DDR约束,直接参考IP例子ddr3_x16_eval.lpf抄过来就好(最多确认下那些信号是否都有效),通常在下边目录:xxx\coregen_hwt_bit_v901_nocdr_noddr\ddr3_x16\ddr_p_eval\ddr3_x16\impl\lse

4、不需要时序分析的路径。Xilinx的约束是TIG,Lattice就是BLOCK,免得后端工具把时间耗费在这些不需要时序分析的路径上。

BLOCK PATH FROM CLKNET "clk_54m_pll" TO CLKNET "clk_148m5" ;

BLOCK NET "video_rddr_scaler_inst/fifo_rst" ;

5、接口信号的上下拉设置,通常设置为NONE,对按键、IIC则设置为上拉PULLMODE=UP。

后端报告

后端跑完,关注的信息,包括:

- 运行时间,决定了迭代的周期多久,方便评估验证的效率。虽然报告没给出时间耗费,但有起始时间(下图synplify报告最前边几行)和最终产生bit的时间(看bit修改日期就知道),首尾做个减法就得到最终结果。

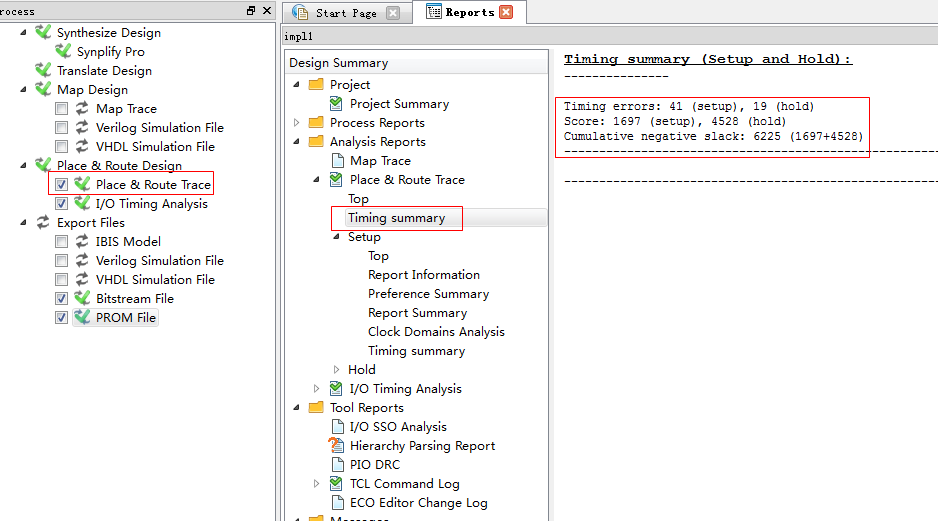

- 时序报告,score不能太高,具体得分需要逐条分析,从而评估bit的质量,或者是否适当提高时序约束频率,面积约束等策略。通过netlist的查看,检查时钟路径是否都覆盖,避免每次跑出版本的功能不具备一致性。

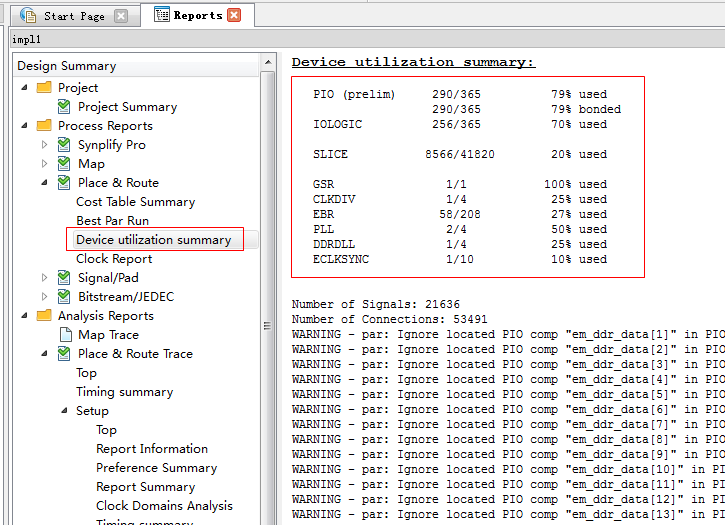

- 资源报告,评估后端风险,各个模块资源等

后记

先暂时列这些,想起了再补充。

=======================

by NicoWei

2019-3-8 23:00:48

=======================

【心得】Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)的更多相关文章

- mock server 前后端分离小结(转)

1.前台开发受限于后台开发的速度 2.后台提供给前台的接口缺字段,时常需要联调 基于Mock Server开发的好处: 对于前端来讲,可以独立于后端进行开发. 对于后端来讲,根据前端定义的接口进行开发 ...

- Git使用经验小结

2012春,开始正式使用SVN,2014年9月加入一起好后,开始使用Git. 有了一些使用经验,也看了下网上关于"Git全胜SVN"的言论. 结合自己的实际情况,简要写几句: 1 ...

- mybatis 使用经验小结

一.多数据源问题 主要思路是把dataSource.sqlSesstionFactory.MapperScannerConfigurer在配置中区分开,各Mapper对应的包名.类名区分开 <? ...

- jmeter linux使用经验小结

1. 确认务必安装了JDK,并且把路径配置OK.否则执行会报错. 2. 当做负载机时,在hosts 配置上 你的ip 你的hostname 或者使用./bin/jmeter-server ...

- Struts2 interceptor使用经验小结

1. interceptor 调用Spring容器中的bean 在interceptor中常有需要调用Spring Bean的需要,其实很简单和Struts2的Action一样配置即可. Spring ...

- DEV_TreeList使用经验小结

1. 点击叶子节点是希望Open键显示,点击非叶子节点时希望隐藏.实践中发现点击到了非叶子节点图标,Open没有隐藏,如何解决? 增加一个判断: if (_hitInfo.HitInfoType != ...

- 性能测试工具Loadrunner使用经验小结(原创更新版)

1. 引言 1.1. 简介 loadrunner是一种预测系统行为和性能的负载测试工具,它可以轻松创建虚拟用户.创建真实的负载.定位性能问题.重复测试保证系统的高性能 globa-100的注册码:AE ...

- Kafka使用经验小结

本文尽量从一个使用者的角度去记录一些在实战当中使用Kfaka所需要关注的要点,这样可能会贴切更多的读者,本文并不会介绍太多的Kafka的一些架构层次设计的知识,因为网上已经有一大堆的重复搬运的资料任由 ...

- mybatis 使用经验小结 good

一.多数据源问题 主要思路是把dataSource.sqlSesstionFactory(用来产生sqlSession).MapperScannerConfigurer在配置中区分开,各Mapper对 ...

随机推荐

- CVE-2019-0686|Microsoft Exchange特权提升漏洞补丁已发布

Microsoft Exchange Server中存在一个特权提升漏洞.成功利用此漏洞的攻击者可以获得与Exchange服务器的任何其他用户相同的权限.这可能允许攻击者执行诸如访问其他用户的邮箱之类 ...

- Intellij Idea 无法启动项目的配置坑

1. run/debug configuration里面,tomcat的deployment点击添加不能自动创建war-explorded包: 方案:删除project libraries,重新mav ...

- SQL中关于不能显示count为0的行的问题

今天在写自己一个博客项目时遇到了一个数据库问题,因为对于数据库自己所知道的还是很浅显的,对一些查询语句不怎么熟悉. 我目前有一个文章表和评论表,评论表里面有个post_id对应文章表里面的id,想查询 ...

- asp.net core导入excel

接昨天的导出 导入excel内容 对比昨天导出的内容增加了一行实体属性名称作为标题行,这样到转换为实体的时候才能找到对应的属性. 导入代码 public IActionResult InportExc ...

- 架构师入门:Spring Cloud系列,Hystrix与Eureka的整合

和Ribbon等组件一样,在项目中,Hystrix一般不会单独出现,而是会和Eureka等组件配套出现.在Hystrix和Eureka整合后的框架里,一般会用到Hystrix的断路器以及合并请求等特性 ...

- 『练手』001 Laura.SqlForever架构基础(Laura.XtraFramework 的变迁)

001 Laura.SqlForever架构的基础(Laura.XtraFramework 的变迁之路) Laura.XtraFramework 到底是 做什么的? Laura.XtraFramewo ...

- unity中ScriptableObject在assetbundle中的加载

转载请标明出处:http://www.cnblogs.com/zblade/ 以前都是写一些个人的调研博客,从今天开始,也写一些个人在开发中遇到的一些可以分享的趟坑博客,为后续的开发人员提供一些绵薄之 ...

- Fescar(Seata)-Springcloud流程分析-2阶段

上文我们分析了fescar的一阶段执行过程.在一阶段中,服务起始方发起全局事务并注册到TC.在调用协同服务时,协同服务的事务分支事务会先完成阶段一的事务提交或回滚,并生成事务回滚的undo_log日志 ...

- Linux framebuffer测试程序

Linux framebuffer的框架非常简单, 对于应用程序就是操作一块内存(俗称帧缓存), 当然也有可能是双缓存, 一般用于高帧率场景, 一块帧在填充数据时, 另一块在显示, 接着对调过来, 那 ...

- Linux用户和权限管理看了你就会用啦

前言 只有光头才能变强 回顾前面: 看完这篇Linux基本的操作就会了 没想到上一篇能在知乎获得千赞呀,Linux也快期末考试了,也有半个月没有写文章了.这篇主要将Linux下的用户和权限知识点再整理 ...